1.本发明是有关于一种存储器装置及其制造方法。

背景技术:

2.近年来,半导体装置的尺寸已逐渐缩小。在半导体技术中,特征尺寸的缩小、速度、效能、密度与每单位集成电路之成本的改良皆为相当重要的目标。在实际应用上,装置尺寸缩小的同时,仍须保持装置的电性以符合商业需求。

技术实现要素:

3.本发明系有关于一种存储器装置及其制造方法。

4.根据本发明的一方面,提出一种存储器装置,其包括一叠层体结构及一阶梯状结构。叠层体结构包括一第一子叠层体结构及一第二子叠层体结构。阶梯状结构电性连接至叠层体结构。阶梯状结构包括一第一子阶梯状结构及一第二子阶梯状结构。第一子阶梯状结构及第二子阶梯状结构各包括一第一阶梯状部与一第二阶梯状部。第一子叠层体结构与第二子叠层体结构分别连接至第一子阶梯状结构的第一阶梯状部与第二子阶梯状结构的第一阶梯状部。

5.根据本发明的另一方面,提出一种存储器装置的制造方法,其包括以下步骤。沿一垂直方向交错叠层多个导电层与多个绝缘层以形成一叠层结构。叠层结构包括配置在一第一方向上的一第一叠层部、一第二叠层部与另一第一叠层部。第一叠层部与另一第一叠层部分别在第二叠层部的相反侧上。第一叠层部与另一第一叠层部在一阶梯状接触区中。第二叠层部在一存储器阵列区中。利用多个光刻胶层对第一叠层部与另一第一叠层部进行刻蚀以形成一阶梯状结构。在阶梯状接触区中,光刻胶层在第一方向及/或一第二方向上的尺寸是彼此不同。第一方向、第二方向及垂直方向是互相垂直。存储器装置包括一叠层体结构及阶梯状结构。叠层体结构包括一第一子叠层体结构及一第二子叠层体结构。第一子叠层体结构及第二子叠层体结构包括第二叠层部。阶梯状结构电性连接至叠层体结构,并包括一第一子阶梯状结构及一第二子阶梯状结构。第一子阶梯状结构及第二子阶梯状结构各包括一第一阶梯状部与一第二阶梯状部。第一子叠层体结构与第二子叠层体结构分别连接至第一子阶梯状结构的第一阶梯状部与第二子阶梯状结构的第一阶梯状部。

6.为了对本发明的上述及其他方面有更好的了解,下文特举实施例,并配合所附附图详细说明如下:

附图说明

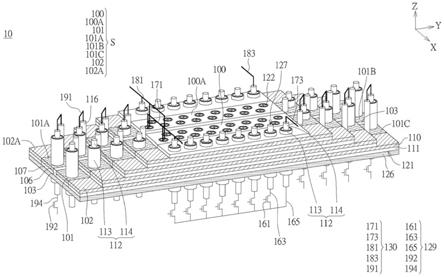

7.图1为根据一实施例的存储器装置的俯视示意图。

8.图2为根据另一实施例的存储器装置的俯视示意图。

9.图3a至图3t绘示一实施例的存储器装置的制造方法。

10.【符号说明】

11.1~96:导电阶梯层

12.100:叠层体结构

13.101:第一叠层体部

14.102:第二叠层体部

15.110:第一子叠层体结构

16.111:第一叠层体部

17.112:第二叠层体部

18.120:第二子叠层体结构

19.121:第一叠层体部

20.122:第二叠层体部

21.130:第三子叠层体结构

22.131:第一叠层体部

23.132:第二叠层体部

24.140:第四子叠层体结构

25.141:第一叠层体部

26.142:第二叠层体部

27.200:阶梯状结构

28.210:第一子阶梯状结构

29.211:第一阶梯状部

30.212:第二阶梯状部

31.220:第二子阶梯状结构

32.221:第一阶梯状部

33.222:第二阶梯状部

34.230:第三子阶梯状结构

35.231:第一阶梯状部

36.232:第二阶梯状部

37.240:第四子阶梯状结构

38.241:第一阶梯状部

39.242:第二阶梯状部

40.300:柱状元件

41.410,420:绝缘元件

42.500:介电元件

43.610,620,630,640:字线驱动器

44.700:叠层结构

45.701,701-1,701-2:第一叠层部

46.701g1~701g11:内叠层部

47.701k1~701k11:外叠层部

48.701p1~701p3,701q1~701q3:叠层部区

49.702:第二叠层部

50.707:导电层

51.708:绝缘层

52.7011:第一子叠层部

53.7012:第二子叠层部

54.c:阶梯状接触区

55.d1:第一方向

56.d2:第二方向

57.e,f:阶梯尺寸

58.h1,h2,t1,t11,t12,t21,t22:尺寸

59.m:存储器阵列区

60.pr1~,pr15:光刻胶层

61.z:垂直方向

具体实施方式

62.以下以一些实施例做说明。须注意的是,本发明并非显示出所有可能的实施例,未于本发明提出的其他实施例也可能可以应用。再者,图式上的尺寸比例并非按照实际产品等比例绘制。因此,说明书和图示内容仅作叙述实施例之用,而非作为限缩本发明保护范围之用。另外,实施例中的叙述,例如局部结构、工艺步骤和材料应用等等,仅为举例说明之用,并非对本发明欲保护的范围做限缩。实施例的步骤和结构各自细节可在不脱离本发明的精神和范围内根据实际应用工艺的需要而加以变化与修饰。以下是以相同/类似的符号表示相同/类似的元件做说明。

63.请参照图1,其为根据一实施例的存储器装置的俯视示意图。存储器装置包括叠层体结构100与阶梯状结构200。阶梯状结构200电性连接叠层体结构100。阶梯状结构200与叠层体结构100包括在垂直方向z上交错叠层的导电层与绝缘层。阶梯状结构200与叠层体结构100的导电层电性相连。垂直方向z、第一方向d1与第二方向d2可彼此垂直。

64.一实施例中,阶梯状结构200与叠层体结构100具有数量为96层的导电层。阶梯状结构200的导电层具有呈阶梯状配置的96阶层的导电阶梯层,如图1所示。阶梯状结构200的导电层包括阶层由下至上的第一阶层(底阶层)的导电阶梯层1、第二阶层的导电阶梯层2、第三阶层的导电阶梯层3

…

至第九十四阶层的导电阶梯层94、第九十五阶层的导电阶梯层95与第九十六阶层(顶阶层)的导电阶梯层96。阶梯状结构200具有96个阶梯单元,分别具有导电阶梯层1、导电阶梯层2、导电阶梯层3

…

至导电阶梯层94、导电阶梯层95与导电阶梯层96。阶梯单元具有在第一方向d1上的阶梯尺寸e,并具有在第二方向d2上的阶梯尺寸f。但本发明不限于此。

65.叠层体结构100可包括第一子叠层体结构110、第二子叠层体结构120、第三子叠层体结构130与第四子叠层体结构140。第一子叠层体结构110、第二子叠层体结构120、第三子叠层体结构130与第四子叠层体结构140在存储器阵列区m中。第一子叠层体结构110、第二子叠层体结构120、第三子叠层体结构130与第四子叠层体结构140可排列在第二方向d2上。此实施例中,第一子叠层体结构110、第二子叠层体结构120、第三子叠层体结构130与第四子叠层体结构140各自在第二方向d2上具有相同的尺寸t1。举例来说,子叠层体结构(例如

第一子叠层体结构110、第二子叠层体结构120、第三子叠层体结构130与第四子叠层体结构140)包括第一叠层体部101。亦即,第一子叠层体结构110包括第一叠层体部111。第二子叠层体结构120包括第一叠层体部121。第三子叠层体结构130包括第一叠层体部131。第四子叠层体结构140包括第一叠层体部141。第一叠层体部101(第一叠层体部111、第一叠层体部121、第一叠层体部131、第一叠层体部141)在第二方向d2上可具有一致的尺寸t1。

66.存储单元定义在第一子叠层体结构110、第二子叠层体结构120、第三子叠层体结构130与第四子叠层体结构140的第一叠层体部101中。举例来说,柱状元件300可形成在叠层体结构100中。柱状元件300在垂直方向z上延伸穿过叠层体结构100。一实施例中,柱状元件300包括通道柱。存储材料层配置在通道柱与导电层之间。nand闪存阵列的存储单元定义在通道柱与导电层交错处的存储材料层中。导电层用作字线。通道柱电性连接至位线。一实施例中,nand芯片可为捕捉层设计。一实施例中,nand芯片可为浮动栅设计。一实施例中,nand芯片可为阵列下电路设计。

67.阶梯状结构200可包括第一子阶梯状结构210、第二子阶梯状结构220、第三子阶梯状结构230及第四子阶梯状结构240。第一子阶梯状结构210、第二子阶梯状结构220、第三子阶梯状结构230及第四子阶梯状结构240在阶梯状接触区c中。第一子阶梯状结构210包括第一阶梯状部211与第二阶梯状部212。第一阶梯状部211的阶梯阶层(即第四十九阶层至第九十六阶层)高于第二阶梯状部212的阶梯阶层(即第一阶层至第四十八阶层)。第一子叠层体结构110连接至第一子阶梯状结构210的第一阶梯状部211。第一子阶梯状结构210的第一阶梯状部211电性连接在第一子阶梯状结构210的第二阶梯状部212与第一子叠层体结构110之间。

68.第二子阶梯状结构220包括第一阶梯状部221与第二阶梯状部222。第一阶梯状部221的阶梯阶层(即第四十九阶层至第九十六阶层)高于第二阶梯状部222的阶梯阶层(即第一阶层至第四十八阶层)。第二子叠层体结构120连接至第二子阶梯状结构220的第一阶梯状部221。第二子阶梯状结构220的第一阶梯状部221电性连接在第二子阶梯状结构220的第二阶梯状部222与第二子叠层体结构120之间。

69.第一子叠层体结构110在第一子阶梯状结构210的第一阶梯状部211与第二子阶梯状结构220的第二阶梯状部222之间。第二子叠层体结构120在第一子阶梯状结构210的第二阶梯状部212与第二子阶梯状结构220的第一阶梯状部221之间。第一子阶梯状结构210在第二方向d2上的尺寸h1可大于第一子叠层体结构110的尺寸t1。例如,尺寸h1可约为尺寸t1的两倍。

70.第三子叠层体结构130、第四子叠层体结构140、第三子阶梯状结构230与第四子阶梯状结构240之间的关系类似第一子叠层体结构110、第二子叠层体结构120、第一子阶梯状结构210与第二子阶梯状结构220之间的关系。举例来说,第三子阶梯状结构230可包括第一阶梯状部231与第二阶梯状部232。第四子阶梯状结构240可包括第一阶梯状部241与第二阶梯状部242。第三子叠层体结构130连接至第三子阶梯状结构230的第一阶梯状部231。第四子叠层体结构140连接至第四子阶梯状结构240的第一阶梯状部241。可以此类推其它结构特征。

71.第一子叠层体结构110与第一子阶梯状结构210的导电层可通过绝缘元件410电性绝缘第二子叠层体结构120与第二子阶梯状结构220的导电层。绝缘元件410在第一子叠层

体结构110与第二子阶梯状结构220的第二阶梯状部222之间,在第一子叠层体结构110与第二子叠层体结构120之间,并在第二子叠层体结构120与第一子阶梯状结构210的第二阶梯状部212之间。可以此类推绝缘元件420相对于第三子叠层体结构130、第四子叠层体结构140、第三子阶梯状结构230与第四子阶梯状结构240之间的关系。绝缘元件410与绝缘元件420可具有形状。

72.第一子阶梯状结构210、第二子叠层体结构120与第二子阶梯状结构220的导电层可通过介电元件500电性绝缘第三子阶梯状结构230、第三子叠层体结构130与第四子阶梯状结构240的导电层。介电元件500可在第一子阶梯状结构210的第二阶梯状部212与第三子阶梯状结构230的第一阶梯状部231之间,在绝缘元件410与第三子叠层体结构130之间,在第二子叠层体结构120与第三子叠层体结构130之间,在第二子叠层体结构120与绝缘元件420之间,并在第二子阶梯状结构220的第一阶梯状部221与第四子阶梯状结构240的第二阶梯状部242之间。

73.第一子叠层体结构110与第一子阶梯状结构210的导电层(字线)可经过由第一子阶梯状结构210的导电阶梯层1~96及其上的导电插塞(未显示)电性连接至字线驱动器610。第二子叠层体结构120与第二子阶梯状结构220的导电层(字线)可经过由第二子阶梯状结构220的导电阶梯层1~96及其上的导电插塞(未显示)电性连接至字线驱动器620。第三子叠层体结构130与第三子阶梯状结构230的导电层(字线)可经过由第三子阶梯状结构230的导电阶梯层1~96及其上的导电插塞(未显示)电性连接至字线驱动器630。第四子叠层体结构140与第四子阶梯状结构240的导电层(字线)可经过由第四子阶梯状结构240的导电阶梯层1~96及其上的导电插塞(未显示)电性连接至字线驱动器640。也就是说,第一子阶梯状结构210、第二子阶梯状结构220、第三子阶梯状结构230与第四子阶梯状结构240可称作有效的(effective)阶梯状结构。实施例中,并没有虚置(dummy)阶梯状结构(其导电层为电性浮接)设置在第一子阶梯状结构210与第三子阶梯状结构230之间,也没有虚置阶梯状结构设置在第二子阶梯状结构220与第四子阶梯状结构240之间。因此能够提升晶圆上有效存储器装置的密度。定义在各第一子叠层体结构110、第二子叠层体结构120、第三子叠层体结构130与第四子叠层体结构140中的一个区块(one block)的存储单元可由对应的字线驱动器610、字线驱动器620、字线驱动器630或字线驱动器640其中之一选择或控制,或同时进行擦除。

74.请参照图2,其为根据另一实施例的存储器装置的俯视示意图。图2的存储器装置与图1的存储器装置之间的差异说明如下。第一子叠层体结构110、第二子叠层体结构120、第三子叠层体结构130与第四子叠层体结构140各还包括第二叠层体部102连接第一叠层体部101。第一子叠层体结构110的第一叠层体部111与第二叠层体部112相连接。第二子叠层体结构120的第一叠层体部121与第二叠层体部122相连接。第三子叠层体结构130的第一叠层体部131与第二叠层体部132相连接。第四子叠层体结构140的第一叠层体部141与第二叠层体部142相连接。

75.举例来说,第一子叠层体结构110的第二叠层体部112是在第二子叠层体结构120的第一叠层体部121与第一子阶梯状结构210的第二阶梯状部212之间。第二子叠层体结构120的第二叠层体部122是在第一子叠层体结构110的第一叠层体部111与第二子阶梯状结构220的第二阶梯状部222之间。第一子叠层体结构110的第二叠层体部112连接至第一子阶

梯状结构210的第二阶梯状部212,因此能提供至第一子阶梯状结构210更短的电连接路径且降低电阻。第二子叠层体结构120的第二叠层体部122连接至第二子阶梯状结构220的第二阶梯状部222,因此能提供至第二子阶梯状结构220更短的电连接路径且降低电阻。第三子叠层体结构130、第四子叠层体结构140、第三子阶梯状结构230与第四子阶梯状结构240之间的关系类似第一子叠层体结构110、第二子叠层体结构120、第一子阶梯状结构210与第二子阶梯状结构220之间的关系。因此可类推第三子叠层体结构130的第二叠层体部132及第四子叠层体结构140的第二叠层体部142的其它结构特征及其与其它元件之间的关系。

76.第一子叠层体结构110、第二子叠层体结构120、第三子叠层体结构130与第四子叠层体结构140各自在第二方向d2上具有不同的尺寸。举例来说,第一子叠层体结构110、第二子叠层体结构120、第三子叠层体结构130与第四子叠层体结构140独立具有l形状。第一子叠层体结构110远离第一子阶梯状结构210的部分在第二方向d2上的尺寸t11(等于第一叠层体部111在第二方向d2上的尺寸t1)是小于靠近第一子阶梯状结构210的部分在第二方向d2上的尺寸t12(即第一叠层体部111在第二方向d2上的尺寸t1与第二叠层体部112在第二方向d2上的尺寸的总和)。第一子阶梯状结构210在第二方向d2上的尺寸h1可小于第一子叠层体结构110远离第一子阶梯状结构210的部分在第二方向d2上的尺寸t11。例如,尺寸h1可约为尺寸t11的两倍。第一子阶梯状结构210的尺寸h1可等于第一子叠层体结构110靠近第一子阶梯状结构210的部分在第二方向d2上的尺寸t12。类似以上,第二子叠层体结构120远离第二子阶梯状结构220的部分在第二方向d2上的尺寸t21(等于第一叠层体部121在第二方向d2上的尺寸t1)是小于靠近第二子阶梯状结构220的部分在第二方向d2上的尺寸t22(即第一叠层体部121在第二方向d2上的尺寸t1与第二叠层体部122在第二方向d2上的尺寸的总和)。第二子阶梯状结构220在第二方向d2上的尺寸h2可大于第二子叠层体结构120远离第二子阶梯状结构220的部分在第二方向d2上的尺寸t21。例如,尺寸h2可约为尺寸t21的两倍。第二子阶梯状结构220的尺寸h2可等于第二子叠层体结构120靠近第二子阶梯状结构220的部分在第二方向d2上的尺寸t22。可以此类推第三子叠层体结构130与第四子叠层体结构140的尺寸特征。

77.此实施例中,第一子阶梯状结构210的第一阶梯状部211的阶梯阶层(即第四十九阶层至第九十六阶层)是高于第二阶梯状部212的阶梯阶层(即第一阶层至第四十八阶层)。第二子阶梯状结构220的第一阶梯状部221的阶梯阶层(即第一阶层至第四十八阶层)是低于第二阶梯状部222的阶梯阶层(即第四十九阶层至第九十六阶层)。第三子阶梯状结构230的第一阶梯状部231的阶梯阶层(即第四十九阶层至第九十六阶层)是高于第二阶梯状部232的阶梯阶层(即第一阶层至第四十八阶层)。第四子阶梯状结构240的第一阶梯状部241的阶梯阶层(即第一阶层至第四十八阶层)是低于第二阶梯状部242的阶梯阶层(即第四十九阶层至第九十六阶层)。但本发明不限于此。阶梯阶层的数量及配置可视实际工艺或产品实际需求做调变。

78.绝缘元件410在第一子叠层体结构110的第一叠层体部111与第二子叠层体结构120的第二叠层体部122之间,在第一子叠层体结构110的第一叠层体部111与第二子叠层体结构120的第一叠层体部121之间,并在第一子叠层体结构110的第二叠层体部112与第二子叠层体结构120的第一叠层体部121之间。可以此类推绝缘元件420与第三子叠层体结构130及第四子叠层体结构140之间的关系。

79.第一子阶梯状结构210、第一子叠层体结构110、第二子叠层体结构120与第二子阶梯状结构220的导电层可通过介电元件500电性绝缘第三子阶梯状结构230、第三子叠层体结构130、第四子叠层体结构140与第四子阶梯状结构240的导电层。介电元件500可在第一子阶梯状结构210的第二阶梯状部212与第三子阶梯状结构230的第一阶梯状部231之间,在第一子叠层体结构110的第二叠层体部112与第三子叠层体结构130的第一叠层体部131之间,在绝缘元件410与第三子叠层体结构130的第一叠层体部131之间,在第二子叠层体结构120的第一叠层体部121与第三子叠层体结构130的第一叠层体部131之间,在第二子叠层体结构120的第一叠层体部121与绝缘元件420之间,在第二子叠层体结构120的第一叠层体部121与第四子叠层体结构140的第二叠层体部142之间,并在第二子阶梯状结构220的第一阶梯状部221与第四子阶梯状结构240的第二阶梯状部242之间。

80.图3a至图3t绘示一实施例之存储器装置的制造方法,其包括对叠层结构700进行利用不同分布之光刻胶层的多个黄光光刻刻蚀工艺,从而形成阶梯状结构的制造步骤。

81.请参照图3a。可在一基底(未显示)上沿垂直方向z交错叠层导电层707与绝缘层708以形成叠层结构700。此实施例中,叠层结构700可包括数量为96层的导电层707,通过绝缘层708相互绝缘。叠层结构700包括排列在第一方向d1上的第一叠层部701与第二叠层部702。第一叠层部701包括第一叠层部701-1与第一叠层部701-2,分别在第二叠层部702的相反侧上。第一叠层部701-1与第一叠层部701-2在阶梯状接触区c中。第二叠层部702在存储器阵列区m中。第二叠层部702可为叠层体结构100。一实施例中,可形成光刻胶层(未显示)覆盖在第二叠层部702的绝缘层708(例如顶绝缘层)上,并以此光刻胶层(未显示)作为刻蚀掩模进行刻蚀步骤,以移除露出的第一叠层部701的绝缘层708(例如顶绝缘层),从而露出第一叠层部701的第九十六阶层的导电层707(例如导电阶梯层96)。然后可移除光刻胶层。

82.请参照图3b。形成光刻胶层pr1在叠层结构700上。光刻胶层pr1覆盖第二叠层部702与第一叠层部701(包括第一叠层部701-1与第一叠层部701-2)的第一子叠层部7011,并露出第一叠层部701的第二子叠层部7012的第九十六阶层的导电层(即导电阶梯层96)。以光刻胶层pr1作为刻蚀掩模,从第二子叠层部7012的第九十六阶层的导电层(即导电阶梯层96)向下刻蚀第二子叠层部7012的48阶层,以露出第四十八阶层的导电层(即导电阶梯层48)。然后可移除光刻胶层pr1。如此,形成了如图3c所示的半导体结构。

83.请参照图3d,形成光刻胶层pr2在叠层结构700上。光刻胶层pr2覆盖第二叠层部702,并在第一方向d1上延伸而覆盖在部分的第一叠层部701上。亦即,光刻胶层pr2覆盖第一叠层部701较靠近第二叠层部702的内叠层部701g1,并露出较远离第二叠层部702的外叠层部701k1。以光刻胶层pr2作为刻蚀掩模,从露出的外叠层部701k1的第九十六阶层的导电层(即导电阶梯层96)与第四十八阶层的导电层(即导电阶梯层48)向下刻蚀4阶层,以分别露出第九十二阶层的导电层(即导电阶梯层92)与第四十四阶层的导电层(即导电阶梯层44)。然后可削减光刻胶层pr2(先前光刻胶层)在第一方向d1上的阶梯尺寸e以形成图3e所示的光刻胶层pr3(后续光刻胶层)。可不削减光刻胶层pr2在第二方向d2上的尺寸,因此光刻胶层pr3在第二方向d2的尺寸是相同于光刻胶层pr2在第二方向d2的尺寸。

84.请参照图3e,光刻胶层pr3在叠层结构700上。光刻胶层pr3覆盖第二叠层部702与第一叠层部701的内叠层部701g2,并露出第一叠层部701的外叠层部701k2。以光刻胶层pr3作为刻蚀掩模,从露出的外叠层部701k2的导电层(即导电阶梯层96、导电阶梯层92、导电阶

梯层48与导电阶梯层44)向下刻蚀4阶层。如此,可形成如图3f所示的半导体结构。然后可削减光刻胶层pr3(先前光刻胶层)在第一方向d1上的阶梯尺寸e以形成图3g所示的光刻胶层pr4(后续光刻胶层)。可不削减光刻胶层pr3在第二方向d2上的尺寸,因此光刻胶层pr4在第二方向d2的尺寸是相同于光刻胶层pr3在第二方向d2的尺寸。

85.请参照图3g,光刻胶层pr4在叠层结构700上。光刻胶层pr4覆盖第二叠层部702与第一叠层部701的内叠层部701g3,并露出第一叠层部701的外叠层部701k3。以光刻胶层pr4作为刻蚀掩模,从露出的外叠层部701k3的导电层(例如图3f所示的导电阶梯层96、92、88、48、44、40)向下刻蚀4阶层,以形成如图3g所示之外叠层部701k3的导电阶梯层92、88、84、44、40、36。然后可削减光刻胶层pr4(先前光刻胶层)在第一方向d1上的阶梯尺寸e以形成图3h所示的光刻胶层pr5(后续光刻胶层)。可不削减光刻胶层pr4在第二方向d2上的尺寸,因此光刻胶层pr5在第二方向d2的尺寸是相同于光刻胶层pr4在第二方向d2的尺寸。

86.请参照图3h,光刻胶层pr5在叠层结构700上。光刻胶层pr5覆盖第二叠层部702与第一叠层部701的内叠层部701g4,并露出第一叠层部701的外叠层部701k4。以光刻胶层pr5作为刻蚀掩模,从露出的外叠层部701k4的导电层(即导电阶梯层96、92、88、84、48、44、40、36)向下刻蚀4阶层,以形成如图3h所示之外叠层部701k4的导电阶梯层92、88、84、80、44、40、36、32。然后可削减光刻胶层pr5(先前光刻胶层)在第一方向d1上的阶梯尺寸e以形成图3i所示的光刻胶层pr6(后续光刻胶层)。可不削减光刻胶层pr5在第二方向d2上的尺寸,因此光刻胶层pr6在第二方向d2的尺寸是相同于光刻胶层pr5在第二方向d2的尺寸。

87.请参照图3i,光刻胶层pr6在叠层结构700上。光刻胶层pr6覆盖第二叠层部702与第一叠层部701的内叠层部701g5,并露出第一叠层部701的外叠层部701k5。以光刻胶层pr6作为刻蚀掩模,从露出的导电层(即导电阶梯层96、92、88、84、80、48、44、40、36、32)向下刻蚀4阶层,以形成如图3i所示之外叠层部701k5的导电阶梯层92、88、84、80、76、44、40、36、32、28。然后可削减光刻胶层pr6(先前光刻胶层)在第一方向d1上的阶梯尺寸e以形成图3j所示的光刻胶层pr7(后续光刻胶层)。可不削减光刻胶层pr6在第二方向d2上的尺寸,因此光刻胶层pr7在第二方向d2的尺寸是相同于光刻胶层pr6在第二方向d2的尺寸。

88.请参照图3j,光刻胶层pr7在叠层结构700上。光刻胶层pr7覆盖第二叠层部702与第一叠层部701的内叠层部701g6,并露出第一叠层部701的外叠层部701k6。以光刻胶层pr7作为刻蚀掩模,从露出的外叠层部701k6的导电层(即导电阶梯层92、88、84、80、76、44、40、36、32、28)向下刻蚀4阶层,以形成如图3j所示之外叠层部701k6的导电阶梯层92、88、84、80、76、72、44、40、36、32、28、24。然后可削减光刻胶层pr7(先前光刻胶层)在第一方向d1上的阶梯尺寸e以形成图3k所示的光刻胶层pr8(后续光刻胶层)。可不削减光刻胶层pr7在第二方向d2上的尺寸,因此光刻胶层pr8在第二方向d2的尺寸是相同于光刻胶层pr7在第二方向d2的尺寸。

89.请参照图3k,光刻胶层pr8在叠层结构700上。光刻胶层pr8覆盖第二叠层部702与第一叠层部701的内叠层部701g7,并露出第一叠层部701的外叠层部701k7。以光刻胶层pr8作为刻蚀掩模,从露出的外叠层部701k7的导电层(即导电阶梯层92、88、84、80、76、72、44、40、36、32、28、24)向下刻蚀4阶层,以形成如图3k所示之外叠层部701k7的导电阶梯层92、88、84、80、76、72、68、44、40、36、32、28、24、20。然后可削减光刻胶层pr8(先前光刻胶层)在第一方向d1上的阶梯尺寸e以形成图3l所示的光刻胶层pr9(后续光刻胶层)。可不削减光刻

胶层pr8在第二方向d2上的尺寸,因此光刻胶层pr9在第二方向d2的尺寸是相同于光刻胶层pr8在第二方向d2的尺寸。

90.请参照图3l,光刻胶层pr9在叠层结构700上。光刻胶层pr9覆盖第二叠层部702与第一叠层部701的内叠层部701g8,并露出第一叠层部701的外叠层部701k8。以光刻胶层pr9作为刻蚀掩模,从露出的外叠层部701k8的导电层(即导电阶梯层92、88、84、80、76、72、68、44、40、36、32、28、24、20)向下刻蚀4阶层,以形成如图3l所示之外叠层部701k8的导电阶梯层92、88、84、80、76、72、68、64、44、40、36、32、28、24、20、16。然后可削减光刻胶层pr9(先前光刻胶层)在第一方向d1上的阶梯尺寸e以形成图3m所示的光刻胶层pr10(后续光刻胶层)。可不削减光刻胶层pr9在第二方向d2上的尺寸,因此光刻胶层pr10在第二方向d2的尺寸是相同于光刻胶层pr9在第二方向d2的尺寸。

91.请参照图3m,光刻胶层pr10在叠层结构700上。光刻胶层pr10覆盖第二叠层部702与第一叠层部701的内叠层部701g9,并露出第一叠层部701的外叠层部701k9。以光刻胶层pr10作为刻蚀掩模,从露出的外叠层部701k9的导电层(即导电阶梯层92、88、84、80、76、72、68、64、44、40、36、32、28、24、20、16)向下刻蚀4阶层,以形成如图3m所示之外叠层部701k9的导电阶梯层92、88、84、80、76、72、68、64、60、44、40、36、32、28、24、20、16、12。然后可削减光刻胶层pr10(先前光刻胶层)在第一方向d1上的阶梯尺寸e以形成图3n所示的光刻胶层pr11(后续光刻胶层)。可不削减光刻胶层pr10在第二方向d2上的尺寸,因此光刻胶层pr11在第二方向d2的尺寸是相同于光刻胶层pr10在第二方向d2的尺寸。

92.请参照图3n,光刻胶层pr11在叠层结构700上。光刻胶层pr11覆盖第二叠层部702与第一叠层部701的内叠层部701g10,并露出第一叠层部701的外叠层部701k10。以光刻胶层pr11作为刻蚀掩模,从露出的外叠层部701k10的导电层(即导电阶梯层92、88、84、80、76、72、68、64、60、44、40、36、32、28、24、20、16、12)向下刻蚀4阶层,以形成如图3n所示之外叠层部701k10的导电阶梯层92、88、84、80、76、72、68、64、60、56、44、40、36、32、28、24、20、16、12、8。然后可削减光刻胶层pr11(先前光刻胶层)在第一方向d1上的阶梯尺寸e以形成图3o所示的光刻胶层pr12(后续光刻胶层)。可不削减光刻胶层pr11在第二方向d2上的尺寸,因此光刻胶层pr12在第二方向d2的尺寸是相同于光刻胶层pr11在第二方向d2的尺寸。

93.请参照图3o,光刻胶层pr12在叠层结构700上。光刻胶层pr12覆盖第二叠层部702与第一叠层部701的内叠层部701g11,并露出第一叠层部701的外叠层部701k11。以光刻胶层pr12作为刻蚀掩模,从露出的外叠层部701k11的导电层(即导电阶梯层92、88、84、80、76、72、68、64、60、56、44、40、36、32、28、24、20、16、12、8)向下刻蚀4阶层,以形成如图3o所示之外叠层部701k11的导电阶梯层92、88、84、80、76、72、68、64、60、56、52、44、40、36、32、28、24、20、16、12、8、4。然后可移除光刻胶层pr12。从而,可形成如图3p所示的半导体结构。

94.请参照图3q,形成光刻胶层pr13在叠层结构700上。光刻胶层pr13覆盖第二叠层部702,并在第一方向d1上延伸而覆盖在部分的第一叠层部701上。亦即,光刻胶层pr13覆盖第一叠层部701的第一子叠层部7011与第二子叠层部7012的叠层部区701p1,并露出第一子叠层部7011与第二子叠层部7012的叠层部区701q1。以光刻胶层pr13作为刻蚀掩模,从露出的导电层向下刻蚀1阶层,以形成如图3q所示之叠层部区701q1所具有的导电阶梯层配置。然后可削减光刻胶层pr13(先前光刻胶层)在第二方向d1上的阶梯尺寸f以形成图3r所示的光刻胶层pr14(后续光刻胶层)。可不削减光刻胶层pr13在第一方向d1上的尺寸,因此光刻胶

层pr14在第一方向d1的尺寸是相同于光刻胶层pr13在第一方向d1的尺寸。

95.请参照图3r,形成光刻胶层pr14在叠层结构700上。光刻胶层pr14覆盖第二叠层部702与第一叠层部701之第一子叠层部7011与第二子叠层部7012的叠层部区701p2,并露出叠层部区701q2。以光刻胶层pr14作为刻蚀掩模,从露出的导电层向下刻蚀1阶层,以形成如图3r所示之叠层部区701q2所具有的导电阶梯层配置。然后可削减光刻胶层pr14(先前光刻胶层)在第二方向d1上的阶梯尺寸f以形成图3s所示的光刻胶层pr15(后续光刻胶层)。可不削减光刻胶层pr14在第一方向d1上的尺寸,因此光刻胶层pr15在第一方向d1的尺寸是相同于光刻胶层pr14在第一方向d1的尺寸。

96.请参照图3s,形成光刻胶层pr15在叠层结构700上。光刻胶层pr15覆盖第二叠层部702与第一叠层部701之第一子叠层部7011与第二子叠层部7012的叠层部区701p3,并露出叠层部区701q3。以光刻胶层pr15作为刻蚀掩模,从露出的导电层向下刻蚀1阶层,以形成如图3s所示之叠层部区701q3所具有的导电阶梯层配置。然后可移除光刻胶层pr15。从而,可形成如图3t所示的半导体结构,其包括类似参照图1所述的叠层体结构100与阶梯状结构200。

97.根据上述制造方法,是利用不同分布之光刻胶层作为刻蚀掩模刻蚀第一叠层部701从而形成阶梯状结构200。举例来说,在阶梯状接触区c中,光刻胶层在第一方向d1及/或第二方向d2上的尺寸是彼此不同。图3b的光刻胶层pr1、图3q的光刻胶层pr13、图3r的光刻胶层pr14与图3s的光刻胶层pr15其在阶梯状接触区c中的光刻胶部分是在第一方向d1上具有相同的尺寸,而在第二方向d2上具有不同的尺寸。图3d的光刻胶层pr2、图3e与图3f的光刻胶层pr3、图3g的光刻胶层pr4、图3h的光刻胶层pr5、图3i的光刻胶层pr6、图3j的光刻胶层pr7、图3k的光刻胶层pr8、图3l的光刻胶层pr9、图3m的光刻胶层pr10、图3n的光刻胶层pr11与图3o的光刻胶层pr12其在阶梯状接触区c中的光刻胶部分是在第二方向d2上具有相同的尺寸,而在第一方向d1上具有不同的尺寸。亦可参照图式理解所谓不同分布的光刻胶层其它可能的解读。

98.本发明并不限于上述制造方法。例如,可视实际工艺经验,使用其它种类的光刻胶层配置、刻蚀顺序等工艺参数。

99.以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。