半导体装置、存储设备、及晶体管的制造方法

1.[相关申请]

[0002]

本技术享有以日本专利申请2020-157386号(申请日期:2020年9月18日)为基础申请的优先权。本技术通过参照该基础申请而包含基础申请的全部内容。

技术领域

[0003]

本发明涉及一种半导体装置、存储设备、及晶体管的制造方法。

背景技术:

[0004]

为了将半导体存储设备高集成化,已提出一种将存储单元三维堆叠的三维积层型非易失性存储设备。三维积层型非易失性存储设备例如具有存储单元阵列与成为存储单元的控制电路的周边电路积层的结构。周边电路使用的是cmos(complementary metal oxide semiconductor,互补金氧半导体)等。cmos中使用的晶体管会因其制造步骤等而发生特性的劣化。

技术实现要素:

[0005]

本发明的实施方式提供一种能够使特性稳定提高的半导体装置、存储设备、及晶体管的制造方法。

[0006]

实施方式的半导体装置具备衬底、衬底上的栅极绝缘膜、积层半导体层、及积层半导体层上或积层半导体层的上方的金属层。积层半导体层具有:第1层,形成在栅极绝缘层上,并且包含掺杂有磷的多晶半导体;第2层,形成在第1层上,并且包含掺杂有碳的多晶半导体;及第3层,形成在第2层上,并且包含掺杂有磷或未掺杂磷的多晶半导体。第3层的磷含量少于第1层的磷含量,或第3层不含磷。

附图说明

[0007]

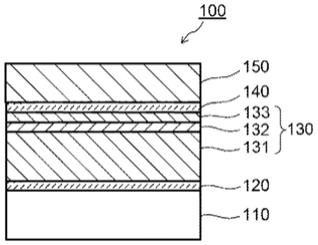

图1是表示实施方式的半导体装置中的栅极电极的剖视图。

[0008]

图2是表示图1所示的栅极电极的变化例的剖视图。

[0009]

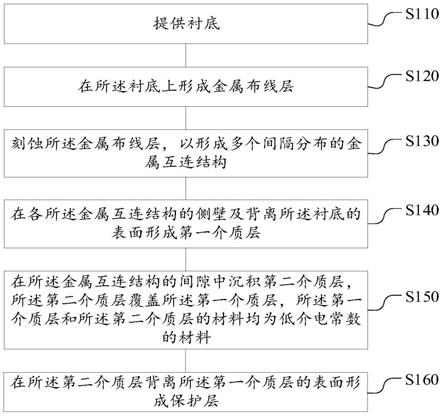

图3(a)~(f)是表示图1所示的栅极电极的制造步骤的图。

[0010]

图4是表示作为实施方式的半导体装置的cmosfet(complementary metal oxide semiconductor field effect transistor,互补金氧半导体场效电晶体)的剖视图。

[0011]

图5(a)~图7(o)是表示图4所示的cmosfet的制造步骤的图。

[0012]

图8是表示实施方式的半导体存储装置的构成的框图。

[0013]

图9是表示图8所示的半导体存储装置的存储单元阵列的电路构成的电路图。

[0014]

图10是表示实施方式的半导体存储装置的剖视图。

具体实施方式

[0015]

下面,参照附图,对实施方式的半导体装置及半导体存储装置进行说明。此外,在

各实施方式中,存在对实质上相同的构成部位标注相同的符号并将相关说明部分省略的情况。附图是示意性的,厚度与平面尺寸的关系、各部分的厚度比例等有时会与实际情况不同。

[0016]

(第1实施方式/栅极电极)

[0017]

图1是表示实施方式的半导体装置中的栅极电极的结构的剖视图。图1所示的栅极电极100设置在栅极绝缘层120上,该栅极绝缘层120形成在半导体衬底110的一面上。作为半导体衬底110,例如可以使用硅衬底。栅极绝缘层120例如可以使用氧化硅(sio)。栅极电极100具备3层结构的积层半导体层130、金属层150,且根据需要而具备tsi(through silicon oxide insertion,穿通氧化硅插入)层140。

[0018]

在栅极绝缘层120之上形成有3层结构的积层半导体层130。积层半导体层130从靠近栅极绝缘层120的一侧起依次具有:第1层131,包含掺杂有磷(p)的多晶半导体;第2层132,包含掺杂有碳(c)的多晶半导体;及第3层133,包含掺杂有p或未掺杂p的多晶半导体。作为积层半导体层130的第1层131、第2层132、第3层133中的多晶半导体,例如可以使用多晶硅。

[0019]

第2层132中所掺杂的c具有捕捉p来抑制彼此扩散的作用。然而,如下述制造步骤(图2)所示,会形成氧化膜160来抑制蚀刻残留,如果在第2层132的正上方形成氧化膜160,那么氧化膜160将变得难以剥离。因此,要在第2层132之上插置第3层133,以促进氧化膜160的剥离。

[0020]

第3层133具有抑制积层半导体层130与下述金属层150的界面电阻上升的作用。然而,如果第3层133中的p掺杂量过多,那么将促进作为下述氧化层的tsi层140加速氧化。因此,第3层133的p掺杂量要设定得比第1层131的p掺杂量少。也就是说,第3层133的磷含量要少于第1层131的磷含量。

[0021]

在积层半导体层130的第3层133之上,根据需要而形成有tsi层140。tsi层140具有防止杂质向下述金属层150扩散的作用。tsi层140例如可以使用氧化硅(sio)。不过,根据金属层150的构成材料,如图2所示,也可以省略tsi层140,而在积层半导体层130上直接设置金属层150。

[0022]

在tsi层140上形成有金属层150。作为金属层150,例如可以使用从靠近tsi层140的一侧起依次积层有硅化钨(wsi)/氮化钛(tin)、或钛(ti)/氮化钛(tin)/钨(w)的积层体。

[0023]

如果金属层150为wsi/tin,那么存在杂质向界面的wsi中扩散的风险。因此,倾向于插置tsi层140。不过,在金属层150为ti/tin/w的情况下,界面并不存在w,因此也就无需tsi层140。图2所示的栅极电极100例如具有ti/tin/w的积层膜来作为金属层150,从而省略了tsi层140的形成。

[0024]

所述栅极电极100例如是按以下所述而制造的。按照图3来说明栅极电极100的制造步骤。如图3(a)所示,准备半导体衬底110。如图3(b)所示,在半导体衬底110的一面上成膜出栅极绝缘层120。

[0025]

继而,如图3(c)所示,在栅极绝缘层120之上依次成膜出第1层131、第2层132、第3层133,从而形成积层半导体层130。如图3(d)所示,在第3层133之上成膜出氧化膜160。氧化膜160例如可以使用氧化硅(sio)。

[0026]

接着,成膜出氧化膜160后,如图3(e)所示,将第3层133的上层部分133a连同氧化

膜160一起去除。作为去除方法,可以使用机械蚀刻(cmp)或化学蚀刻。化学蚀刻例如可以使用cde(chemical dry etching,化学干式蚀刻)、rie(reactive ion etching,反应性离子蚀刻)或湿式蚀刻。另外,也可以将这些去除方法中的多种去除方法组合起来使用。

[0027]

接着,如图3(f)所示,在第3层133之上成膜出tsi层140,再在tsi层140之上成膜出金属层150,从而获得图1所示的栅极电极100。图2所示的栅极电极100是通过在第3层133上直接成膜出金属层150而获得的。

[0028]

(第2实施方式/半导体装置)

[0029]

作为第2实施方式的半导体装置例如为cmosfet。图4是表示第2实施方式的一例的剖视图。图4所示的cmosfet具有n通道mosfet(下文有时简称“nmos晶体管(trn)”)与p通道mosfet(下文有时简称“pmos晶体管(trp)”)。此外,将图4中的x方向设为栅极宽度方向,将y方向设为栅极长度方向,将z方向设为与x方向及y方向交叉的方向来进行说明。

[0030]

在半导体衬底110的表面附近,形成有p型井区域pw、n型井区域nw、及用来将n型井区域nw与p型井区域pw电分离的元件分离区域sti。元件分离区域sti例如可以使用氧化硅(sio)。

[0031]

在p型井区域pw设置有nmos(n-channel metal oxide semiconductor,n通道金氧半导体)晶体管trn,在n型井区域nw设置有pmos(p-channel metal oxide semiconductor,p通道金氧半导体)晶体管trp。

[0032]

作为nmos晶体管trn的栅极电极gcn,可以使用所述栅极电极100。金属层150的上表面被绝缘层55覆盖。金属层150的侧面被绝缘层56n覆盖。绝缘层56n作为nmos晶体管trn的栅极电极100的侧壁发挥作用。绝缘层55一部分开口,栅极电极100经由绝缘层55的开口连接于接触插塞c0。

[0033]

另外,在p型井区域pw设置有n

杂质扩散区域np1及np2,它们例如掺杂有磷(p)。n

杂质扩散区域np1与n

杂质扩散区域np2沿y方向隔开配置。n

杂质扩散区域np1及np2作为nmos晶体管trn的源极(源极扩散层)及漏极(漏极扩散层)发挥作用。n

杂质扩散区域np1及np2分别连接于接触插塞cs。

[0034]

接触插塞cs、c0具有形成在接触孔的底面及侧面的导电层58、及与导电层58相接地埋入接触孔内的导电层59。导电层58作为障壁金属发挥作用,可以使用钛(ti)与氮化钛(tin)的积层结构。导电层59例如可以使用钨(w)。

[0035]

而pmos晶体管trp并不特别限定,可以采用一般结构。例如,在n型井区域nw的表面附近,沿y方向隔开设置有p

杂质扩散区域pp1及pp2,在它们之间的区域设置有栅极电极gcp的栅极绝缘层120p。p

杂质扩散区域pp1及pp2例如掺杂有硼(b)。p

杂质扩散区域pp1及pp2作为pmos晶体管trp的源极(源极扩散层)及漏极(漏极扩散层)发挥作用。

[0036]

另外,在栅极绝缘层120p与金属层150p之间设置有掺硼(b)多晶硅层180。进而,金属层150p的上表面被绝缘层55覆盖。金属层150p的侧面被绝缘层56p覆盖。绝缘层56p作为pmos晶体管(trp)的栅极电极gcp的侧壁发挥作用。绝缘层55一部分开口,栅极电极gcp经由绝缘层55的开口连接于接触插塞c0。p

杂质扩散区域pp1及pp2分别连接于接触插塞cs。

[0037]

在接触插塞cs及c0的上表面连接有导电体层(图4中未予图示,见图10中的符号d0)。该导电体层作为图4所示的pmos晶体管trp及nmos晶体管trn与其他晶体管或外部连接端子之间的配线发挥作用。

[0038]

接触插塞cs是设置在nmos晶体管trn及pmos晶体管trp的源极或漏极与导电体层之间的导电体层。接触插塞c0是设置在nmos晶体管trn及pmos晶体管trp的栅极电极与导电体层之间的导电体层。n

杂质扩散区域np1及np2与p

杂质扩散区域pp1及pp2分别经由接触插塞cs电连接于导电体层。另外,nmos晶体管trn及pmos晶体管trp被绝缘层31覆盖。

[0039]

所述cmosfet例如是按以下所述而制造的。参照图5、图6及图7来说明cmosfet的制造步骤。首先,如图5(a)所示,准备半导体衬底110,再如图5(b)所示,在其一面上成膜出栅极绝缘层120。此外,图4所示的p型井区域pw、n型井区域nw、n

杂质扩散区域np1及np2、p

杂质扩散区域pp1及pp2的图示被省略了。

[0040]

如图5(c)所示,在栅极绝缘层120之上依次成膜出第1层131、第2层132、第3层133,从而形成积层半导体层130。如图5(d)所示,在第3层133之上成膜出氧化膜160。氧化膜160例如是通过热氧化而形成的。

[0041]

继而,如图5(e)所示,成膜出终止层170。终止层170例如可以使用氮化硅(sin)。如图5(f)所示,将以后要形成pmos晶体管trp的那侧去除。作为去除方法,例如可以使用rie。

[0042]

如图6(g)所示,成膜出pmos晶体管trp的栅极绝缘层120p,再在栅极绝缘层120p之上成膜出掺硼(b)多晶硅层180。掺b多晶硅层180不仅成膜在以后要形成pmos晶体管trp的那侧(pmos晶体管trp侧)的栅极绝缘层120p上,还成膜在以后要设置nmos晶体管trn的那侧(nmos晶体管trn侧)的终止层170上。如图6(h)所示,在掺b多晶硅层180上成膜出终止层190。例如,终止层190可以使用sin。

[0043]

如图6(i)所示,通过rie将nmos晶体管trn侧的掺b多晶硅层180去除。如图6(j)所示,形成将nmos晶体管trn与pmos晶体管trp分离的sti槽200。

[0044]

如图7(k)所示,向sti槽200内填充填充物201。填充物201例如可以使用sio。向sti槽200中填充填充物201后,将终止层170的一部分、终止层190的一部分、及填充物201的一部分去除。作为去除方法,可以使用cmp。如图7(l)所示,将nmos晶体管trn侧的终止层170、及pmos晶体管trp侧的终止层190去除。作为去除方法,可以使用湿式蚀刻。

[0045]

如图7(m)所示,将nmos晶体管trn的氧化膜160、及3层多晶半导体层130的第3层133的上层部分去除。作为去除方法,可以使用湿式蚀刻。如图7(n)所示,在nmos晶体管trn侧的第3层133上、及pmos晶体管trp侧的掺b多晶硅层180上,成膜出tsi层140。如图7(o)所示,在tsi层140上成膜出金属层150。

[0046]

追加nmos晶体管trn侧与pmos晶体管trp侧的形成所需的步骤,如将金属层150分在nmos晶体管trn侧与pmos晶体管trp侧等,从而制作cmosfet,但相关图示被省略了。

[0047]

在所述制造步骤的步骤(e)中,如果不成膜出第3层133,而在第2层132上直接成膜出终止(sin)层170,那么在后续步骤中受热时,有可能会在第2层132与终止层170的界面发生异常氧化。该异常氧化被认为是第2层132中所包含的c捕获了第1层131中所掺杂的磷(p)而导致的,会在形成sti(填充物201)后进行蚀刻(步骤(l))时产生蚀刻残渣等。该蚀刻残渣有可能会导致晶体管的漏电流增大。另外,蚀刻残渣会导致栅极电极100(gcn)间发生短路等,从而成为了使制造良率下降的主要因素。

[0048]

因此,实施方式的栅极电极100中,在第2层132上设置有p浓度较第1层131低的第3层133。第3层133使用的是掺杂有低浓度的p或未掺杂p的多晶硅等,因此能够抑制p在热步骤中发生偏析等。由此,能够防止蚀刻残渣的产生。结果,能够抑制蚀刻残渣导致的缺陷产

生,从而能够提高晶体管的性能。进而,通过减少蚀刻残渣,也能够提高晶体管的良率。

[0049]

(第3实施方式/半导体存储装置)

[0050]

作为第2实施方式的半导体装置的cmosfet例如可以用于将存储单元晶体管三维积层在半导体衬底上的三维积层型非易失性存储设备的控制电路等。不过,第2实施方式的半导体装置的用途并不限于此,而可以用于各种半导体装置。作为第3实施方式的半导体存储装置,参照图8、图9及图10来说明三维积层型nand型闪速存储器。

[0051]

图8是表示第3实施方式的三维积层型nand型闪速存储器的整体构成的框图。如图8所示,半导体存储装置1例如由外部的存储控制器2来控制。半导体存储装置1包含存储单元阵列10、指令寄存器11、地址寄存器12、定序器13、驱动器模块14、行解码器模块15及感测放大器模块16。

[0052]

存储单元阵列10包含多个块blk0~blk(l-1)(l为2以上的整数)。块blk是非易失地存储数据的多个存储单元晶体管(下文有时简称“存储单元”)的集合体,例如用作数据的抹除单位。在存储单元阵列10设置有多个位线及多个字线。各存储单元晶体管例如与1个位线及1个字线相关联。关于存储单元阵列10的详细构成,将在下文加以说明。

[0053]

指令寄存器11保存半导体存储装置1从存储控制器2接收到的指令cmd。指令cmd例如包含使定序器13执行读出动作、写入动作及抹除动作等的命令。地址寄存器12保存半导体存储装置1从存储控制器2接收到的地址信息add。地址信息add例如包含块地址ba、页地址pa及列地址ca。例如,块地址ba、页地址pa及列地址ca分别用于块blk、字线及位线的选择。

[0054]

定序器13控制半导体存储装置1整体的动作。例如,定序器13基于指令寄存器11中所保存的指令cmd控制驱动器模块14、行解码器模块15及感测放大器模块16等,从而执行读出动作、写入动作及抹除动作等。

[0055]

驱动器模块14产生读出动作、写入动作及抹除动作等中所要使用的电压。然后,驱动器模块14例如基于地址寄存器12中所保存的页地址pa,将所产生的电压施加给与选择字线对应的信号线。

[0056]

行解码器模块15基于地址寄存器12中所保存的块地址ba,选择对应存储单元阵列10内的1个块blk。然后,行解码器模块15例如向选择块blk内的选择字线传输施加给与选择字线对应的信号线的电压。

[0057]

感测放大器模块16在写入动作中,根据从存储控制器2接收到的写入数据dat,对各位线施加所期望的电压。另外,感测放大器模块16在读出动作中,基于位线的电压对存储单元中所存储的数据进行判定,并将判定结果作为读出数据dat传输给存储控制器2。

[0058]

半导体存储装置1与存储控制器2之间的通信例如支持nand接口。例如,在半导体存储装置1与存储控制器2之间的通信中,会使用指令锁存使能信号cle、地址锁存使能信号ale、写使能信号wen、读使能信号ren、就绪忙碌信号rbn及输入输出信号i/o。

[0059]

指令锁存使能信号cle是表示半导体存储装置1所接收到的输入输出信号i/o为指令cmd的信号。地址锁存使能信号ale是表示半导体存储装置1所接收到的信号i/o为地址信息add的信号。写使能信号wen是命令半导体存储装置1将输入输出信号i/o输入的信号。读使能信号ren是命令半导体存储装置1将输入输出信号i/o输出的信号。

[0060]

就绪忙碌信号rbn是通知存储控制器2半导体存储装置1究竟是处于可以受理来自

存储控制器2的命令的就绪状态还是处于不可受理命令的忙碌状态的信号。

[0061]

输入输出信号i/o例如为8比特宽度的信号,可以包含指令cmd、地址信息add、数据dat等。

[0062]

上文所说明的半导体存储装置1及存储控制器2也可以通过组合而构成1个半导体装置。作为这种半导体装置,例如可以例举sd卡等存储卡或ssd(solid state drive,固态驱动器)等。

[0063]

接着,使用图9,对存储单元阵列10的电路构成进行说明。图9的例子表示的是块blk0,其他块blk的电路构成也是相同的。如图9所示,块blk例如包含4个串单元su0~su3。各串单元su包含多个nand串ns。

[0064]

多个nand串ns分别与位线bl0~bl(n-1)(n为2以上的整数)相关联。各nand串ns例如包含存储单元晶体管mc0~mc7、以及选择晶体管st1及st2。

[0065]

存储单元晶体管mc包含控制栅极及电荷储存层,非易失地保存数据。下面,在不限定是存储单元晶体管mc0~mc7中的哪一个的情况下,记作存储单元晶体管mc。此外,存储单元晶体管mc既可以是对电荷储存层使用绝缘膜的monos型,也可以是对电荷储存层使用导电体层的fg型。下面,在实施方式中,以monos型为例进行说明。

[0066]

选择晶体管st1用来在各种动作时选择串单元su。在各nand串ns中,选择晶体管st1的漏极连接于相关联的位线bl。选择晶体管st1的源极连接于串联连接的存储单元晶体管mc0~mc7的一端。串联连接的存储单元晶体管mc0~mc7的另一端连接于选择晶体管st2的漏极。

[0067]

在同一个块blk中,选择晶体管st2的源极共通连接于源极线sl。串单元su0~su3内的选择晶体管st1的栅极分别共通连接于选择栅极线sgd0~sgd3。存储单元晶体管mc0~mc7的控制栅极分别共通连接于字线wl0~wl7。选择晶体管st2的栅极共通连接于选择栅极线sgs。

[0068]

上文所说明的存储单元阵列10的电路构成中,被分配了相同列地址ca的多个nand串ns在多个块blk间共通连接于相同的位线bl。源极线sl在多个块blk间共通连接。

[0069]

此外,实施方式的半导体存储装置1所具备的存储单元阵列10的电路构成并不限定于上文所说明的构成。例如,各nand串ns所包含的存储单元晶体管mc、以及选择晶体管st1及st2的个数可以分别设计为任意个数。各块blk所包含的串单元su的个数可以设计为任意个数。

[0070]

接着,使用图10,对存储单元阵列10的剖面构成进行说明。如图10所示,在半导体衬底100上形成有绝缘层31。绝缘层31例如可以使用氧化硅(sio)。在绝缘层31内设置有电路区域ua,在绝缘层31上设置有存储单元阵列10。在电路区域ua例如形成有供感测放大器模块16等使用的电路。

[0071]

首先,对存储单元阵列10的构成进行说明。在绝缘层31上设置有作为源极线sl发挥作用的导电体层32。例如,导电体层32形成为沿着与半导体衬底100大致平行的xy平面扩展的板状。导电体层32是使用导电材料而形成的,导电材料例如包括金属材料或半导体材料等。

[0072]

在导电体层32上交替地积层有11层绝缘层33与10层导电体层34。绝缘层33例如可以使用sio。10层导电体层34例如从下方起依次作为选择栅极线sgs、字线wl0~wl7及选择

栅极线sgd发挥作用。例如,导电体层34形成为沿着x方向延伸的板状。导电体层34是使用导电材料而形成的,导电材料例如包括金属材料。

[0073]

设置有贯通(通过)10层导电体层34从而底面到达导电体层32的多个存储柱mp。存储柱mp沿着与半导体衬底100大致垂直且与x及y方向交叉的z方向延伸。1个存储柱mp对应1个nand串ns。存储柱mp包含块绝缘膜35、电荷储存层36、隧道绝缘膜37、半导体层38、核心层39及上覆层40。

[0074]

更具体来说,以贯通10层导电体层34从而底面到达导电体层32的方式,形成有与存储柱mp对应的孔洞。在孔洞的侧面依次积层有块绝缘膜35、电荷储存层36及隧道绝缘膜37。而且,以侧面与隧道绝缘膜37相接且底面与导电体层32相接的方式,形成有半导体层38。半导体层38是形成存储单元晶体管mc、以及选择晶体管st1及st2的通道的区域。由此,半导体层38作为将选择晶体管st2、存储单元晶体管mc0~mc7及选择晶体管st1的电流路径连接的信号线发挥作用。在半导体层38内设置有核心层39。而且,在半导体层38及核心层39上形成有侧面与隧道绝缘膜37相接的上覆层40。

[0075]

块绝缘膜35、隧道绝缘膜37及核心层39例如可以使用sio。电荷储存层36例如可以使用氮化硅(sin)。半导体层38及上覆层40例如可以使用多晶硅。

[0076]

存储柱mp与分别作为字线wl0~wl7发挥作用的8层导电体层34组合,而作为存储单元晶体管mc0~mc7发挥作用。同样地,存储柱mp与分别作为选择栅极线sgd及sgs发挥作用的2层导电体层34组合,而作为选择晶体管st1及st2发挥作用。

[0077]

在上覆层40上形成有接触插塞cp。在接触插塞cp上形成有作为位线bl发挥作用的导电体层(未图示)。接触插塞cp是使用导电材料而形成的,导电材料例如可以使用金属材料。

[0078]

此外,在图10的例子中,3个存储柱mp沿着y方向而配置,但其实存储柱mp可以任意配置。

[0079]

电路区域ua包含具有所述pmos晶体管trp与nmos晶体管trn的半导体装置。如上所述,能够抑制蚀刻残渣导致的缺陷产生。

[0080]

此外,pmos晶体管trp及nmos晶体管trn例如也可以用于指令寄存器11、地址寄存器12、定序器13、驱动器模块14、行解码器模块15及感测放大器模块16等。

[0081]

对本发明的若干个实施方式进行了说明,但这些实施方式是作为例子而提出的,并非想要限定发明的范围。这些新颖的实施方式可以采用其他各种方式来实施,在不脱离发明主旨的范围内,可以进行各种省略、替换、变更。这些实施方式及其变形包含在发明的范围及主旨中,并且包含在权利要求书所记载的发明及其等同的范围内。

[0082]

[符号的说明]

[0083]1ꢀꢀꢀꢀꢀꢀꢀꢀ

半导体存储装置

[0084]2ꢀꢀꢀꢀꢀꢀꢀꢀ

存储控制器

[0085]

10

ꢀꢀꢀꢀꢀꢀꢀ

存储单元阵列

[0086]

11

ꢀꢀꢀꢀꢀꢀꢀ

指令寄存器

[0087]

12

ꢀꢀꢀꢀꢀꢀꢀ

地址寄存器

[0088]

13

ꢀꢀꢀꢀꢀꢀꢀ

定序器

[0089]

14

ꢀꢀꢀꢀꢀꢀꢀ

驱动器模块

[0090]

15

ꢀꢀꢀꢀꢀꢀꢀ

行解码器模块

[0091]

16

ꢀꢀꢀꢀꢀꢀꢀ

感测放大器模块

[0092]

58,59

ꢀꢀꢀꢀ

导电体层

[0093]

35

ꢀꢀꢀꢀꢀꢀꢀ

块绝缘膜

[0094]

36

ꢀꢀꢀꢀꢀꢀꢀ

电荷储存层

[0095]

37

ꢀꢀꢀꢀꢀꢀꢀ

隧道绝缘膜

[0096]

100

ꢀꢀꢀꢀꢀꢀ

栅极电极

[0097]

110

ꢀꢀꢀꢀꢀꢀ

半导体衬底

[0098]

120,120p 栅极绝缘层

[0099]

130

ꢀꢀꢀꢀꢀꢀ

3层多晶半导体层

[0100]

131

ꢀꢀꢀꢀꢀꢀ

第1层

[0101]

132

ꢀꢀꢀꢀꢀꢀ

第2层

[0102]

133

ꢀꢀꢀꢀꢀꢀ

第3层

[0103]

140

ꢀꢀꢀꢀꢀꢀ

tsi层

[0104]

150,150p 金属层

[0105]

160

ꢀꢀꢀꢀꢀꢀ

氧化膜。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。