技术特征:

1.一种集成组件,其包括:基底上方的存储器叠层;沿着所述存储器叠层的存储器单元阵列;所述阵列包括沿着行方向延伸的行和沿着列方向延伸的列;沿着所述阵列的所述行并且沿着所述行方向延伸的字线;沿着所述阵列的所述列并且沿着所述列方向延伸的数位线;所述阵列中的每个所述存储器单元由所述字线中的一个和所述数位线中的一个相结合唯一地寻址;沿着所述基底的控制电路系统;所述控制电路系统包含与所述字线耦合的字线驱动器电路系统;所述控制电路系统被细分为存储体;所述存储体沿着所述行方向物理地伸长;每个所述存储体被细分为一系列区段,所述区段被布置在沿着所述行方向延伸的区段行中;并且每个所述区段均包括一系列贴片,所述贴片包含输入/输出电路系统;所述贴片被布置成组,所述组共享所述字线驱动器电路系统的部分;每一组内的所述字线驱动器电路系统的所述部分包含沿着所述组的所述贴片中的一个的第一节段并且包含沿着所述组的相邻贴片的第二节段,所述第一节段和所述第二节段沿着所述行方向和所述列方向两者彼此偏移。2.根据权利要求1所述的集成组件,其包括每一个所述存储体内的所述区段中的8个。3.根据权利要求1所述的集成组件,其包括每个所述区段内的所述贴片中的17个,并且其中每个所述组包含所述贴片中的四个。4.根据权利要求1所述的集成组件,其包括每个所述区段内的所述贴片中的34个,并且其中每个所述组包含所述贴片中的10个。5.根据权利要求1所述的集成组件,其中所述区段中的第一个的边缘与所述区段中的相邻第二个共享一组内的一或多个贴片。6.根据权利要求5所述的集成组件,其中所述一或多个贴片中的至少一个并入所述区段中的所述第一个和所述第二个中的一或两个的冗余电路系统中。7.根据权利要求1所述的集成组件,其中所述控制电路系统包含与所述数位线耦合的感测放大器电路系统。8.根据权利要求1所述的集成组件,其包括所述基底上方的所述存储器叠层中的两个存储器叠层;其中所述字线驱动器电路系统被划分为第一字线驱动器子电路系统和第二字线驱动器子电路系统,所述第一字线驱动器子电路系统与所述存储器叠层中的一个的所述字线耦合,并且所述第二字线驱动器子电路系统与所述存储器叠层中的另一个的所述字线耦合。9.根据权利要求1所述的集成组件,其包括:每一个所述存储体内的所述区段行中的两个或更多个;沿着所述列方向彼此邻近并且通过共享插口区域彼此间隔开的一对所述存储体;以及所述共享插口区域内的全局输入/输出总线。10.根据权利要求9所述的集成组件,其中所述全局输入/输出总线沿着所述行方向延伸所述存储体的全长。11.根据权利要求9所述的集成组件,其中所述全局输入/输出总线被细分为两个或更

多个节段,每个节段沿着所述行方向延伸的长度小于所述存储体的全长。12.根据权利要求1所述的集成组件,其包括:每个所述存储体内的所述区段行中的三个;沿着所述列方向彼此邻近并且通过共享插口区域彼此间隔开的一对所述存储体;第一系列的第一全局输入/输出线,其沿着所述列方向延伸并且从所述共享插口区域延伸到与所述一对所述存储体中的所述存储体中的一个的所述区段相邻的第一组本地总线;以及第二系列的第二全局输入/输出线,其沿着所述列方向延伸并且从所述共享插口区域延伸到与所述一对所述存储体中的所述存储体中的另一个的所述区段相邻的第二组本地总线。13.根据权利要求12所述的集成组件,其包括第一本地输入/输出线,所述第一本地输入/输出线从所述第一组所述本地总线延伸到所述存储体中的所述一个的所述区段中;以及第二本地输入/输出线,所述第二本地输入/输出线从所述第二组所述本地总线延伸到所述存储体中的所述另一个的所述区段中。14.根据权利要求1所述的集成组件,其中各个区段的边缘贴片在逻辑上彼此合并。15.根据权利要求1所述的集成组件,其中各个区段行的边缘贴片在逻辑上彼此合并。16.根据权利要求1所述的集成组件,其中所述基底对应于半导体管芯;所述集成组件包括与所述输入/输出电路系统耦合的gio;并且其中所述gio包含一或多个节段,所述一或多个节段延伸小于所述管芯的长度的约1/3。17.根据权利要求16所述的集成组件,其中所述一或多个节段延伸小于所述管芯的长度的约1/6。18.根据权利要求16所述的集成组件,其中所述一或多个节段延伸小于所述管芯的长度的约1/8。19.根据权利要求16所述的集成组件,其中沿着所述gio的信号具有全轨操作。20.一种集成组件,其包括:基底上方的存储器叠层;沿着所述存储器叠层的存储器单元阵列;所述阵列包括沿着行方向延伸的行并且包括沿着列方向延伸的列;沿着所述存储器阵列的所述行并且沿着所述行方向延伸的字线;沿着所述存储器阵列的所述列并且沿着所述列方向延伸的数位线;所述存储器阵列中的每个所述存储器单元由所述字线中的一个和所述数位线中的一个相结合唯一地寻址;沿着所述基底的控制电路系统;所述控制电路系统包含与所述字线耦合的字线驱动器电路系统;所述控制电路系统被细分为存储体;所述存储体沿着所述行方向物理地伸长;所述基底对应于半导体管芯;所述管芯具有沿着所述行方向延伸的第一侧和与所述第一侧呈相对关系的第二侧;所述管芯被细分为四个象限区域;所述象限区域中的两个沿着所述第一侧并且通过插口区域彼此间隔开;所述象限区域中的所述两个是第一象限区域和第二象限区域;所述第一象限区域和所述第二象限区域各自包括8个存储体;每个所述存储体被细分为一系列区段,所述区段被布置在沿着所述行方向延伸的区段行中;每个所述存储体包括所述区段行中的多于一个;每个所述区段均包括一系列贴片,所述贴片包含输入/

输出电路系统;并且其中所述贴片被布置成组,所述组共享所述字线驱动器电路系统的部分。21.根据权利要求20所述的集成组件,其中所述第一象限区域和所述第二象限区域通过包含存储体逻辑电路系统的中间区域彼此间隔开。22.根据权利要求21所述的集成组件,其中所述存储体逻辑电路系统包含行解码器电路系统。23.根据权利要求20所述的集成组件,其包括每个所述存储体内的所述区段中的8个。24.根据权利要求23所述的集成组件,其包括每个所述区段内的所述贴片中的17个,并且其中每个所述组包含所述贴片中的四个。25.根据权利要求23所述的集成组件,其包括每个所述区段内的所述贴片中的34个,并且其中每个所述组包含所述贴片中的10个。26.根据权利要求20所述的集成组件,其中所述存储体中的一个内的所述区段中的第一个的边缘与所述存储体中的所述一个内的所述区段中的相邻第二个共享一组内的一或多个贴片。27.根据权利要求26所述的集成组件,其中所述一或多个贴片中的至少一个并入所述区段中的所述第一个和所述第二个中的一或两个的冗余电路系统中。28.根据权利要求20所述的集成组件,其包括所述基底上方的所述存储器叠层中的两个;其中所述字线驱动器电路系统被划分为第一字线驱动器子电路系统和第二字线驱动器子电路系统,所述第一字线驱动器子电路系统与所述存储器叠层中的一个的字线耦合,并且所述第二字线驱动器子电路系统与所述存储器叠层中的另一个的字线耦合。29.根据权利要求20所述的集成组件,其包括沿着所述第二侧的所述象限区域中的另外两个;所述象限区域中的所述另外两个是第三象限区域和第四象限区域;所述第三象限区域和所述第四象限区域各自包括8个存储体,所述第三象限区域和所述第四象限区域的每个所述存储体包括被布置在沿着所述行方向延伸的区段行中的区段;并且所述第三象限区域和所述第四象限区域的每个所述区段包括一系列贴片,所述贴片包含输入/输出电路系统。30.根据权利要求20所述的集成组件,其包括:沿着所述列方向彼此邻近并且通过共享插口区域彼此间隔开的一对所述存储体;第一系列的第一全局输入/输出线,其沿着所述列方向延伸并且从所述共享插口区域延伸到与所述一对所述存储体中的所述存储体中的一个的所述区段相邻的第一组本地总线;以及第二系列的第二全局输入/输出线,其沿着所述列方向延伸并且从所述共享插口区域延伸到与所述一对所述存储体中的所述存储体中的另一个的所述区段相邻的第二组本地总线。31.根据权利要求30所述的集成组件,其中所述第一系列的第一全局输入/输出线和所述第二系列的第二全局输入/输出线具有在所述存储体中的所述一个和所述存储体中的所述另一个的所述区段中的一或多个上方的区域。32.一种集成组件,其包括:基底上方的第一存储器叠层;

所述第一存储器叠层上方的第二存储器叠层;沿着所述第一存储器叠层的第一组存储器单元阵列;所述第一组包括沿着行方向延伸的第一行并且包括沿着列方向延伸的第一列;沿着所述第一存储器叠层的第二组存储器单元阵列;所述第二组包括沿着所述行方向延伸的第二行并且包括沿着所述列方向延伸的第二列;沿着所述第一行并且沿着所述行方向延伸的第一字线;沿着所述第二行并且沿着所述行方向延伸的第二字线;沿着所述基底的控制电路系统;所述控制电路系统包含与所述第一字线耦合的第一字线驱动器子电路系统和与所述第二字线耦合的第二字线驱动器子电路系统;所述控制电路系统被细分为存储体;所述存储体沿着所述行方向物理地伸长;每个所述存储体被细分为一系列区段,所述区段被布置在沿着所述行方向延伸的区段行中;每个所述区段均包括一系列第一贴片,所述第一贴片包含第一输入/输出电路系统;所述第一贴片被布置成第一组,所述第一组共享所述第一字线驱动器子电路系统的部分;每个第一组内的所述第一字线驱动器子电路系统的所述部分包含沿着所述第一组的所述第一贴片中的一个的第一节段并且包含沿着所述第一组的相邻第一贴片的第二节段,所述第一节段和所述第二节段沿着所述行方向和所述列方向彼此偏移;每个所述区段均包括一系列第二贴片,所述第二贴片包含第二输入/输出电路系统;所述第二贴片被布置成第二组,所述第二组共享所述第二字线驱动器子电路系统的部分;每个第二组内的所述第二字线驱动器子电路系统的所述部分包含沿着所述第二组的所述第二贴片中的一个的第三节段并且包含沿着所述第二组的相邻第二贴片的第四节段,所述第三节段和所述第四节段沿着所述行方向和所述列方向彼此偏移;并且其中所述第三节段和所述第四节段沿着所述行方向相对于所述第一节段和所述第二节段移位。33.根据权利要求32所述的集成组件,其包括每个所述存储体内的所述区段中的8个。34.根据权利要求32所述的集成组件,其包括每个所述区段内的所述第一贴片中的17个,并且其中每个所述第一组包含所述第一贴片中的四个。35.根据权利要求34所述的集成组件,其包括每个所述区段内的所述第二贴片中的17个,并且其中每个所述第二组包含所述第二贴片中的四个。36.根据权利要求32所述的集成组件,其包括每个所述区段内的所述第一贴片中的34个,并且其中每个所述第一组包含所述第一贴片中的10个。37.根据权利要求36所述的集成组件,其包括每个所述区段内的所述第二贴片中的34个,并且其中每个所述第二组包含所述第二贴片中的10个。38.根据权利要求32所述的集成组件,其中所述区段中的第一个的边缘与所述区段中的相邻第二个共享第一组内的一或多个第一贴片。39.根据权利要求38所述的集成组件,其中所述一或多个第一贴片中的至少一个并入所述区段中的所述第一个和所述第二个中的一或两个的冗余电路系统中。40.根据权利要求32所述的集成组件,其中所述第三节段和第四节段沿着所述行方向相对于所述第一节段和第二节段移位达所述组中的一个的约一半的距离。

41.根据权利要求32所述的集成组件,其包括:每个所述存储体内的所述区段行中的三个;沿着所述列方向彼此邻近并且通过共享插口区域彼此间隔开的一对所述存储体;第一系列的第一全局输入/输出线,其沿着所述列方向延伸并且从所述共享插口区域延伸到沿着所述一对所述存储体中的所述存储体中的一个的所述区段的第一组本地总线;以及第二系列的第二全局输入/输出线,其沿着所述列方向延伸并且从所述共享插口区域延伸到沿着所述一对所述存储体中的所述存储体中的另一个的所述区段的第二组本地总线。42.根据权利要求41所述的集成组件,其中所述第一组和所述第二组的所述本地总线沿着所述行方向延伸。

技术总结

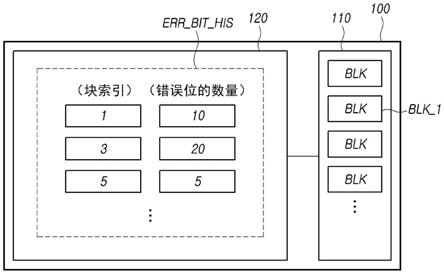

一些实施例包含一种集成组件,所述集成组件具有在基底上方的存储器叠层,并且具有沿着存储器叠层的存储器单元阵列。阵列包含沿着行方向延伸的行和沿着列方向延伸的列。字线沿着行,而数字线沿着列。控制电路系统沿着基底并且包含与字线耦合的字线驱动器电路系统。控制电路系统被细分为存储体。存储体沿着行方向伸长。每个存储体被细分为一系列区段,所述区段被布置在沿着行方向延伸的区段行中。每个区段均包含一系列贴片,所述贴片包含输入/输出电路系统。贴片被布置成组,所述组共享字线驱动器电路系统的部分。器电路系统的部分。器电路系统的部分。

技术研发人员:李继云 何源

受保护的技术使用者:美光科技公司

技术研发日:2021.06.09

技术公布日:2022/3/15

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。