半导体装置及其制造方法

1.[相关申请的交叉参考]

[0002]

本技术案基于2020年09月14日提出申请的在先日本专利申请案第2020-154035号的优先权而主张优先权利益,通过引用使其全部内容并入本文中。

技术领域

[0003]

本发明的实施方式涉及一种半导体装置及其制造方法。

背景技术:

[0004]

在三维存储器等半导体存储器中,希望提高通道半导体层等半导体层的性能。

技术实现要素:

[0005]

根据一实施方式,半导体装置具备:衬底;以及积层膜,包含交替设置在所述衬底上方的多层电极层及多层绝缘层。所述装置还具备:第1半导体层,设置在所述积层膜内;以及第2半导体层,在所述积层膜内设置在所述第1半导体层上,且包含单晶半导体层。所述装置还具备配线层,所述配线层设置在所述积层膜及所述第2半导体层上,与所述第2半导体层电连接。

附图说明

[0006]

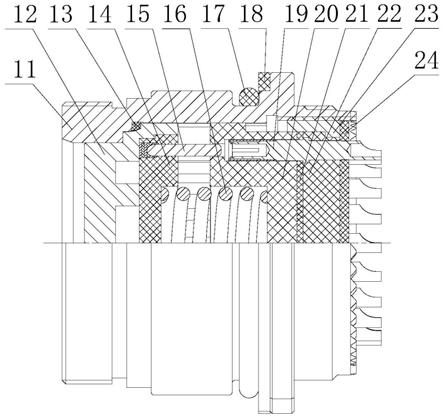

图1是表示第1实施方式的半导体装置的构造的剖视图。

[0007]

图2是表示第1实施方式的柱状部的构造的放大剖视图。

[0008]

图3是表示第1实施方式的半导体装置的构造的放大剖视图。

[0009]

图4是表示第1实施方式的比较例的半导体装置的构造的放大剖视图。

[0010]

图5(a)及(b)、图6(a)及(b)、图7(a)及(b)、图8(a)及(b)、图9(a)及(b)、图10(a)及(b)是表示第1实施方式的半导体装置的制造方法的剖视图。

[0011]

图11(a)及(b)是表示第1实施方式的变化例的半导体装置的制造方法的剖视图。

[0012]

图12是表示第1实施方式的半导体装置的整体构造的剖视图。

具体实施方式

[0013]

以下,参照附图,对本发明的实施方式进行详细说明。在图1到图12中,对相同构成标注相同符号,并省略重复的说明。

[0014]

(第1实施方式)

[0015]

图1是表示第1实施方式的半导体装置的构造的剖视图。

[0016]

本实施方式的半导体装置例如是三维存储器,具备电路区域1、以及设置在电路区域1上的阵列区域2。例如,如下所述,本实施方式的半导体装置是通过将包含电路区域1的电路晶圆与包含阵列区域2的阵列晶圆贴合而制造。图1示出了电路区域1(电路晶圆)与阵列区域2(阵列晶圆)的贴合面s。

[0017]

本实施方式的半导体装置在电路区域1内具备衬底11、晶体管12及层间绝缘层13,在阵列区域2内具备层间绝缘膜21、积层膜22、层间绝缘膜23及多个柱状部24。晶体管12包含栅极绝缘膜12a、栅极电极12b及绝缘膜12c。积层膜22包含多层电极层22a及多层绝缘层22b。各柱状部24包含存储器绝缘膜24a、半导体层24b、通道半导体层24c及核心绝缘膜24d。通道半导体层24c是第1半导体层的例子,半导体层24b是第2半导体层的例子。

[0018]

本实施方式的半导体装置在电路区域1内还具备接触插塞31、包含1条以上配线的配线层32、介层插塞33、包含1条以上配线的配线层34、介层插塞35、包含1条以上配线的配线层36、介层插塞37及金属垫38,在阵列区域2内还具备金属垫41、介层插塞42、包含1条以上配线的配线层43、配线层51及钝化膜52。配线层51包含半导体层51a及金属层51b。半导体层51a是第3半导体层的例子。

[0019]

图1示出了相互垂直的x方向、y方向及z方向。在本说明书中,将 z方向视作上方向,将-z方向视作下方向。-z方向可与重力方向一致,也可以与重力方向不一致。z方向是第1方向的例子。

[0020]

衬底11例如是硅衬底等半导体衬底。晶体管12具备:栅极绝缘膜12a,形成在衬底11上;栅极电极12b,形成在栅极绝缘膜12a上;以及绝缘膜12c,形成在栅极电极12b的侧面。本实施方式的半导体装置在衬底11上具备多个晶体管12,图1示出了这些晶体管12中的1个。这些晶体管12例如构成了控制本实施方式的半导体装置的动作的控制电路(逻辑电路)。层间绝缘层13以覆盖这些晶体管12的方式形成在衬底11上。

[0021]

层间绝缘膜21形成在层间绝缘层13上。积层膜22包含交替积层在层间绝缘膜21上的多层电极层22a及多层绝缘层22b。本实施方式的这些电极层22a如下所述包含多条字线、1条以上源极侧选择线及1条以上漏极侧选择线。各电极层22a例如包含w(钨)层等金属层。各绝缘层22b例如是氧化硅膜。层间绝缘膜23形成在积层膜22上。

[0022]

各柱状部24具有在z方向上延伸的柱状形状,形成在层间绝缘膜21、积层膜22及层间绝缘膜23内。各柱状部24包含:存储器绝缘膜24a,形成在层间绝缘膜21、积层膜22及层间绝缘膜23的侧面;半导体层24b及通道半导体层24c,形成在存储器绝缘膜24a的侧面;以及核心绝缘膜24d,形成在通道半导体层24c的侧面。

[0023]

存储器绝缘膜24a具有在z方向上延伸的管状形状,包围半导体层24b及通道半导体层24c。如下所述,存储器绝缘膜24a包含阻挡绝缘膜、电荷蓄积层及隧道绝缘膜。

[0024]

通道半导体层24c具有在z方向上延伸的管状形状,包围核心绝缘膜24d。具体来说,通道半导体层24c包含:侧面部分p1,具有在z方向上延伸的管状形状;以及底面部分p2,具有设置在该管的上端的底面形状。通道半导体层24c例如是多晶硅(polysilicon)层等多晶半导体层。侧面部分p1是第1部分的例子,底面部分p2是第2部分的例子。另外,通道半导体层24c可包含n型杂质原子或p型杂质原子,也可以不包含n型杂质原子及p型杂质原子中的任一种。

[0025]

半导体层24b具有在z方向上延伸的非管状形状,形成在通道半导体层24c的底面部分p2上。通道半导体层24c的侧面部分p1具有管状形状即中空的柱状形状,相对地,半导体层24b具有非管状形状即实心的柱状形状。半导体层24b例如是单晶硅(monocrystalline silicon)层等单晶半导体层。本实施方式的半导体层24b在与层间绝缘膜23的上表面相同的高度具有上表面,在比层间绝缘膜23的下表面更低的高度具有下表面。另外,关于本实施

方式的半导体层24b的下表面的高度的详细内容,将在下文叙述。

[0026]

半导体层24b例如包含n型杂质原子或p型杂质原子。半导体层24b内的n型杂质原子或p型杂质原子的浓度例如为1.0

×

10

19

cm-3

以上。本实施方式的半导体层24b包含浓度为1.0

×

10

19

cm-3

至5.0

×

10

19

cm-3

的p(磷)原子。

[0027]

核心绝缘膜24d具有在z方向上延伸的非管状形状,形成在通道半导体层24c的侧面部分p1内。核心绝缘膜24d例如是氧化硅膜。

[0028]

各柱状部24中,由存储器绝缘膜24a、半导体层24b、通道半导体层24c及核心绝缘膜24d构成多个存储单元晶体管或多个选择晶体管。这些存储单元晶体管或选择晶体管构成三维存储器的存储单元阵列。

[0029]

接触插塞31、配线层32、介层插塞33、配线层34、介层插塞35、配线层36、介层插塞37、金属垫38、金属垫41、介层插塞42及配线层43在衬底11上依序设置在层间绝缘膜13、21内。本实施方式的半导体装置具备多个接触插塞31、多个介层插塞33、多个介层插塞35、多个介层插塞37、多个金属垫38、多个金属垫41及多个介层插塞42,图1示出了这些插塞及垫中的一部分。所述控制电路经由这些插塞、垫及配线层与所述存储单元阵列电连接,且经由这些插塞、垫及配线层控制所述存储单元阵列的动作。

[0030]

各个金属垫38、41例如包含cu(铜)层等金属层。在本实施方式的半导体装置中,金属垫38与金属垫41相互接合,层间绝缘膜13与层间绝缘膜21相互粘接。在本实施方式中,各柱状部24形成在配线层43上,由此,各柱状部24的通道半导体层24c与配线层43电连接。

[0031]

配线层51包含:半导体层51a,形成在层间绝缘膜23及各柱状部24上;以及金属层51b,形成在半导体层51a上。在本实施方式中,半导体层51a与各柱状部24的半导体层24b相接,由此,配线层51与各柱状部24的半导体层24b电连接。半导体层51a例如是掺杂了p原子的多晶硅层。

[0032]

钝化膜52形成在配线层51上。钝化膜52例如是氧化硅膜等绝缘膜。钝化膜52也可以包含氧化硅膜及其它绝缘膜。

[0033]

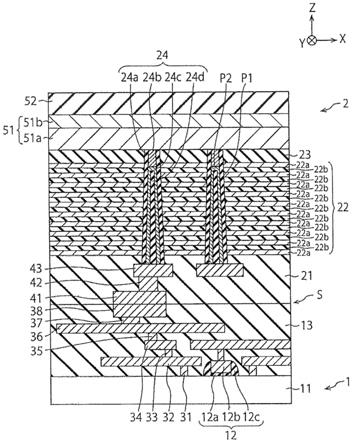

图2是表示第1实施方式的柱状部24的构造的放大剖视图。

[0034]

如图2所示,柱状部24包含依序形成在积层膜22内的存储器绝缘膜24a、通道半导体层24c(侧面部分p1)及核心绝缘膜24d。存储器绝缘膜24a包含依序形成在积层膜22内的阻挡绝缘膜61、电荷蓄积层62及隧道绝缘膜63。

[0035]

阻挡绝缘膜61例如是氧化硅膜。电荷蓄积层62例如是氮化硅膜等绝缘膜,具有蓄积信号电荷的功能。电荷蓄积层62也可以是多晶硅层等半导体层。隧道绝缘膜63例如是氧化硅膜。阻挡绝缘膜61、电荷蓄积层62及隧道绝缘膜63均具有在z方向上延伸的管状形状,包围通道半导体层24c及半导体层24b(参照图1)。

[0036]

图3是表示第1实施方式的半导体装置的构造的放大剖视图。

[0037]

图3示出了交替包含多层电极层22a及多层绝缘层22b的积层膜22、以及设置在积层膜22内的柱状部24。这些电极层22a包含:1条以上漏极侧选择线sgd;多条字线wl,配置在漏极侧选择线sgd的上方;以及1条以上源极侧选择线sgs,设置在字线wl的上方。图3所示的这些电极层22a包含1条漏极侧选择线sgd及5条源极侧选择线sgs作为一例,但漏极侧选择线sgd的条数及源极侧选择线sgs的条数并不限定于此。漏极侧选择线sgd是第1选择线的例子,源极侧选择线sgs是第2选择线的例子。

[0038]

本实施方式的半导体层24b在与层间绝缘膜23的上表面相同的高度具有上表面,在比层间绝缘膜23的下表面更低的高度具有下表面。例如,图3所示的半导体层24b的下表面位于最下方的漏极侧选择线sgd的下表面与最上方的漏极侧选择线sgd的上表面之间的高度,此处,位于从下向上数第3条(=从上向下数第3条)漏极侧选择线sgd的下表面与上表面之间的高度。

[0039]

当抹除某一柱状部24(nand(not and,与非)串)的各存储单元的存储数据时,本实施方式的半导体装置对用于该柱状部24的指定的源极侧选择线sgs施加抹除电压。由此,在该柱状部24的指定的选择晶体管中产生gidl(gate induced drain leakage,栅诱导漏极泄漏)电流,流向各存储单元。利用该gidl电流抹除各存储单元的存储数据。

[0040]

本实施方式的所述指定的源极侧选择线sgs是与半导体层24b对向的源极侧选择线sgs,具体来说,是从上向下数第1条(最上方)漏极侧选择线sgd、从上向下数第2条漏极侧选择线sgd及从上向下数第3条漏极侧选择线sgd。当对这些源极侧选择线sgs施加抹除电压时,与这些源极侧选择线sgs对应的选择晶体管中产生gidl电流,更详细地说是半导体层24b中产生gidl电流。这些源极侧选择线sgs被称作gidl发生器。

[0041]

本实施方式的半导体层24b是为了促进该gidl电流产生而设置的。因此,如上所述,半导体层24b内包含高浓度的p原子。根据本实施方式,通过将与指定的源极侧选择线sgs(gidl发生器)对应的选择晶体管的通道区域作为半导体层24b,能够有效地产生gidl电流。

[0042]

图4是表示第1实施方式的比较例的半导体装置的构造的放大剖视图。

[0043]

图4示出了交替包含多层电极层22a及多层绝缘层22b的积层膜22、以及设置在积层膜22内的柱状部24。这些电极层22a包含:1条以上漏极侧选择线sgd;多条字线wl,配置在漏极侧选择线sgd的上方;以及1条以上源极侧选择线sgs,设置在字线wl的上方。图4所示的这些电极层22a包含1条漏极侧选择线sgd及4条源极侧选择线sgs作为一例。

[0044]

本比较例的柱状部24不包含半导体层24b。因此,在本比较例的通道半导体层24c中,侧面部分p1延伸到配线层51的下表面,底面部分p2与配线层51的下表面相接。

[0045]

本比较例的柱状部24具备设置在通道半导体层24c内的杂质扩散层25来代替半导体层24b。杂质扩散层25例如是掺杂了p原子的多晶硅层。在本比较例中,与杂质扩散层25对向的源极侧选择线sgs即最上方的源极侧选择线sgs作为gidl发生器发挥功能。本比较例的gidl电流在杂质扩散层25中产生。

[0046]

此处,将图3所示的第1实施方式的半导体装置和图4所示的比较例的半导体装置进行比较。

[0047]

在图4所示的比较例中,例如通过向通道半导体层24c内注入p原子,而形成杂质扩散层25。在这种情况下,形成杂质扩散层25的位置根据注入p原子的位置而变化。一般来说,因为希望不同柱状部24中产生的gidl电流的值接近于相同值,所以理想的是不同柱状部24的杂质扩散层25的位置接近于相同位置。然而,注入p原子的位置一般在不同的杂质扩散层25间存在差异,因此,难以使不同柱状部24的杂质扩散层25的位置接近于相同位置。进而,如果通过退火使注入到通道半导体层24c内的p原子扩散,那么p原子的位置有可能差异更大。

[0048]

另一方面,在图3所示的第1实施方式中,利用与通道半导体层24c不同的、另外形

成的半导体层24b而非通道半导体层24c内所形成的杂质扩散层25,来产生gidl电流。因此,根据本实施方式,能够容易地使不同柱状部24的半导体层24b的位置接近于相同位置,从而能够容易地使不同柱状部24中产生的gidl电流的值接近于相同值。如下所述,本实施方式的半导体层24b是通过外延生长而形成的,所以容易使不同柱状部24的半导体层24b的位置接近于相同位置。

[0049]

图12是表示第1实施方式的半导体装置的整体构造的剖视图。

[0050]

阵列区域2具备:包含多个存储单元的存储单元阵列111、存储单元阵列111上的半导体层112、半导体层112上的背栅绝缘膜113及背栅绝缘膜113上的背栅电极114。背栅电极114与下述选择栅极sg一样用于半导体层112的电场控制。阵列区域2还具备存储单元阵列111下方的层间绝缘膜21a及层间绝缘膜21a下方的绝缘膜21b作为层间绝缘膜21。绝缘膜21b例如是氧化硅膜。

[0051]

电路区域1设置在阵列区域2下方。电路区域1具备绝缘膜21b下方的绝缘膜13a、绝缘膜13a下方的层间绝缘膜13b及层间绝缘膜13b下方的衬底11,作为层间绝缘膜13。绝缘膜13a例如是氧化硅膜。衬底11例如是硅衬底等半导体衬底。

[0052]

阵列区域2具备多条字线wl及选择栅极sg作为存储单元阵列111内的电极层。图12示出了存储单元阵列111的阶梯构造部121。阵列区域2还具备所述背栅电极114作为存储单元阵列111外的电极层。如图12所示,各字线wl经由接触插塞122与字配线层123电连接,背栅电极114经由接触插塞124与背栅配线层125电连接,选择栅极sg经由接触插塞126与选择栅极配线层127电连接。贯通字线wl及选择栅极sg的柱状部24经由接触插塞43'与配线层43内的位线bl电连接,且与半导体层112电连接。另外,字线wl相当于所述电极层22a的具体例。

[0053]

电路区域1具备多个晶体管12。各晶体管12具备:栅极电极12b,介隔栅极绝缘膜12a设置在衬底11上;以及未图示的源极扩散层及漏极扩散层,设置在衬底11内。电路区域1还具备:多个接触插塞31,设置在这些晶体管12的源极扩散层或漏极扩散层上;配线层32,设置在这些接触插塞31上,且包含多条配线;以及多个介层插塞35,设置在配线层32上。电路区域1还具备:配线层36,设置在这些介层插塞35上,且包含多条配线;多个介层插塞37,设置在配线层36上;以及多个金属垫38,在绝缘膜13a内设置在这些介层插塞37上。另外,省略了所述介层插塞33及配线层34的图示。电路区域1作为控制阵列区域2的控制电路(逻辑电路)发挥功能。

[0054]

阵列区域2具备:多个金属垫41,在绝缘膜21b内设置在金属垫38上;多个介层插塞42,设置在金属垫41上;以及配线层131,设置在这些介层插塞42上,且包含多条配线。各字线wl或各位线bl与配线层131内对应的配线电连接。阵列区域2还具备:配线层132,设置在配线层131上,且包含多条配线;配线层133,设置在配线层132上,且包含多条配线;以及介层插塞134,设置在配线133上。阵列区域2还具备:金属垫135,设置在介层插塞134上;以及钝化膜136,覆盖金属垫135及背栅电极114。钝化膜136例如是氧化硅膜,具有使金属垫136的上表面露出的开口部p。金属垫136是图12的半导体装置的外部连接垫,能够经由焊球、金属凸块、键合线等而连接于安装衬底或其它装置。

[0055]

图5到图10是表示第1实施方式的半导体装置的制造方法的剖视图。

[0056]

首先,准备用于阵列晶圆4的衬底26,在衬底26上依序形成层间绝缘膜23、积层膜

22'、以及作为层间绝缘膜21的一部分的绝缘膜21a(图5(a))。衬底26例如是硅衬底等半导体衬底。积层膜22'以交替包含多层牺牲层22a'及多层绝缘层22b的方式形成。各牺牲层22a'例如是氮化硅膜。衬底26是第1衬底的例子。这些牺牲层22a'是第1膜的例子,这些绝缘层22b是第2膜的例子。

[0057]

这些牺牲层22a'在下述步骤(图8(a)的步骤)中被置换成多层电极层22a。由此,在层间绝缘膜23与绝缘膜21a之间形成交替包含多层电极层22a及多层绝缘层22b的积层膜22。

[0058]

其次,在绝缘膜21a、积层膜22'及层间绝缘膜23内形成多个存储器孔h1(图5(b))。结果,衬底26的上表面在这些存储器孔h1内露出。这些存储器孔h1是凹部的例子。

[0059]

其次,在衬底26的整面形成存储器绝缘膜24a(图6(a))。结果,在存储器孔h1内的衬底26的上表面、存储器孔h1内的绝缘膜21a、积层膜22'及层间绝缘膜23的侧面、存储器孔h1外的绝缘膜21a的上表面形成存储器绝缘膜24a。存储器绝缘膜24a是通过在衬底26的整面依序形成阻挡绝缘膜61、电荷蓄积层62及隧道绝缘膜63(图2)而形成。

[0060]

其次,通过干式蚀刻,从存储器孔h1内的衬底26的上表面、存储器孔h1外的绝缘膜21a的上表面去除存储器绝缘膜24a(图6(b))。结果,衬底26的上表面再次在存储器孔h1内露出。像这样,存储器绝缘膜24a被加工成具有在z方向上延伸的管状形状。

[0061]

其次,通过从衬底26外延生长,而在存储器孔h1内的衬底26的上表面形成半导体层24b(图7(a))。半导体层24b例如是掺杂了p原子的单晶硅层。半导体层24b内的p原子的浓度例如为1.0

×

10

19

cm-3

以上,优选为1.0

×

10

19

cm-3

至5.0

×

10

19

cm-3

。像这样,半导体层24b被加工成具有在z方向上延伸的非管状形状。

[0062]

另外,图7(a)所示的阵列晶圆4的上下方向的朝向与图3所示的阵列区域2的上下方向的朝向相反。因此,图7(a)所示的半导体层24b的上表面与图3所示的半导体层24b的下表面对应。在图7(a)的步骤中,以半导体层24b上表面的位置来到图3所示的半导体层24b下表面的位置的方式,形成半导体层24b。因此,图7(a)所示的半导体层24b的上表面位于最上方(图3中为最下方)的源极侧选择线sgs的上表面与最下方(图3中为最上方)的源极侧选择线sgs的下表面之间的高度。但是,在图7(a)所示的阶段,牺牲层22a'尚未被置换成电极层22,因此,更准确地说,图7(a)所示的半导体层24b的上表面是位于对应于最上方的源极侧选择线sgs的牺牲层22a'的上表面与对应于最下方的源极侧选择线sgs的牺牲层22a'的下表面之间的高度。

[0063]

其次,在衬底26的整面依序形成通道半导体层24c及核心绝缘膜24d,并去除存储器孔h1外的通道半导体层24c及核心绝缘膜24d(图7(b))。结果,在存储器孔h1内的半导体层24b的上表面、存储器孔h1内的积层膜22'及层间绝缘膜23的侧面形成通道半导体层24c。进而,在存储器孔h1内的通道半导体层24c的上表面及侧面形成核心绝缘膜24d。像这样,通道半导体层24c以具有在z方向上延伸的管状形状的方式形成,核心绝缘膜24d以具有在z方向上延伸的非管状形状的方式形成。具体来说,通道半导体层24c以包含侧面部分p1及底面部分p2的方式形成,所述侧面部分p1具有在z方向上延伸的管状形状,所述底面部分p2具有设置在该管的下端的底面形状。像这样,在所述多个存储器孔h1内形成多个柱状部24。

[0064]

其次,将牺牲层22a'置换成电极层22(图8(a))。具体来说,在绝缘膜21a及积层膜22'内形成狭缝,通过使用狭缝进行湿式蚀刻而去除牺牲层22a',在因去除牺牲层22a'而形

成的多个凹部内嵌埋多层电极层22。结果,在层间绝缘膜23与绝缘膜21a之间形成交替包含多层电极层22a及多层绝缘层22b的积层膜22。这些电极层22a例如包含多条字线wl、1条以上源极侧选择线sds及1条以上漏极侧选择线sdg(参照图3)。

[0065]

另外,在图5(a)的步骤中,也可以不形成交替包含多层牺牲层22a'及多层绝缘层22b的积层膜22',而是形成交替包含多层电极层22a及多层绝缘层22b的积层膜22。在这种情况下,就不必在图8(a)的步骤中将牺牲层22a'置换成电极层22a。这种情况下的电极层22a及绝缘层22b是第1膜及第2膜的例子。

[0066]

其次,在绝缘膜21a及各柱状部24上,形成作为层间绝缘膜21的一部分的绝缘膜21b、配线层43、介层插塞42及金属垫41(图8(a))。像这样,制造成为贴合对象的阵列晶圆4。图8(a)示出了成为阵列晶圆4的贴合面s的阵列晶圆4的上表面s2。

[0067]

其次,准备用于电路晶圆3的衬底11,在衬底11上形成晶体管12、层间绝缘膜13、接触插塞31、配线层32、介层插塞33、配线层34、介层插塞35、配线层36、介层插塞37及金属垫38(图8(b))。像这样,制造成为贴合对象的电路晶圆3。图8(b)示出了成为电路晶圆3的贴合面s的电路晶圆3的上表面s1。

[0068]

其次,将电路晶圆3与阵列晶圆4贴合,在电路晶圆3上配置阵列晶圆4(图9(a))。电路晶圆3与阵列晶圆4以晶体管12、积层膜22、柱状部24等夹在衬底11与衬底26之间的方式贴合。通过该贴合,金属垫38与金属垫41相互接合,层间绝缘膜13与层间绝缘膜21相互粘接。

[0069]

其次,通过cpm(chemical mechanical polishing,化学机械抛光)去除衬底26(图9(b))。结果,各柱状部24的半导体层24b露出。

[0070]

其次,在层间绝缘膜23及各柱状部24上形成配线层51的半导体层51a(图10(a))。图10(a)的步骤中所形成的半导体层51a例如是掺杂了p原子的非晶硅层。该半导体层51a以与各柱状部24的半导体层24b相接的方式形成,由此,与各柱状部24的半导体层24b电连接。

[0071]

其次,通过激光退火使半导体层51a退火(图10(b))。结果,作为非晶硅层的半导体层51a变成多晶硅层。

[0072]

之后,在半导体层51a上形成配线层51的金属层51b,在金属层51b上形成钝化膜52(参照图1)。像这样,制造本实施方式的半导体装置。

[0073]

另外,在制造图4所示的比较例的半导体装置时,例如通过图10(b)的步骤的退火使p原子从半导体层51a扩散到通道半导体层24c,而在通道半导体层24c内形成杂质扩散层25。然而,该方法难以使不同柱状部24的杂质扩散层25的位置接近于相同位置。此外,为了抑制退火对金属垫38、41造成不良影响,希望图10(b)的步骤的退火仅进行较短时间。这也会成为使p原子从半导体层51a扩散到通道半导体层24c的操作上的障碍。

[0074]

另一方面,在本实施方式中,另外形成与通道半导体层24c不同的半导体层24b,来代替在通道半导体层24c内形成杂质扩散层25。由此,能够消除类似比较例的半导体装置那样的问题。

[0075]

图11是表示第1实施方式的变化例的半导体装置的制造方法的剖视图。

[0076]

首先,在实施图5(a)~图9(b)的步骤之后,通过湿式蚀刻去除衬底26(图11(a))。结果,各柱状部24的半导体层24b露出。在图11(a)的步骤中,也可以将层间绝缘膜23及存储器绝缘膜24a的一部分和衬底26一起去除。在这种情况下,如图11(a)所示,各柱状部24的半

导体层24b的部分k1从层间绝缘膜23及存储器绝缘膜24a突出。

[0077]

其次,与图10(a)的步骤一样,在层间绝缘膜23及各柱状部24上形成配线层51的半导体层51a(图11(b))。结果,以半导体层51a的多个部分k2向 z方向突出的方式,形成半导体层51a。半导体层51a的这些部分k2分别形成在对应的柱状部24的半导体层24b的部分k1的 z方向。在图11(b)中,该部分k1突出到半导体层51a内。

[0078]

其次,在实施图10(b)的步骤之后,在半导体层51a上形成配线层51的金属层51b,在金属层51b上形成钝化膜52(参照图1)。像这样,制造本变化例的半导体装置。本变化例的半导体装置的构造在包含所述部分k1、k2这一方面,与本实施方式的半导体装置的构造不同。

[0079]

如上所述,本实施方式的半导体装置的各柱状部24除了具备通道半导体层24c以外,还具备半导体层24b。因此,根据本实施方式,能够提高各柱状部24内的半导体层(通道半导体层24c及半导体层24b)的性能。例如,根据本实施方式,能够容易地使不同柱状部24的半导体层24b的位置接近于相同位置,从而能够容易地使不同柱状部24中产生的gidl电流的值接近于相同值。

[0080]

对本发明的若干实施方式进行了说明,但这些实施方式是作为例子提出的,并非意图限定发明的范围。这些新颖的实施方式能以其它各种方式实施,在不脱离发明主旨的范围内,能够进行各种省略、置换、变更。这些实施方式及其变化包含在发明的范围及主旨中,并且包含在权利要求书所记载的发明及其均等范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。