半导体衬底、半导体衬底的制造方法及半导体装置的制造方法

1.相关申请案的引用

2.本技术案基于2020年09月15日申请的在先日本专利申请案第2020-154443号的优先权而主张优先权利益,其全部内容以引用的方式包含于此。

技术领域

3.本实施方式涉及一种半导体衬底、半导体衬底的制造方法及半导体装置的制造方法。

背景技术:

4.在制造半导体器件时,有时使用不形成半导体器件的非成品晶圆(non product wafer)(npw)。另外,已知有一种在半导体衬底上三维配置着存储单元的半导体器件。

技术实现要素:

5.实施方式的发明想要解决的问题在于,提供一种表面积更大的半导体衬底、半导体衬底的制造方法及半导体装置的制造方法。

6.实施方式的半导体衬底具备表面,所述表面具有包含内底面及内壁面的沟槽。内壁面具有凹部,所述凹部具有从沿着所述内壁面的表面的方向到所述沟槽的宽度方向的深度。半导体衬底在内壁面露出。

7.另外,实施方式的半导体衬底的所述内壁面具有多个所述凹部,多个所述凹部沿着所述沟槽的深度方向或所述沟槽的内周,隔开间隔配置。

8.另外,实施方式的半导体衬底还具备半导体层,所述半导体层设置在所述表面的一部分上,沿着所述内壁面延伸。

9.另外,实施方式的半导体衬底还具备第2表面,所述第2表面设置在所述表面的相反侧,具有至少一个包含第2内壁面的第2沟槽。

10.另外,实施方式的半导体衬底是硅晶圆、碳化硅晶圆、玻璃晶圆、石英晶圆、蓝宝石晶圆或化合物半导体晶圆。

11.另外,实施方式的半导体装置的制造方法具备以下步骤:将第1半导体衬底载置到处理室内,所述第1半导体衬底具备第1表面与设置在所述第1表面的膜,且所述膜具有第1沟槽;将所述实施方式的所述半导体衬底也就是第2半导体衬底载置到所述处理室内;及在所述处理室内,同时处理所述第1半导体衬底与所述第2半导体衬底。

12.另外,实施方式的半导体装置的制造方法中的所述膜具有交替积层的第1层与第2层。

13.另外,实施方式的半导体装置的制造方法中的所述处理包含选自由成膜处理、蚀刻处理及改质处理所组成的群中的至少一个处理。

14.另外,实施方式的半导体装置的制造方法将多个所述第2半导体衬底载置到所述

处理室内。

15.另外,实施方式的半导体衬底的制造方法在半导体衬底的表面形成催化剂层,对形成着所述催化剂层的半导体衬底,供给包含氟化氢的第1液体,供给所述第1液体后,供给第2液体,所述第2液体包含氟化氢,且所述氟化氢浓度低于所述第1液体。

16.根据所述实施方式的发明,可提供一种表面积更大的半导体衬底、半导体衬底的制造方法及半导体装置的制造方法。

附图说明

17.图1是半导体晶圆的外观示意图。

18.图2是表示半导体晶圆的构造例的截面示意图。

19.图3是表示半导体晶圆的构造例的俯视示意图。

20.图4是表示半导体晶圆的构造例的俯视示意图。

21.图5是表示区域101与区域102的边界部的俯视示意图。

22.图6是用以说明半导体晶圆的制造方法例的示意图。

23.图7是用以说明半导体晶圆的制造方法例的示意图。

24.图8是用以说明半导体晶圆的制造方法例的示意图。

25.图9是用以说明半导体晶圆的制造方法例的示意图。

26.图10是用以说明半导体晶圆的制造方法例的示意图。

27.图11是表示凹部11c的其它形状例的截面示意图。

28.图12是表示沟槽11的其它形状例的截面示意图。

29.图13是表示沟槽11的其它形状例的截面示意图。

30.图14是表示沟槽11的其它形状例的截面示意图。

31.图15是表示沟槽11的其它形状例的截面示意图。

32.图16是用以说明具备包含图12到图15所示的形状的沟槽11的表面10a的半导体晶圆1的制造方法例的图。

33.图17是用以说明具备包含图12到图15所示的形状的沟槽11的表面10a的半导体晶圆1的制造方法例的图。

34.图18是用以说明具备包含图12到图15所示的形状的沟槽11的表面10a的半导体晶圆1的制造方法例的图。

35.图19是表示半导体晶圆的其它构造例的截面示意图。

36.图20是表示半导体晶圆的其它构造例的截面示意图。

37.图21是表示半导体晶圆的其它构造例的截面示意图。

38.图22是表示用以说明图21所示的半导体晶圆的制造方法例的示意图。

39.图23是表示用以说明图21所示的半导体晶圆的制造方法例的示意图。

40.图24是表示图21所示的半导体晶圆的其它构造例的截面示意图。

41.图25是表示半导体晶圆的其它构造例的截面示意图。

42.图26是表示半导体晶圆的其它构造例的截面示意图。

43.图27是表示半导体晶圆的其它构造例的截面示意图。

44.图28是表示图27所示的半导体晶圆的制造方法例的示意图。

45.图29是表示图27所示的半导体晶圆的制造方法例的示意图。

46.图30是表示图27所示的半导体晶圆的制造方法例的示意图。

47.图31是表示图27所示的半导体晶圆的制造方法例的示意图。

48.图32是表示图27所示的半导体晶圆的制造方法例的示意图。

49.图33是表示半导体晶圆的其它构造例的截面示意图。

50.图34是表示半导体晶圆的其它构造例的截面示意图。

51.图35是表示半导体制造装置的构成例的示意图。

52.图36是表示半导体器件的构造例的示意图。

53.图37是用以说明半导体器件的制造方法例的示意图。

54.图38是用以说明半导体器件的制造方法例的示意图。

55.图39是用以说明半导体器件的制造方法例的示意图。

具体实施方式

56.以下,参考附图对实施方式进行说明。存在附图记述的各构成要件的厚度与平面尺寸的关系、各构成要件的厚度比例等与实物不同的情况。另外,实施方式中,对实质上相同的构成要件附注相同的符号并适当省略说明。

57.《第1实施方式》

58.图1是作为半导体衬底的半导体晶圆的外观示意图。图2是表示半导体晶圆的构造例的截面示意图,表示包含x轴和与x轴及y轴正交的z轴的x-z截面的一部分。

59.图3是表示半导体晶圆的构造例的俯视示意图,表示半导体晶圆中包含x轴和与x轴正交的y轴的x-y平面的一部分。

60.半导体晶圆1是npw,是用于事先评估、测定成膜、蚀刻、其它半导体制造中的诸工艺的晶圆。例如,用于评估、测定以下工艺:使晶圆表面与原料气体反应而形成薄膜的化学气相沉积(cvd,chemical vapor deposition)、原子层沉积(ald,atomic layer deposition)等成膜工艺、或者对晶圆表面供给等离子体而对膜进行蚀刻的化学干蚀刻(cde,chemical dry etch)、对表面供给原料气体而对膜进行蚀刻的原子层蚀刻(ale,atomic layer etch)、供给液体而对膜进行蚀刻的湿蚀刻等蚀刻工艺。或者,也用于它们的再现性试验等。或者,有时利用与形成着半导体器件的晶圆相同的处理室进行处理。半导体晶圆1也可以被称为虚拟晶圆或测试片等。

61.半导体晶圆1包含表面10a及表面10b,所述表面10a在x轴方向及y轴方向上延伸,所述表面10b是表面10a的相反面。表面10a的表面积优选为与形成着半导体器件或者形成中途的半导体晶圆的器件形成面的表面积相同程度。半导体晶圆1的例子包含硅晶圆、碳化硅晶圆、玻璃晶圆、石英晶圆、蓝宝石晶圆、gaas衬底等化合物半导体晶圆等。另外,半导体晶圆1的形状不限定为图1所示的形状,例如也可为具有定向平面的形状。

62.表面10a具有包含至少一个沟槽11的图案。沟槽11包含内壁面11a与内底面11b。半导体晶圆1在内壁面11a及内底面11b露出。设置多个沟槽11的情况下,如图2所示,多个沟槽11沿着表面10a的x轴方向并列配置,沿着表面10a的y轴方向线状延伸。沟槽11的长度方向的长度l例如为4μm以上,优选为40μm以上。沿着x轴方向相邻的沟槽11的间隔例如为0.4μm以上且14μm以下,优选为1μm以下。沿着x轴方向相邻的沟槽11的端部可不沿着y轴方向相互

偏移。

63.另外,沟槽11的形状不限定为线状。沟槽11的形状例如也可为孔状。

64.内壁面11a具有凹部11c。凹部11c露出。多个凹部11c沿着沟槽11的深度方向隔开间隔配置。凹部11c具有从沿着内壁面11a的表面的方向(z轴方向)到沟槽11的宽度方向(x轴方向)的深度。也就是说,内壁面11a沿着深度方向具有凹凸构造。凹部11c的z轴方向的长度(凹部11c的宽度)例如为100nm以上且2000nm以下。凹部11c的x轴方向的长度(凹部11c的深度)例如为10nm以上且200nm以下。

65.沟槽11的纵横比例如为50以上且1750以下。纵横比由图3所示的沟槽11的深度d相对于沟槽11的宽度w的比来定义。沟槽11的宽度w例如为0.4μm以上且14μm以下。沟槽11的深度d例如为20μm以上且半导体晶圆1的厚度以下,沟槽11也可贯通半导体晶圆1。表面10a的表面积与未形成沟槽11时的表面积相比,例如为50倍以上,优选为100倍以上。也就是说,未在表面10b形成沟槽等的情况下,也可以说是表面10b的50倍以上,优选为100倍以上。

66.沟槽11优选为例如距离表面10a的深度d为20μm以上且纵横比为50以上。由此,可以实现扩大表面10a的表面积并且容易去除形成在表面10a的膜的沟槽11。

67.沟槽11可隔着间隔壁12形成。如果沟槽11的长度l、深度d、纵横比变大,那么沟槽11容易坍塌变形。对此,通过设置间隔壁12,使间隔壁12作为梁发挥作用而可支撑沟槽11,所以可抑制沟槽11变形。

68.为了抑制沟槽11变形,间隔壁12优选为在y轴方向上,例如以100μm以上的间隔设置。另外,优选为多个间隔壁12在y轴方向的长度相同。此外,沿着x轴方向相邻的沟槽11的间隔壁12的位置也可以如图2所示,不沿着y轴方向偏移,相邻的沟槽11间的区域经由间隔壁12连接。

69.沟槽11可包含沿着互不相同的方向延伸的多个沟槽。图4是表示半导体晶圆1的构造例的俯视示意图,且表示x-y平面的一部分。图4所示的半导体晶圆1的表面10a包含区域101与区域102。区域101及区域102例如沿着x轴方向及y轴方向交替配置。区域101与区域102的间隔例如为2μm以上。另外,图4示出了形成在表面10a上的多个曝光区域中的1个曝光区域。

70.图5是表示区域101与区域102的边界部的俯视示意图。区域101具有沟槽111,区域102具有沟槽112。多个沟槽111沿着x轴方向并列配置,且沿着y轴方向延伸。多个沟槽112沿着y轴方向并列配置,且沿着x轴方向延伸。另外,沟槽111的延伸方向(长度l方向)与沟槽112的延伸方向(长度l方向)不限定为相互正交的方向,只要为彼此交叉的方向即可。沟槽111及沟槽112包含在沟槽11内。因此,关于沟槽111及沟槽112的其它说明,可适当引用沟槽11的说明。另外,所述表面10a的构造也可以形成在表面10b。

71.如上所述,半导体晶圆1可作为在半导体晶圆1上进行成膜并对此进行评估的测试片使用。或者,也可以作为在半导体晶圆1上进行成膜后进行蚀刻并对此评估的测试片使用。此时,半导体晶圆具有一对具有不同表面积的表面,并且一对表面上的成膜量差别较大,所以容易翘曲。因此,假设在多个沟槽11全部沿着同一方向延伸的情况下,因对一方向施加应力,所以半导体晶圆1的翘曲容易变大。对此,通过使多个沟槽11沿着多个方向延伸,可分散施加应力的方向,从而抑制半导体晶圆1的翘曲。

72.半导体晶圆1可作为测试片重复利用。也就是说,可对半导体晶圆1连续进行成膜

步序或连续进行成膜步序与蚀刻步序。通过设置在沟槽11的内壁面11a的凹部11c,表面积增大,所以即便在连续成膜的情况下,也可以抑制表面积变化,即便在蚀刻的情况下,也可以容易去除膜。

73.如图4所示,表面10a还可以具有区域103。区域103优选为不具有沟槽11的平坦面。通过设为平坦面,区域103可使用最小测定区域比设置在沟槽11间的平坦部大的光谱椭圆仪、x射线光电子能谱(xps,x-ray photoelectron spectroscopy)、荧光x射线分析、傅里叶转换红外光谱仪(ftir,fourier transform infrared spectroscopy)等测定器,例如测定形成在表面10a的膜的厚度、密度、组成。区域103的面积例如可小于区域101的面积或区域102的面积。区域103例如形成在表面10a的多个曝光区域中的各区域。

74.如上所述,半导体晶圆1可通过控制用以扩大表面积的沟槽的形状而实现不易变形的沟槽11。因此,可抑制重复使用半导体晶圆1时的表面积的变化。可提供表面积更大的半导体晶圆。另外,关于所述沟槽11的尺寸,优选为根据要成膜的膜的种类或膜厚而设定。

75.半导体晶圆1例如可使用催化剂辅助蚀刻(metal-assisted chemical etching:mace)制造。mace是通过将在衬底表面形成着催化剂层的衬底浸渍到药液而仅蚀刻与催化剂层接触的区域的技术。

76.图6到图10是用以说明半导体晶圆的制造方法例的图。半导体晶圆的制造方法例具备催化剂层形成步序、蚀刻步序、及催化剂层去除步序。

77.催化剂层形成步序中,如图6所示,在半导体晶圆1的表面10a形成催化剂层2。催化剂层2例如含有金、银、铂、铱、钯等贵金属催化剂。催化剂层2例如可使用cvd法、镀覆法等形成。另外,催化剂层2也可以含有石墨烯等碳材料的催化剂。

78.蚀刻步序中,使半导体晶圆1浸渍到第1蚀刻液。作为第1蚀刻液,例如可使用氢氟酸及过氧化氢溶液的混合液。

79.当使半导体晶圆1浸渍到第1蚀刻液时,在表面10a与催化剂层2的接触部,表面10a的材料(例如硅)溶解到蚀刻液中。通过重复所述反应,如图7所示,大致垂直地蚀刻半导体晶圆1。

80.此外,蚀刻步序中,使半导体晶圆1浸渍到第2蚀刻液。作为第2蚀刻液,例如可使用氢氟酸及过氧化氢溶液的混合液。

81.第2蚀刻液的氢氟酸浓度低于第1蚀刻液的氢氟酸浓度。第1蚀刻液的氢氟酸的浓度优选为5.0质量%以上且20.0质量%以下。第2蚀刻液的氢氟酸的浓度优选为1.0质量%以上且3.0质量%以下。当使半导体晶圆1浸渍到具有所述浓度的第2蚀刻液时,在表面10a与催化剂层2的接触部,表面10a的材料(例如硅)溶解到蚀刻液中。通过重复进行所述反应,如图8所示,大致平行地蚀刻半导体晶圆1。

82.此外,通过交替切换使用第1蚀刻液的mace与使用第2蚀刻液的mace,如图9所示,可形成包含内壁面11a及凹部11c的沟槽11。

83.催化剂层去除步序中,如图10所示,从表面10a去除催化剂层2。催化剂层2例如通过使半导体晶圆1含浸到盐酸与硝酸的混合液(王水)等药液而去除。

84.即便去除催化剂层2,仍会有如图10所示,在半导体晶圆1的内部或表面,稍微残留催化剂层2所含的催化剂原子2a的情况。催化剂原子2a的量相对于去除催化剂层2后的半导体晶圆1的表面积例如为1

×

10

11

atoms/cm2以下。

85.凹部11c的形状例如通过调整催化剂层2的尺寸、第2蚀刻液的氟化氢的浓度、蚀刻时间等参数而控制。例如,图11是表示凹部11c的其它形状例的截面示意图。如图11所示,凹部11c在剖视时可具有v字形状。

86.如上所述,本实施方式中,通过在沟槽11形成凹部11c,可增加半导体晶圆1的表面积。

87.另外,通过使用mace来制造半导体晶圆1,即便在形成凹部11c的情况下,也可以容易形成。

88.《第2实施方式》

89.本实施方式中,对沟槽11的其它形状例进行说明。图12到图15是表示沟槽11的其它形状例的示意图,表示半导体晶圆1的x-y平面的一部分。另外,对于与所述半导体晶圆1的说明相同的部分,可适当引用所述说明。

90.图12所示的沟槽11为线状,沟槽11的内壁面11a具有凹部11c。图13所示的沟槽11为线状,沟槽11的内壁面11a具有俯视时呈v字形状的凹部11c。图14所示的沟槽11为孔状,沟槽11的内壁面11a具有凹部11c。图15所示的沟槽11为孔状,沟槽11的内壁面11a具有俯视时呈v字形状的凹部11c。多个凹部11c各者沿着沟槽11的内周隔开间隔配置。内壁面11a、内底面11b、凹部11c露出。

91.图16到图18是用以说明具备包含图12到图15所示的形状的沟槽11的表面10a的半导体晶圆1的制造方法例的图。半导体晶圆的制造方法例具备催化剂层形成步序、蚀刻步序及催化剂层去除步序。

92.催化剂层形成步序中,如图16所示,在半导体晶圆1的表面10a形成催化剂层2。催化剂层2例如含有金、银、铂、铱、钯等贵金属催化剂。催化剂层2例如可使用cvd法、镀覆法等形成。另外,催化剂层2也可以含有石墨烯等碳材料的催化剂。

93.蚀刻步序中,使半导体晶圆1浸渍到第1蚀刻液。作为第1蚀刻液,例如可使用氢氟酸及过氧化氢溶液的混合液。

94.当使半导体晶圆1浸渍到蚀刻液时,在表面10a与催化剂层2的接触部,表面10a的材料(例如硅)溶解到蚀刻液中。通过重复进行所述反应,如图17所示,大致垂直地蚀刻半导体晶圆1。

95.催化剂层去除步序中,如图18所示,从表面10a去除催化剂层2。催化剂层2例如通过使半导体晶圆1含浸到王水等药液而去除。

96.即便去除催化剂层2,仍会有在半导体晶圆1的内部或表面,稍微残留催化剂层2所含的催化剂原子2a的情况。去除催化剂层2后的半导体晶圆1的内部及表面的催化剂原子2a的面密度例如为1

×

10

11

atoms/cm2以下。

97.如图12到图15所示的形状的凹部11c可通过使用被加工成期望形状的平面形状的催化剂层2蚀刻半导体晶圆1而形成。另外,也可以与第1实施方式同样地,通过交替切换使用第1蚀刻液的mace与使用第2蚀刻液的mace,而形成具有如图2所示的截面形状的凹部11c。

98.如上所述,通过使用mace来制造半导体晶圆1,即便为形成深度d、纵横比较大的沟槽11的情况,也可以容易地形成。

99.如上所述,本实施方式中,通过在沟槽11形成凹部11c,可增加半导体晶圆1的表面

积。

100.本实施方式可与其它实施方式适当组合。

101.《第3实施方式》

102.本实施方式中,对半导体晶圆1的其它构造例进行说明。图19及图20是表示半导体晶圆1的其它构造例的截面示意图,表示x-z截面的一部分。另外,对于与所述半导体晶圆1的说明相同的部分,可适当引用所述说明。

103.图19所示的半导体晶圆1具备设置在表面10a并且具有内壁面11a与内底面11b的沟槽11、及面向内壁面11a及内底面11b设置的多孔质区域11d。多孔质区域11d露出。

104.沟槽11的形状虽未特别限定,但此处作为线状的沟槽进行说明。

105.多孔质区域11d例如为氧化硅膜、含有掺杂碳的氧化硅膜等多孔质膜,在膜中具有多个空孔。空孔的平均直径例如为0.5nm以上。所述多孔质膜以与第2实施方式同样的方法,在半导体晶圆1形成沟槽11后,例如使用涂布法或cvd法形成在表面10a。另外,多孔质区域11d未必为膜状。

106.多孔质区域11d的形状可根据膜厚或形成方法等条件而变化。图20是表示多孔质区域11d的其它形状例的截面示意图。如图20所示,可以由多孔质区域11d填埋沟槽11。

107.如以上所述,本实施方式中,通过在半导体晶圆1形成沟槽11后,在沟槽11进而形成多孔质区域11d,可增加半导体晶圆1的表面积。

108.本实施方式可与其它实施方式适当组合。

109.《第4实施方式》

110.本实施方式中,对半导体晶圆1的其它构造例进行说明。图21是表示半导体晶圆1的其它构造例的截面示意图,表示x-z截面的一部分。另外,对于与所述半导体晶圆1的说明相同的部分,可适当引用所述说明。

111.图21所示的半导体晶圆1具备设置在表面10a并且具有内壁面11a与内底面11b的沟槽11、及面向内壁面11a及内底面11b的多孔质区域11e。内壁面11a、内底面11b、多孔质区域11d露出。沟槽11的形状虽无特别限定,但此处作为线状的沟槽进行说明。

112.多孔质区域11e为设置在内壁面11a及内底面11b的多孔质面。多孔质面的表面具有多个凹部(孔)。多个孔具有5nm以上且100nm以下的平均直径,例如沿着x轴方向延伸。另外,多个孔中的至少一个可从多个沟槽11中的一个贯通到多个沟槽11中的另一个。

113.图22到图24是用以说明图21所示的半导体晶圆的制造方法例的图。半导体晶圆的制造方法例具备第1催化剂层形成步序、第1蚀刻步序、第1催化剂层去除步序、第2催化剂层形成步序、第2蚀刻步序及第2催化剂层去除步序。因第1催化剂层形成步序、第1蚀刻步序、及第1催化剂层去除步序分别与第2实施方式的催化剂层形成步序、蚀刻步序、及催化剂层去除步序相同,所以此处省略说明。

114.第2催化剂层形成步序中,如图22所示,在半导体晶圆1的表面10a形成催化剂层5。催化剂层5例如含有金、银、铂、铱及钯等贵金属催化剂。催化剂层5例如可使用溅镀、cvd法、镀覆法等形成。另外,催化剂层5也可以含有石墨烯等碳材料的催化剂。

115.第2蚀刻步序中,使用mace,使半导体晶圆1浸渍到蚀刻液。作为蚀刻液,例如可使用氢氟酸及过氧化氢溶液的混合液。

116.当使半导体晶圆1浸渍到蚀刻液时,在表面10a与催化剂层5的接触部,表面10a的

材料(例如硅)溶解到蚀刻液中。通过重复进行所述反应,如图23所示,半导体晶圆1被蚀刻而形成多孔质区域11e。另外,经蚀刻的半导体晶圆1的表面10a包含催化剂层5的残留物5a。

117.在第2催化剂层去除步序中,如图24所示,从表面10a去除催化剂层5的残留物5a。催化剂层5例如通过使半导体晶圆1含浸到王水等药液而去除。另外,也可以利用所述药液进一步蚀刻多孔质区域11e。此时,与第1实施方式同样地,存在催化剂层5的催化剂原子残存的情况。

118.如上所述,本实施方式中,通过在半导体晶圆1形成沟槽11后,在沟槽11进而形成多孔质区域11e,可增加半导体晶圆1的表面积。

119.本实施方式可与其它实施方式适当组合。

120.《第5实施方式》

121.本实施方式中,对半导体晶圆1的其它构造例进行说明。图25是表示半导体晶圆1的其它构造例的截面示意图,表示x-z截面的一部分。另外,对于与所述半导体晶圆1的说明相同的部分,可适当引用所述说明。

122.图25所示的半导体晶圆1的表面10a具备沟槽11。另外,对于沟槽11的说明,可适当引用所述实施方式的沟槽11的说明。

123.沟槽11具有内壁面11a、内底面11b、设置在内底面11b的柱状部11b1、及设置在内底面11b的柱状部11b2。内壁面11a在与内底面11b交叉的方向(z轴方向)具有高度。沟槽11的平面形状虽未特别限定,但例如为线状。沟槽11的x轴方向的宽度虽无特别限定,但例如为100μm以上。

124.柱状部11b1在z轴方向延伸。柱状部11b1在z轴方向的高度低于内壁面11a。图25表示多个柱状部11b1。柱状部11b1的平面形状虽无特别限定,但例如为线状。相邻的柱状部11b1的x轴方向的间隔虽无特别限定,但例如为10μm以上且小于100μm。

125.柱状部11b2在z轴方向延伸。柱状部11b2在z轴方向的高度低于柱状部11b1。图25表示多个柱状部11b2。多个柱状部11b2设置在柱状部b1间。柱状部11b2的平面形状虽无特别限定,但例如为线状。相邻的柱状部11b2的x轴方向的间隔虽无特别限定,但例如为1μm以上且小于10μm。

126.沟槽11、柱状部11b1及柱状部11b2各者例如可与第2实施方式同样地使用mace而形成。例如,通过使用具有第1宽度的催化剂层2的mace形成第1沟槽,通过使用具有比第1宽度窄的第2宽度的催化剂层2的mace,在第1沟槽的内底面形成第2沟槽,通过使用具有比第2宽度窄的第3宽度的催化剂层2的mace,在第2沟槽的内底面形成第3沟槽。

127.如上所述,本实施方式中,在半导体晶圆1的沟槽11形成多个柱状部(柱状部11b1、柱状部11b2),由此可增加半导体晶圆1的表面积。

128.本实施方式可与其它实施方式适当组合。

129.《第6实施方式》

130.本实施方式中,对半导体晶圆1的其它构造例进行说明。图26是表示半导体晶圆1的其它构造例的截面示意图。另外,对于与所述半导体晶圆1的说明相同的部分,可适当引用所述说明。

131.图26所示的半导体晶圆1具备:表面10a,具有包含内壁面11a与内底面11b的沟槽11;及半导体层6a,设置在表面10a上。内壁面11a、内底面11b、半导体层6a露出。沟槽11的形

状虽无特别限定,但此处作为线状沟槽进行说明。半导体层6a例如设置在表面10a中除沟槽11以外的区域,且沿着内壁面11a延伸。

132.半导体层6a例如为磊晶层,通过使与半导体晶圆1相同的材料(例如硅)在表面10a上磊晶生长而形成。如图26所示,有在半导体层6a与半导体晶圆1的表面10a之间存在界面的情况。

133.如上所述,本实施方式中,可通过在半导体晶圆1的表面10a上形成半导体层6a而扩大内壁面11a,所以可增加半导体晶圆1的表面积。

134.本实施方式可与其它实施方式适当组合。

135.《第7实施方式》

136.本实施方式中,对半导体晶圆1的其它构造例进行说明。图27是表示半导体晶圆1的其它构造例的截面示意图。另外,对于与所述半导体晶圆1的说明相同的部分,可适当引用所述说明。

137.图27所示的半导体晶圆1具备:表面10a,具有包含内壁面11a与内底面11b的沟槽11;及半导体层6b,设置在表面10a上。内壁面11a、内底面11b的一部分、半导体层6b露出。沟槽11的形状虽无特别限定,但此处作为线状的沟槽进行说明。

138.半导体层6b设置在内底面11b的一部分上。此时,在半导体层6b与内壁面11a之间形成沟槽11f。

139.图28到图32是用以说明图27所示的半导体晶圆的制造方法例的图。半导体晶圆的制造方法例具备催化剂层形成步序、第1蚀刻步序、催化剂层去除步序、第1成膜步序、第2蚀刻步序、第2成膜步序、第3蚀刻步序、及第4蚀刻步序。催化剂层形成步序、第1蚀刻步序及催化剂层去除步序分别与第2实施方式的催化剂层形成步序、蚀刻步序及催化剂层去除步序相同,所以此处省略说明。

140.第1成膜步序中,如图28所示,在半导体晶圆1的表面10a形成膜7。膜7形成在表面10a中除沟槽11以外的区域、内壁面11a及内底面11b。膜7优选为包含与半导体晶圆1的材料的蚀刻选择比较高的材料,例如含有氧化硅、氮化硅、氮氧化硅等材料。膜7例如可使用溅镀、cvd法、镀覆法等形成。

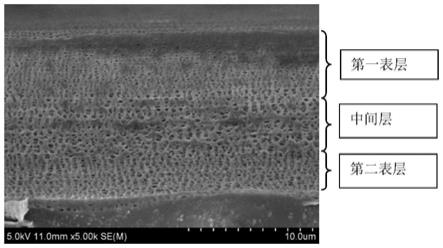

141.第2蚀刻步序中,如图29所示,利用反应性离子蚀刻等蚀刻法局部蚀刻膜7,由此使表面10a中除沟槽11以外的区域与内底面11b露出。膜7的一部分沿着内壁面11a残存。

142.第2成膜步序中,如图30所示,在半导体晶圆1的表面10a形成膜8。膜8形成在露出的表面10a中除沟槽11以外的区域、膜7上及内底面11b上。膜8例如为硅膜。膜8例如使用溅镀法、cvd法、镀覆法等形成。

143.第3蚀刻步序中,如图31所示,利用反应性离子蚀刻或湿蚀刻等蚀刻局部蚀刻膜8,由此使膜7的残存物的上端露出并且形成半导体层6。

144.第4蚀刻步序中,如图32所示,利用湿蚀刻等蚀刻法蚀刻膜7的残存物,由此去除面向内壁面11a的膜7的残存物。由此,可形成半导体层6b。

145.如上所述,本实施方式中,通过在半导体晶圆1的表面10a上形成半导体层6b,进而形成沟槽11f,可增加半导体晶圆1的表面积。

146.本实施方式可与其它实施方式适当组合。

147.《第8实施方式》

148.本实施方式中,对半导体晶圆1的其它构造例进行说明。图33是表示半导体晶圆1的其它构造例的截面示意图。另外,对于与所述半导体晶圆1的说明相同的部分,可适当引用所述说明。

149.图33所示的半导体晶圆1具备:表面10a,具有沟槽11a;表面10b,设置在表面10a的相反侧并且具有沟槽11b;及斜面10c,从表面10a或表面10b延伸并且具有沟槽11c。沟槽11a、沟槽11b、沟槽11c的形状虽无特别限定,但此处作为具有露出的内壁面与内底面的线状沟槽进行说明。

150.本实施方式的半导体晶圆1不限于图33所示的构造。图34是表示半导体晶圆1的其它构造例的截面示意图。另外,对于与所述半导体晶圆1的说明相同的部分,适当引用所述说明。

151.图34所示的半导体晶圆1具备:第1半导体晶圆1a,具有包含沟槽11a的表面10a;及第2半导体晶圆1b,具有包含沟槽11b的表面10b。第1半导体晶圆1a及第2半导体晶圆1b例如通过热接合而接合。沟槽11a、沟槽11b的形状虽无特别限定,但此处作为线状的沟槽进行说明。

152.如上所述,本实施方式中,通过在多个表面形成沟槽11可增加半导体晶圆1的表面积。

153.本实施方式可与其它实施方式适当组合。

154.《第9实施方式》

155.本实施方式中,作为半导体晶圆的使用方法例,使用图35到图38,对在半导体装置的制造步序中将所述半导体晶圆1作为虚拟晶圆使用的例子进行说明。

156.图35是表示半导体制造装置的构成例的示意图。图35表示lp-cvd(low pressure chemical vapor deposition:lp-cvd,低压化学气相沉积)装置的构成例。图35所示的半导体制造装置20具备处理室21、用以将原料气体22供给到处理室21内的配管23。lp-cvd装置20还具备未图示的真空泵、加热器、排气系统、电源、控制电路等。

157.存在以下情况:将作为虚拟晶圆的半导体晶圆1和形成着半导体器件或者形成中途的半导体晶圆也就是器件晶圆9一起搬入到同一处理室21内,同时处理半导体晶圆1与器件晶圆9。此时的半导体装置的制造方法例具备将器件晶圆9载置到处理室21内的步骤、将实施方式的半导体晶圆1载置到处理室21内的步骤、及在处理室21内同时处理器件晶圆9与半导体晶圆1的步骤。另外,器件晶圆9与半导体晶圆1可在相同的步骤或不同的步骤载置到处理室21内。

158.图35中,示出了如下例子:在处理室21内处理多个器件晶圆9时,将至少1个半导体晶圆1与多个器件晶圆9一起载置到处理室21内,同时进行成膜处理。半导体晶圆1只要载置至少1片以上即可,但优选如图35所示载置多片。另外,优选如图35所示,半导体晶圆1至少配置到处理室21内的上部或下部区域。

159.此处,对器件晶圆9的构造例进行说明。形成在器件晶圆9的半导体器件例如为三维nand型闪存。以下,对制造三维nand型闪存时的成膜步序进行说明。

160.图36是表示半导体器件的构造例的示意图。图36所示的半导体器件具备:核心绝缘膜91、半导体通道层92、包含穿遂绝缘膜931、电荷储存层932及阻挡绝缘膜933的存储膜93、电极材料层94、金属层95、及绝缘层96。电极材料层94作为栅极电极(字线)发挥作用。核

心绝缘膜91、半导体通道层92、存储膜93形成在存储孔h内,构成存储单元。阻挡绝缘膜933例如为sio2膜(氧化硅膜)。电荷储存层932例如为sin膜(氮化硅膜)。穿遂绝缘膜931例如为包含sio2膜与sion膜(氮氧化硅膜)的积层膜。半导体通道层92例如为多晶硅层。核心绝缘膜91例如为sio2膜。电极材料层94、金属层95及绝缘层96分别为例如w层(钨层)、tin膜(氮化钛膜)及al2o3膜(氧化铝膜)。所述情况下,金属层95作为所述电极层内的势垒金属层发挥作用,绝缘层96与所述阻挡绝缘膜933一起作为阻挡绝缘膜发挥作用。

161.接着,使用图37、图38及图39对图36所示的半导体器件的制造方法例进行说明。图37中,在硅晶圆等半导体晶圆90上形成交替积层多个牺牲层97与多个绝缘层98而成的积层膜,在所述牺牲层97及绝缘层98内,设置着作为沟槽的存储孔h。牺牲层97是之后形成电极材料层的区域。存储孔h是之后形成存储膜93的区域。

162.半导体晶圆1例如用于半导体器件制造时的存储膜93、半导体通道层92、核心绝缘膜91的形成、或电极材料层94、金属层95、绝缘层96的形成、及包含构成存储孔h侧面的牺牲层97、绝缘层98的所述薄膜的改质处理、蚀刻处理。

163.存储膜93的形成是通过以下形成的:将器件晶圆9搬入到处理室21内,在存储孔h内依次成膜阻挡绝缘膜933、电荷储存层932、穿遂绝缘膜931,所述器件晶圆9的状态为在将图37所示的多个牺牲层97与多个绝缘层98交替积层的积层体上形成着存储孔h。

164.金属层95及绝缘层96的形成是通过以下形成的:形成存储膜93后,如图38所示,去除多个牺牲层,将在多个绝缘层98间具有空腔c的器件晶圆9搬入到处理室21内,如图39所示,在空腔c内依次成膜绝缘层96、金属层95及电极材料层94。(将此称为替换步序)。

165.改质处理包含:例如在图37及图38的牺牲层97及绝缘层98、阻挡绝缘膜933、电荷储存层932、穿遂绝缘膜、半导体通道层92的形成步序中,在形成各层或膜后或者形成中途,利用含氧气体进行处理所引起的氧化、使用氨气等含氮气体的气相处理所引起的氮化、进行热处理所引起的结晶化。另外,包含以下处理:在形成层或膜厚后,形成包含硼、磷及金属等期望杂质的牺牲层,通过进行热处理使杂质扩散到目标层或膜,其后,蚀刻去除牺牲膜。另外,对于电极材料层94、金属层95、绝缘层96也同样。

166.蚀刻处理包含处理:例如对图37的牺牲层97及绝缘层98、图38中形成的阻挡绝缘膜933、电荷储存层932、穿遂绝缘膜、半导体通道层92各者,在形成层或膜后,利用包含氟、氯、溴等卤素的蚀刻气体使层或膜薄化。另外,对于图39的电极材料层94、金属层95、绝缘层96也同样。

167.在任何一个例子中,均将至少1片半导体晶圆1和多个器件晶圆9一起搬入到处理室21内,进行同样的处理。由此,在处理室21内的特定位置无法获得期望的处理结果的情况下,可使用半导体晶圆1作为虚拟晶圆。另外,可进行多个处理。

168.半导体晶圆1如上所述,以表面积增大的方式形成着多个沟槽11。因此,成为具有与器件晶圆9相同程度的表面积的虚拟晶圆。因此,例如可进一步减少因表面积差引起的处理室21内的成膜不均,可进一步提高器件晶圆9间或器件晶圆9面内的膜厚、膜的组成、膜密度等的均匀性。也就是说,能制造可靠性进一步提高的半导体器件。

169.另外,因半导体晶圆1可作为虚拟晶圆使用,所以半导体纯度可低于器件晶圆9。因此,半导体晶圆1可具有比器件晶圆9更低的电阻率及更高的杂质浓度。

170.另外,半导体晶圆1的沟槽11的深度(z轴方向长度)大于形成在器件晶圆9的存储

孔mh的深度(z轴方向长度)。

171.另外,在本使用方法例中,以lp-cvd装置为例进行了说明,但也可以在其它半导体制造装置中应用半导体晶圆1。另外,半导体器件不限定于三维nand(not and,与非)型闪存,也可以应用其它半导体器件。

172.说明了本发明的若干实施方式,但所述实施方式是作为例子提出的,并不意图限定发明范围。所述新颖的实施方式可以其它各种方式实施,可在不脱离发明主旨的范围内进行各种省略、替换、变更。所述实施方式及其变化包含在发明范围或主旨内,并且包含在权利要求书所记载的发明及其均等的范围内。

173.以下附记基于所述实施方式的技术方案(clauses)。

174.(技术方案1)

175.一种半导体衬底,其具备表面,所述表面具有包含内底面及内壁面的沟槽;

176.所述内壁面具有凹部,所述凹部具有从沿着所述内壁面的表面的方向到所述沟槽的宽度方向的深度;

177.所述半导体衬底在所述内壁面露出。

178.(技术方案2)

179.根据技术方案1所述的半导体衬底,其中所述内壁面具有多个所述凹部,

180.多个所述凹部沿着所述沟槽的深度方向或所述沟槽的内周隔开间隔配置。

181.(技术方案3)

182.一种半导体衬底,其具备:

183.表面,具有包含内底面与内壁面的沟槽;及

184.多孔质区域,面向所述内底面及所述内壁面设置。

185.(技术方案4)

186.一种半导体衬底,其具备:

187.内底面;

188.内壁面,在与所述内底面交叉的第1方向具有高度;及

189.柱状部,设置在所述内底面,在所述第1方向延伸,在所述第1方向上的高度低于所述内壁面;

190.所述半导体衬底在所述内壁面露出。

191.(技术方案5)

192.根据技术方案1所述的半导体衬底,其还具备半导体层,所述半导体层设置在所述表面的一部分上,沿着所述内壁面延伸。

193.(技术方案6)

194.根据技术方案1所述的半导体衬底,其还具备第2表面,所述第2表面设置在所述表面的相反侧,具有至少一个包含第2内壁面的第2沟槽。

195.(技术方案7)

196.根据技术方案1所述的半导体衬底,其是硅晶圆、碳化硅晶圆、玻璃晶圆、石英晶圆、蓝宝石晶圆或化合物半导体晶圆。

197.(技术方案8)

198.一种半导体装置的制造方法,其具备以下步骤:

199.将第1半导体衬底载置到处理室内,所述第1半导体衬底具备第1表面与设置在所述第1表面的膜,且所述膜具有第1沟槽;

200.将技术方案1所述的半导体衬底也就是第2半导体衬底载置到所述处理室内;及

201.在所述处理室内,同时处理所述第1半导体衬底与所述第2半导体衬底。

202.(技术方案9)

203.根据技术方案8所述的半导体装置的制造方法,其中所述膜具有交替积层的第1层与第2层。

204.(技术方案10)

205.根据技术方案8所述的半导体装置的制造方法,其中所述处理包含选自由成膜处理、蚀刻处理及改质处理所组成的群中的至少一个处理。

206.(技术方案11)

207.根据技术方案8所述的半导体装置的制造方法,其中将多块所述第2半导体衬底载置到所述处理室内。

208.(技术方案12)

209.一种半导体衬底的制造方法,

210.在半导体衬底的表面形成催化剂层,

211.对形成着所述催化剂层的半导体衬底,供给包含氟化氢的第1液体,

212.供给所述第1液体后,供给第2液体,所述第2液体包含氟化氢,且所述氟化氢浓度低于所述第1液体。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。