1.本发明涉及波形发生器技术领域,具体地说是一种高速信号任意发生器。

背景技术:

2.信号源有很多种,包括正弦波信号源,函数发生器、脉冲发生器、扫描发生器、任意波形发生器、合成信号源等。一般来讲任意波形发生器,是一种特殊的信号源,综合具有其它信号源波形生成能力,因而适合各种仿真实验的需要。

3.任意波形发生器是仿真实验的最佳仪器,任意波形发生器是信号源的一种,它具有信号源所有的特点。我们传统都认为信号源主要给被测电路提供所需要的已知信号(各种波形),然后用其它仪表测量感兴趣的参数。可见信号源在电子实验和测试处理中,并不测量任何参数而是根据使用者的要求,仿真各种测试信号,提供给被测电路,以达到测试的需要。

4.基于上述分析,如何提供一种任意信号发生器,通过该任意信号发生器将服务器或上位机下发的数字信号转换为模拟信号并输出,是需要解决的技术问题。

技术实现要素:

5.本发明的技术任务是针对以上不足,提供一种高速信号任意发生器,来解决如何提供一种任意信号发生器,通过该任意信号发生器将服务器或上位机下发的数字信号转换为模拟信号并输出的问题。

6.本发明的一种高速信号任意发生器,包括:

7.pxie接口,所述pxie接口用于与服务器或上位机电连接,接收服务器或上位机下发的任意波形数据;

8.fpga芯片,所述fpga芯片与所述pxie接口电连接,用于对所述任意波形数据进行翻译,得到翻译后波形数据;

9.dac芯片,所述dac芯片与所述fpga芯片电连接,用于对翻译后波形数据进行数模转换,得到模拟信号;

10.dac后端电路,所述dac后端电路与所述fpga芯片电连接,用于对模型信号进行放大滤波处理,得到处理后模拟信号;

11.sma端子,所述dac后端电路与所述sma端子电连接,用于输出处理后模拟信号;

12.时钟电路,所述时钟电路的输入端与所述pxie接口电连接,用于从pxie 接口获取两路参考时钟,并用于对两路参考时钟进行pll锁相后,分别为所述dac芯片和fpga芯片提供同步时钟。

13.作为优选,所述时钟电路具有一个输入端和两个输出端,输入端与所述 pxie接口电连接,用于从pxie接口获取两路参考时钟,一个输出端与所述 sam端子连接,用于为其它板卡提供参考时钟,另一个输出端与fpga芯片电连接,用于为fpga芯片和dac芯片提供同步时钟。

14.作为优选,所述同步时钟电路包括:

15.时钟buffer,所述时钟buffer的输入端与所述pxie芯片电连接,用于接收pxie芯片提供的第一路参考时钟,并将第一路参考时钟以多路的形式输出;

16.二选一开关,所述二选一开关的输入端分别与所述pxie芯片和所述时钟buffer电连接,所述二选一开关的输出端与所述sma端子电连接,用于二选一的将第一路参考时钟和第二路参考时钟中的一路参考时钟通过sma 端子提供至其它板卡;

17.时钟缓冲器,所述时钟缓冲器与所述时钟buffer电连接,并与所述fpga 芯片电连接,用于为fpga芯片提供同步时钟。

18.作为优选,所述dac芯片配置有spi接口和jesd接口,

19.所述spi接口作为功能配置接口与所述fpga芯片电连接,所述fpga 芯片通过spi接口配置dac芯片的功能;

20.所述jesd接口作为数据交互接口与所述fpga芯片电连接,通过jesd 接口所述dac芯片与所述fpga芯片进行高速数字交互。

21.更优的,还包括内存芯片,所述内存芯片至少一个,并均与fpga芯片电连接。

22.作为优选,内存芯片为ddr4内存芯片。

23.更优的,还包括flash芯片,所述flash芯片至少一个,并均与fpga 芯片电连接。

24.作为优选,所述flash芯片为spi flash芯片。

25.更优的,还包括电源/管理接口,所述电源/管理接口与所述fpga芯片电连接,用于为fpga芯片提供电能。

26.本发明的一种高速信号任意发生器具有以下优点:通过pxie接口与服务器或上位机交互,fpga芯片对波形数据翻译后,由dac芯片将数字信号转换为模拟信号,并通过dac后端电路对模拟信信号放大滤波处理,同时,通过时钟电路现对pxie接口的两路参考时钟进行pll锁相后,分别为dac芯片和fpga 芯片提供同步时钟,该发生器实现了任意波形的转换,且该结构设计合理、结构简单,具有很好的推广使用价值。

附图说明

27.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域的普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

28.下面结合附图对本发明进一步说明。

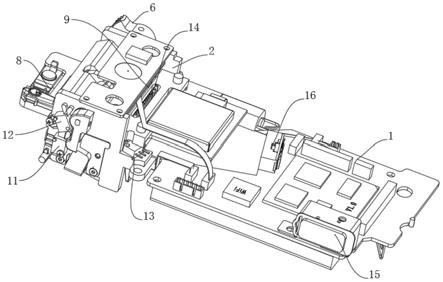

29.图1为实施例一种高速信号任意发生器的组成原理框图;

30.图2为实施例一种高速信号任意发生器的内存芯片配置;

31.图3为实施例一种高速信号任意发生器的电源网络配置;

32.图4为实施例一种高速信号任意发生器中dac芯片的结构框图;

33.图5为实施例一种高速信号任意发生器中ad9163的jesd204b接口支持的 subclass 1的架构图;

34.图6为实施例一种高速信号任意发生器中时钟电路的原理框图;

35.图7为实施例一种高速信号任意发生器中dac与后端模拟电路部分。

具体实施方式

36.下面结合附图和具体实施例对本发明作进一步说明,以使本领域的技术人员可以更好地理解本发明并能予以实施,但所举实施例不作为对本发明的限定,在不冲突的情况下,本发明实施例以及实施例中的技术特征可以相互结合。

37.本发明实施例提供一种高速信号任意发生器,用于解决如何提供一种任意信号发生器,通过该任意信号发生器将服务器或上位机下发的数字信号转换为模拟信号并输出的技术问题。

38.实施例:

39.本发明一种高速信号任意发生器,包括pxie接口、fpga芯片、dac芯片、 sma端子和时钟电路,pxie接口用于与服务器或上位机电连接,接收服务器或上位机下发的任意波形数据;fpga芯片与所述pxie接口电连接,用于对所述任意波形数据进行翻译,得到翻译后波形数据;dac芯片与所述fpga芯片电连接,用于对翻译后波形数据进行数模转换,得到模拟信号;dac后端电路与 fpga芯片电连接,用于对模型信号进行放大滤波处理,得到处理后模拟信号; dac后端电路与所述sma端子电连接,用于输出处理后模拟信号;时钟电路的输入端与所述pxie接口电连接,用于从pxie接口获取两路参考时钟,并用于对两路参考时钟进行pll锁相后,分别为所述dac芯片和fpga芯片提供同步时钟。

40.其中,时钟电路具有一个输入端和两个输出端,输入端与所述pxie接口电连接,用于从pxie接口获取两路参考时钟,一个输出端与所述sam端子连接,用于为其它板卡提供参考时钟,另一个输出端与fpga芯片电连接,用于为 fpga芯片和dac芯片提供同步时钟。

41.本实施例设计参数为:

42.量程范围:

±

1.5v

43.输出阻抗:50ω

44.采样率:6-12gsa/s

45.有效带宽≥300mhz

46.采样精度:16bits

47.输出端子:sma

48.通道:4通道

49.pxie接口包含pcie协议,数据传输部分使用其中的pcie。

50.使用赛灵思xcku060规格的fpga芯片,通过pxie x8 gen2的接口与服务器或其他上位机交互。上位机下达任意波形数据信息通过fpga翻译后通过dac转为模拟信号,再通过后端电路处理后输出。

51.dac芯片采用adi的ad9163,结构如图2所示,fpga通过spi配置其相关功能,通过jesd204b接口进行高速数字数据交互。

52.dac后端电路,通过放大电路调整滤波后输出到sma端子输出。

53.ad9163的jesd204b接口支持subclass 0and subclass 1两种子类架构,本实施例按照图3所示的subclass 1,同步时钟电路包括时钟buffer、二选一开关、时钟缓冲器等,时钟buffer选用sl 18861d1,其输入端与pxie芯片电连接,用于接收pxie芯片提供的第一路参考时钟,并将第一路参考时钟以多路的形式输出;二选一开关选用hsma2-30r ,其输入端分别与pxie 芯片和时钟buffer电连接,二选一开关的输出端与sma端子电连接,用于二选

一的将第一路参考时钟和第二路参考时钟中的一路参考时钟通过sma 端子提供至其它板卡;时钟缓冲器选用hmc7044,其与时钟buffer电连接,并与fpga芯片电连接,用于为fpga芯片提供同步时钟。该时钟设计如图 4所示。

54.pxie接口传入10m参考时钟和100m参考时钟,通过二选一开关由sma 端子输出供其他板卡参考使用。10m时钟通过缓冲器分别和10m的晶振时钟进入hmc7044时钟发生器芯片中,作为其同步时钟。时钟同步后,按照 jesd204b接口时钟规范分别为四路dac和fpga提供时钟。

55.如图5所示,fpga系统的配置有两个2g ddr4内存,并配置有双spiflash。

56.电源部分配置如图6所示,实际测试整体功耗在25w左右,fpga安装参考设计的散热器即可,dac添加小的散热器即可,风冷散热。

57.时钟部分,根据pxie的协议要求,10m与100m时钟用来做同步时钟使用,时钟发生器经过pll锁相后分别给dac和fpga提供时钟,做同源时钟设计,按照jesd204b接口subclass 1模式做时钟设计,整体拓扑参考上面拓扑所述。

58.dac后端输出为电流源输出,后端模拟输出部分如图7所示,差分输出经过上拉后转换为电压信号,再经过变压器t1后通过ac耦合的方式由j32 端子对外输出。

59.本实施例中fpga芯片采用用赛灵思xcku060规格的fpga,它有多个高速接口,支持pcie、jesd204b等协议。fpga作为介于服务器和dac 芯片之间的桥梁,通过pcie总线将来自服务器的波形信号数据处理后通过 dac芯片中jesd204b接口交于dac进行数模信号转换。

60.上文通过附图和优选实施例对本发明进行了详细展示和说明,然而本发明不限于这些已揭示的实施例,基与上述多个实施例本领域技术人员可以知晓,可以组合上述不同实施例中的代码审核手段得到本发明更多的实施例,这些实施例也在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。