1.本发明涉及通讯技术领域,特别是涉及一种逗号检测与字节对齐的校正方法以及校正系统。

背景技术:

2.在采用8b/10b编解码工作模式的高速串行接收器中(如pcie、usb、jesd204b/c等),高速的串行数据经过串并转换后的数据并不一定是正确的,需要一个对齐电路来校正字节数据。通常会采用一个逗号检测与字节对齐(comma detection andword alignment)电路来持续检测逗号码/28.5/(0011111010或1100000101),从而达到识别字节边缘并校正字节的目的。目前,cdwa电路被集成到了数字协议控制器一端,使之可以工作在低频率时钟下,但增加了硬件资源占有量。。

3.现有技术的一个典型的cdwa电路主要包括:数据缓存模块,逗号检测模块,字节对齐模块;如图6所示,数据缓存模块包含了两组位宽为10的寄存器来分别存储当前时钟周期和上一个时钟周期的10bits数据,在存储的20bits的数据中,至少包含一个完整的逗号码,而cdwa的逗号检测模块,主要由10个逗号码阵列构成;开始工作时,从存储的20bits数据的最低有效位开始,依次取出10bits数据输入到逗号检测模块,与其中的逗号码阵列进行对比,从而找出其中的逗号码,字节对齐模块则根据逗号检测模块得到的比对结果,获知一个正确的逗号码的起始位置。

4.但本技术发明人在实现本技术实施例中发明技术方案的过程中,发现上述技术至少存在如下技术问题:

5.在数据传输时,逗号检测模块要持续的将接收到的数据与逗号阵列中的逗号码进行比对,这无疑是逗号检测与字节对齐电路中主要的功耗产生部分,并且功耗也比较大,除此之外,在逗号检测模块中包含10个逗号检测阵列,这也将消耗大量的硬件资源,进而占用较大的面积资源。

6.基于此,本发明设计了一种逗号检测与字节对齐的校正方法以及校正系统,以解决上述问题。

技术实现要素:

7.为了解决目前8b/10b编解码工作模式的高速串行接收器的逗号检测与字节对齐电路所存在的功耗高、面积大等技术问题,本发明的目的是提供一种逗号检测与字节对齐的校正方法以及校正系统。

8.为了实现上述目的,本发明采用如下技术方案:

9.一种逗号检测与字节对齐的校正方法,包括如下步骤:

10.步骤一、存储工作电路的输入数据;

11.步骤二、按照预定条件将采集到的存储数据在逗号码阵列进行低翻转率下的完全匹配数据检测;

12.步骤三、将逗号码阵列检测获得的字节边沿结果进行字节数据的校正。

13.优选的,所述低功耗数据检测包括:

14.将存储数据在逗号阵列1中从最低有效位开始依次采样数据,并与逗号阵列1做逻辑运算,判断是否与逗号阵列1中的数据相匹配,若匹配,则将数据与逗号码进行完全匹配运算。

15.优选的,所述数据与逗号码的完全匹配运算包括:

16.将逗号阵列1中的逻辑运算结果传送至逗号阵列2中进行完全匹配运算,其中,逗号阵列2位于逗号阵列1之后。

17.优选的,所述逗号阵列1为码长为6bits的逗号码组成的逗号码阵列。

18.优选的,所述逗号码阵列包括6

×

10个同或逻辑门。

19.优选的,所述逗号阵列2为与逗号阵列1相同码长的完整的逗号码。

20.优选的,所述字节数据的校正包括:

21.将字节边沿结果传送给字节对齐电路的相应数据位处,并取出正确的字节数据。

22.一种逗号检测与字节对齐的校正系统,其特征在于,包括:

23.数据缓存模块,所述数据缓存模块用于存储工作电路中的输入数据;

24.逗号码检测模块,所述逗号码检测模块用于将存储数据在逗号码阵列中进行低翻转率的完全匹配检测,其中,逗号码阵列包括对存储数据最低有效位开始依次采样数据并进行逻辑运算的逗号阵列1、以及确保逗号阵列1运算结果数据与逗号码完全匹配运算的逗号阵列2;

25.字节对齐电路模块,所述字节对齐电路模块用于将字节边沿在对应的数据位处取出正确的字节数据;以及

26.字节传输模块,所述字节传输模块用于将逗号码阵列获得的字节边沿传送至字节对齐电路模块。

27.本发明实施例中提供的一个或多个技术方案,至少具有如下技术效果或优点:

28.1、本发明通过控制逗号码的位宽来实现对翻转率的最优解,不仅保证了正常检测逗号码以及对字节边沿的校正,而且实现了整个逗号码阵列的功耗最低化,从而降低了逗号检测与字节对齐电路的功耗与面积;

29.2、本发明通过在逗号阵列1末端对逗号阵列2的添加,保证了结果数据与逗号码的完全匹配性;

30.综上所述,本发明具有逗号检测与字节对齐的校正功耗低、字节数据校正准确等优点。

附图说明

31.以下结合附图和具体实施方式来进一步详细说明本发明:

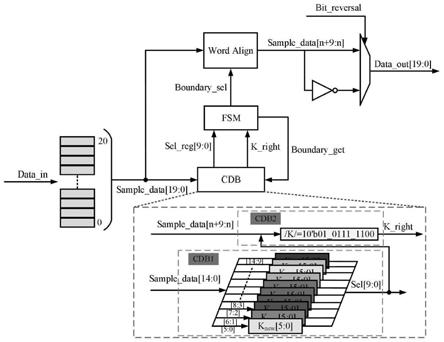

32.图1为本发明逗号检测与字节对齐电路构架图;

33.图2为本发明不同位宽的逗号检测与字节对齐电路与功耗之间的关系图;

34.图3为本发明逗号检测与字节对齐电路的工作时序图;

35.图4为本发明逗号码阵列工作的示意图;

36.图5为本发明不同位宽的逗号检测与字节对齐电路所消耗的fpga硬件资源的表

图;

37.图6为现有技术中逗号检测与字节对齐电路结构图。

具体实施方式

38.以下由特定的具体实施例说明本发明的实施方式,熟悉此技术的人士可由本说明书所揭露的内容轻易地了解本发明的其他优点及功效。

39.实施例一

40.请参阅图1至图5。本发明提供一种技术方案:一种逗号检测与字节对齐的校正方法,包括如下步骤:

41.步骤一、存储工作电路的输入数据;

42.步骤二、按照预定条件将采集到的存储数据在逗号码阵列进行低翻转率下的完全匹配数据检测;

43.步骤三、将逗号码阵列检测获得的字节边沿结果进行字节数据的校正。

44.通过上述步骤不难发现,传统的逗号检测及字节对齐运算过程中,电路被继承到数字协议控制器一端,使之可以工作在低频率时钟下,但增加了硬件资源占有量。

45.在本发明中,主要针对面向8b/10b编解码工作模式的高速串行接收器的逗号检测与字节对齐电路,并且通过利用本发明的逗号码阵列对采集到的存储数据在低翻转率状态下完成检测,不仅可以实现对逗号码的检测以及对字节边沿的校正,还保证了检测工作在低功耗和面积下进行。

46.为了更好的完成在低功耗状态下完成检测工作,如图1和3所示,所述低功耗数据检测包括:

47.将存储数据在逗号阵列1中从最低有效位开始依次采样数据,并与逗号阵列1做逻辑运算,判断是否与逗号阵列1中的数据相匹配,若匹配,则将数据与逗号码进行完全匹配运算。

48.为了更好的实现数据与逗号码的完全匹配,所述数据与逗号码的完全匹配运算包括:

49.将逗号阵列1中的逻辑运算结果传送至逗号阵列2中进行完全匹配运算,其中,逗号阵列2位于逗号阵列1之后。

50.需要说明的是,图1所示的cdb为逗号码检测阵列,cdb1为逗号阵列1,cdb2为逗号阵列2,具体的,在电路开始工作时,首先数据缓存单元会存储输入的数据,然后逗号码阵列中的阵列1(cdb1)会从存储的数据的最低有效位开始依次采样低翻转率带宽下的数据与逗号阵列做逻辑运算,若有与cdb1中相匹配的数据,则将相应的运算结果传送到逗号码阵列2(cdb2)中作进一步运算,用以确保该数据是与逗号码完全相匹配的。然后,状态机将cdb所得到的字节边沿结果传送给字节对齐电路,使其在相应的数据位处取出正确的字节数据,从而完成字节数据的校正。

51.值得注意的是,将逗号码的码长减少到了n bits得到一个新的逗号码,记为k

new

,则这个新的逗号码只需要n个同或逻辑门与接收到的数据进行逻辑运算,整个逗号码阵列需要n

×

10个同或逻辑门。此外,为了避免出现待检数据中包含新提出的逗号码k

new

的数据但却与逗号码不完全匹配的情况,还需要在所提出的新逗号码k

new

阵列的后面添加一个完

整的逗号码。最后,提出的新逗号码阵列所需要的同或逻辑门数量n为n=n

×

10 10,相对于传统的逗号码阵列,采用新的阵列可以减少同或逻辑门数量为d=10

×

(9-n),进而,在减少逗号码的位宽以达到减少硬件资源的目的的同时,会导致逻辑门的翻转率增大,进而增大逗号码阵列的功耗。

52.举例说明,一个标准的反相器电路的动态开关功耗为其中α是单位时间内逻辑门电路产生翻转的概率,f是电路的工作频率,c

l

是负载电容。由上述公式可知,在参数f和c

l

不变的情况下,可以通过减少逻辑门的翻转率α,进而降低电路功耗。假如新的逗号码的位宽为n,则整个逗号码阵列的功耗为

53.为了使整个逗号码阵列的功耗降至最低,所述逗号阵列1为码长为6bits的逗号码组成的逗号码阵列。

54.在本实施例中,当逗号码的位宽为6时,位宽和翻转率α之间可以达到一个最优解,此时整个逗号码阵列的功耗会达到最小值。

55.需要补充的是,为了验证逗号码位宽为6时的翻转率α为最优解,可以优选采用赛灵思(xilinx)公司的kc705系列fpga开发板对此结论进行验证,即通过fpga开发板来实现由不同码长的逗号码构成的逗号检测与字节对齐电路,查看并对比它们所消耗的硬件资源,检测结果如图5所示,且不同位宽的逗号码与归一化后的功耗之间的关系如图2所示,当逗号码k

new

的位宽是6时,逗号检测与字节对齐电路的功耗可以达到最低值,相对于传统结构降低了20.11%,资源占用量减少了31.72%。

56.为了进一步的实施该最优逗号码位宽为6下的逗号码阵列的应用,所述逗号码阵列包括6

×

10个同或逻辑门。

57.为了避免出现待检数据中包含上述内容中新提出逗号码k

new

的数据但却与逗号码不完全匹配的情况、以及逗号检测条件的一致性,所述逗号阵列2为与逗号阵列1相同码长的完整的逗号码。

58.为了更好的完成对字节数据的校正处理,所述字节数据的校正包括:

59.将字节边沿结果传送给字节对齐电路的相应数据位处,并取出正确的字节数据。

60.实施例二

61.本发明还提供了一种逗号检测与字节对齐的校正系统,包括:

62.数据缓存模块,所述数据缓存模块用于存储工作电路中的输入数据;

63.逗号码检测模块,所述逗号码检测模块用于将存储数据在逗号码阵列中进行低翻转率的完全匹配检测,其中,逗号码阵列包括对存储数据最低有效位开始依次采样数据并进行逻辑运算的逗号阵列1、以及确保逗号阵列1运算结果数据与逗号码完全匹配运算的逗号阵列2;

64.字节对齐电路模块,所述字节对齐电路模块用于将字节边沿在对应的数据位处取出正确的字节数据;以及

65.字节传输模块,所述字节传输模块用于将逗号码阵列获得的字节边沿传送至字节对齐电路模块。

66.需要说明的是,字节传输模块优选为状态机(fsm)。

67.举例说明,当存储的数据位20’b0000_1101_0111_1100_1010,而新的逗号码检测

阵列中检测码的码型为6’b11_1100,如图5所示;在cdb1中经过逻辑计算,可以得到s5的数据与检测码相匹配,即s5=k

new

=6'b11_1100,则相对应的指示信号sel_reg[9:0]的值为10’b00_0001_0000;cdb2电路根据这个结果取出相对应的缓存数据s[13:4]与一个完整的逗号码做逻辑运算,若两者相匹配,即k_right=sample_data[13:4]

⊙

k的结果为1时,则表示位s[13]和位s[4]是字节数据的边沿,此后字节对齐电路按照顺序传输数据,字节校正完成。

[0068]

上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。