一种小型化ipd无源器件及滤波器

技术领域

1.本发明涉及ipd无源器件技术领域,更具体地说,涉及一种小型化ipd无源器件及滤波器。

背景技术:

2.ipd滤波器由于其工艺特点,电感在整个版图中占据绝大多数的面积,由于ipd平面电感的特点面积越小电感q值(电感q值也叫电感的品质因数,是衡量电感器件的主要参数,是指电感器在某一频率的交流电压下工作时,所呈现的感抗与其等效损耗电阻之比,电感器的q值越高,其损耗越小,效率越高)一般越差,这就给ipd无源器件的小型化提高了难度,另外现阶段对滤波器的电性能要求越来越高,对ipd器件更是一种挑战。

3.前面的叙述在于提供一般的背景信息,并不一定构成现有技术。

技术实现要素:

4.本发明的目的在于提供一种小型化ipd无源器件及滤波器,该小型化ipd无源器件可以有效减小电感的电感量,在器件尺寸一定的情况下提高电感的q值,提高整个无源器件的电性能,也可以提高整个器件的小型化。

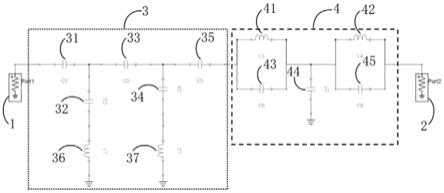

5.本发明提供一种小型化ipd无源器件,包括第一接口端口、第二接口端口、高通电路及低通电路;所述第一接口端口上连接有所述高通电路,所述高通电路和所述低通电路串联连接,所述低通电路另一端和所述第二接口端口连接;所述低通电路包括第三电感、第四电感、第六电容、第七电容及第八电容;所述第三电感和所述第四电感串联连接,所述第三电感的另一端和所述高通电路连接,所述第四电感的另一端和所述第二接口端口连接;所述第七电容一端连接于所述第三电感和所述第四电感之间,所述第七电容另一端与参考地相连;在所述第三电感和所述第四电感上分别并联有所述第六电容和所述第八电容。

6.进一步地,所述高通电路包括第一电容、第二电容、第三电容、第四电容、第五电容、第一电感及第二电感;所述第一电容、所述第三电容及所述第五电容串联连接,所述第一电容的另一端和所述第一接口端口连接,所述第五电容的另一端和所述第三电感连接;所述第二电容一端连接于所述第一电容和所述第三电容之间,所述第二电容另一端经所述第一电感与参考地相连;所述第四电容一端连接于所述第三电容和所述第五电容之间,所述第四电容另一端经所述第二电感与参考地相连。

7.进一步地,所述高通电路还包括第九电容和第十电容,所述第九电容和所述第十电容分别并联在所述第一电感和所述第二电感上。

8.本发明还提供一种滤波器,包括上述的小型化ipd无源器件。

9.本发明提供的小型化ipd无源器件,在ipd的电感上并联电容可以有效减小电感的电感量,在器件尺寸一定的情况下提高电感的q值,进而提高整个无源器件的电性能;由于电感量变小也可以提高整个器件的小型化。

附图说明

10.图1为本发明第一实施例提供的小型化ipd无源器件的原理示意图。

11.图2为图1中小型化ipd无源器件的电性能波形图。

12.图3为本发明第二实施例提供的小型化ipd无源器件的原理示意图。

13.图4为图3中小型化ipd无源器件的电性能波形图。

14.图5为现有技术的ipd无源器件的原理示意图。

15.图6为图5中ipd无源器件的电性能波形图。

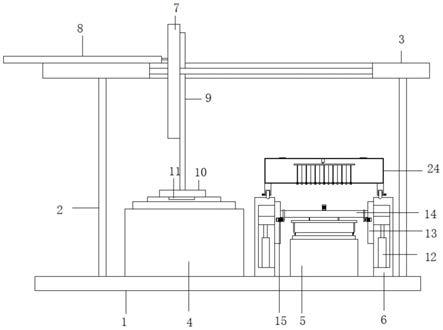

16.图7为一款ipd滤波器版图的布局图。

17.图8为两个占用相同面积电感量的电感示意图。

18.图9为图8中两个电感的仿真q值示意图。

19.附图中涉及的附图标记和组成部分如下所示:

20.1、第一接口端口

ꢀꢀꢀꢀ

2、第二接口端口

ꢀꢀꢀ

3、高通电路

21.31、第一电容

ꢀꢀꢀꢀꢀꢀꢀ

32、第二电容

ꢀꢀꢀꢀꢀꢀ

33、第三电容

22.34、第四电容

ꢀꢀꢀꢀꢀꢀꢀ

35、第五电容

ꢀꢀꢀꢀꢀꢀ

36、第一电感

23.37、第二电感

ꢀꢀꢀꢀꢀꢀꢀ

38、第九电容

ꢀꢀꢀꢀꢀꢀ

39、第十电容

24.4、低通电路

ꢀꢀꢀꢀꢀꢀꢀꢀ

41、第三电感

ꢀꢀꢀꢀꢀꢀ

42、第四电感

25.43、第六电容

ꢀꢀꢀꢀꢀꢀꢀ

44、第七电容

ꢀꢀꢀꢀꢀꢀ

45、第八电容

具体实施方式

26.下面结合附图和实施例,对本发明的具体实施方式作进一步详细描述。以下实施例用于说明本发明,但不用来限制本发明的范围。

27.本发明的说明书和权利要求书中的术语“第一”、“第二”、“第三”、“第四”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。

28.实施例1

29.图1为本发明第一实施例提供的小型化ipd无源器件的原理示意图,图2为图1中小型化ipd无源器件的电性能波形图。请参照图1、图2,本发明实施例提供的小型化ipd无源器件,包括第一接口端口1、第二接口端口2、高通电路3及低通电路4;第一接口端口1上连接有高通电路3,高通电路3和低通电路4串联连接,低通电路4另一端和第二接口端口2连接;

30.高通电路3包括第一电容31、第二电容32、第三电容33、第四电容34、第五电容35、第一电感36及第二电感37;第一电容31、第三电容33及第五电容35串联连接,第一电容31的另一端和第一接口端口1连接,第五电容35的另一端和第三电感41连接;第二电容32一端连接于第一电容31和第三电容33之间,第二电容32另一端经第一电感36与参考地相连;第四电容34一端连接于第三电容33和第五电容35之间,第四电容34另一端经第二电感37与参考地相连。

31.低通电路4包括第三电感41、第四电感42、第六电容43、第七电容44及第八电容45;第三电感41和第四电感42串联连接,第三电感41的另一端和高通电路3连接,第四电感42的另一端和第二接口端口2连接;第七电容44一端连接于第三电感41和第四电感42之间,第七电容44另一端与参考地相连;在第三电感41和第四电感42上分别并联有第六电容43和第八电容45。

32.需要说明的是,发明实施例提供的小型化ipd无源器件,在低通电路4的第三电感41和第四电感42上分别并联有第六电容43和第八电容45;进而可以产生并联谐振,通过图2中的电性能波形图可以看出在第三电感41和第四电感42上分别并联有第六电容43和第八电容45后在通带高频产生了两个传输零点增加了高频抑制(一般为增加传输零点都会在低通电感上并联电容)。

33.实施例2

34.本实施例提供的小型化ipd无源器件和第一实施例提供的小型化ipd无源器件基本相同,不同之处在于高通电路3。

35.图3为本发明第二实施例提供的小型化ipd无源器件的原理示意图,图4为图3中小型化ipd无源器件的电性能波形图。请参照图3、图4,本发明实施例提供的小型化ipd无源器件的高通电路3还包括第九电容38和第十电容39,第九电容38和第十电容39分别并联在第一电感36和第二电感37上。

36.需要说明的是,对比图2和图4的电性能波形图可以看出,相比于第一实施例本实施例的高频抑制得到了提高;进一步地,另外由于第三电感41和第四电感42上的电感量减小了一半左右,可以在较小的面积下实现相同的电性能,实现了ipd器件的小型化。

37.实施例3

38.本实施例以带通滤波器(通带范围:2300-2700mhz)为例进行说明。

39.图5为现有技术的ipd无源器件的原理示意图,图6为图5中ipd无源器件的电性能波形图。

40.对比图1和图5以及图2和图6,在低通电路4的第三电感41和第四电感42上并联电容可以产生并联谐振,对比图2和图6可以看出增加并联电容后在通带高频产生了两个传输零点增加了高频抑制(一般为增加传输零点都会在低通电感上并联电容)。

41.图7为一款ipd滤波器版图的布局图。请参照图7,从图中可以看出虚线框内的电感占据了版图布局的大多数面积,而实线方框内的电容就相对容易实现。

42.本实施例在图5的第三电感41和第四电感42上并联电容可以有效减小使用的电感量(第三电感41和第四电感42的电感量从原来的最大6nh,可以减小到最大3nh),一般电感的面积越大q值越高,减小电感量在相同的面积小可以增加电感的线宽等可以提高电感q值,也可以在更小的面积做到相同电性能指标。

43.图8为两个占用相同面积电感量的电感示意图,图9为图8中两个电感的仿真q值示意图。请参照图8、图9,图8为两个占用相同面积电感量分别为6nh和3nh的电感,图9为此两个电感的仿真q值。从图9可以得出电感量减小后在相同的面积下可以获得更大的q值,q值越大滤波器的电性能越好。

44.基于上文的描述可知,本发明优点在于:

45.1、本发明提供的小型化ipd无源器件,在低通电路4的第三电感41和第四电感42上分别并联有第六电容43和第八电容45;进而可以产生并联谐振,通过图2中的电性能波形图可以看出在第三电感41和第四电感42上分别并联有第六电容43和第八电容45后在通带高频产生了两个传输零点增加了高频抑制。

46.2、本发明提供的小型化ipd无源器件,在高通电路3的第九电容38和第十电容39分别并联第一电感36和第二电感37,从而使得高频抑制得到了提高,可以在较小的面积下实

现相同的电性能,实现了ipd器件的小型化。

47.本发明还提供一种滤波器,包括上述的小型化ipd无源器件。

48.以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以所述权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。