1.本发明关于电子电路,特别是一种功率放大器的电压控制电路。

背景技术:

2.在通信装置中,功率放大器会将信号放大以传送射频信号。射频信号的功率需要符合通信规范,以在预定覆盖范围内传送同时减低通信装置间的信号干扰。由于通信装置的电源通常由电池提供,因此会随使用时间而逐渐下降。当电池的电压过低时,会造成提供至功率放大器的电源过低,使射频信号无法满足通信规范的要求,增加通信装置间的信号干扰及降低通信装置的效能。

技术实现要素:

3.本发明实施例提供一种电压控制电路,包含追踪电路、运算放大器、参考端、晶体管、回馈电路及取样及保持电路。追踪电路用以依据致能电压、取样致能电压及取样参考电压产生随致能电压而更新的更新致能电压。运算放大器包含第一输入端,耦接于追踪电路,用以接收输入电压,第二输入端,用以接收回馈电压,及输出端,用以输出控制电压。参考端用以提供参考电压。晶体管包含控制端,耦接于运算放大器的输出端,用以接收控制电压;第一端,用以接收参考电压;及第二端,用以输出调节电压。回馈电路耦接于晶体管的第二端及运算放大器的第二输入端之间,用以依据调节电压产生回馈电压。取样及保持电路耦接于追踪电路、运算放大器及回馈电路,用以取样与保持输入电压以产生取样致能电压,及取样回馈电压以产生取样参考电压。

附图说明

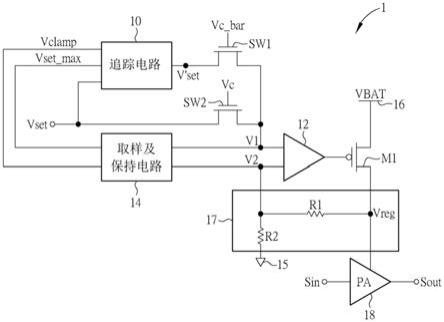

4.图1为本发明实施例中的一种电压控制电路的示意图。图2为显示图1中的调节电压的波形图。图3为图1中的取样及保持电路的示意图。图4为图1中的电压控制电路的时序图。符号说明1:电压控制电路10:追踪电路12:运算放大器14:取样及保持电路140,142:传输闸15,16:参考端17:回馈电路18:功率放大器20,22:波形

m1,m140至m143:晶体管r1,r2,r140,r142:电阻c140,c142:电容sin:交流信号sout:放大后的交流信号sw1及sw2:开关t0至t4:时间v1:输入电压v2:回馈电压vbat:参考电压vc:控制信号vc_bar:反相控制信号vclamp:取样参考电压vmask:屏蔽vset:致能电压v’set:更新致能电压vset_max:取样致能电压vr0至vr3:电压位准vrd:取样控制电压vrd_bar:反相取样控制电压vreg:调节电压

具体实施方式

5.图1为本发明实施例中的一种电压控制电路1的示意图。电压控制电路1可做为低压差稳压器(low dropout regulator,ldo regulator),由参考电压vbat供电而产生调节电压vreg,并将调节电压vreg作为电源供应至功率放大器(power amplifier,pa)18。电压控制电路1可对调节电压vreg进行调节而使得当参考电压vbat大于或非常接近调节电压vreg时仍可将调节电压vreg维持在实质上稳定的预定位准。参考电压vbat是由电池或电池组产生的可变电压,可随使用时间逐渐降低。当参考电压vbat下降至过低的位准时,电压控制电路1无法将调节电压vreg维持在预定位准而会随参考电压vbat降低。

6.电压控制电路1可包含追踪电路10、运算放大器12、取样及保持电路14、参考端16、回馈电路17及晶体管m1。参考端16可提供参考电压vbat。运算放大器12包含第一输入端,耦接于追踪电路10;第二输入端,耦接于回馈电路17;及输出端,耦接于晶体管m1。晶体管m1包含控制端,耦接于运算放大器12的输出端;第一端,耦接于参考端16;及第二端,耦接于功率放大器18。回馈电路17耦接于晶体管m1的第二端及运算放大器12的第二输入端,用以依据调节电压vreg产生回馈电压v2。回馈电压v2可正相关于调节电压vreg。功率放大器18包含电源端,用以接收调节电压vreg;输入端,用以输入交流信号sin;及输出端,用以输出放大后的交流信号sout。交流信号sin及放大后的交流信号sout可为射频信号。

7.运算放大器12的第一输入端可为反相输入端,运算放大器12的第二输入端可为正

向输入端。运算放大器12的第一输入端可接收输入电压v1,运算放大器12的第二输入端可接收回馈电压v2,运算放大器12的输出端可依据回馈电压v2及输入电压v1之间的差值而产生控制电压。晶体管m1的控制端可接收控制电压,晶体管m1的第二端可依据控制电压输出调节电压vreg。晶体管m1可为场效晶体管(field-effect transistor,fet),例如为p型金属氧化物半导体场效晶体管(metal-oxide-semiconductor field-effect transistor,mosfet),及可设置为共源级放大阶段。当回馈电压v2实质上等于输入电压v1时,控制电压实质上等于0v,晶体管m1导通而产生调节电压vreg。当回馈电压v2小于输入电压v1时,控制电压小于0v,晶体管m1的导通程度增加而增加调节电压vreg。当参考电压vbat小于调节电压vreg的预定位准时,晶体管m1的第二端输出的调节电压vreg会小于预定位准。当关闭功率放大器18时,输入电压v1必须降低至小于回馈电压v2才可降低调节电压vreg。

8.图2为显示调节电压vreg的波形图,包含通信规范中定义的屏蔽vmask、符合通信规范的调节电压vreg的波形20及未符合通信规范的调节电压vreg的波形22。波形20可对应于本发明实施例所产生的波形,而波形22可对应于先前技术所产生的波形。当功率放大器18运作时,调节电压vreg不超出屏蔽vmask才可符合通信规范而不会对其他装置造成信号干扰。在时间t0,功率放大器18开始被开启,波形20及22开始从低位准vr0上升。在时间t1,波形20及22上升至预定位准vr1。时间t0至t1之间的时段可称为电压上升期间(ramp-up period)。在时间t2,功率放大器18开始被关闭,波形20开始从位准vr2下降,波形22维持在位准vr2。位准vr2可小于预定位准vr1。在时间t1至t2之间的时段可称为功率放大器开启期间,功率放大器18可放大交流信号sin。在时间t3,波形20下降至位准vr3,波形22才开始从位准vr2下降。在时间t4,波形20及22下降至低位准vr0。时间t2至t4之间的时段可称为电压下降期间(ramp-down period)。时间t4至下次功率放大器18开始被开启的时间t0可称为功率放大器关闭期间,功率放大器18在这段期间无法运作。由于波形22在时间t3才开始从位准vr2下降,因此在时间t3会超出屏蔽vmask,而不符合通信规范且可能会对其他装置造成信号干扰。此外,由于波形22在时间t3至t4之间的时段突然从位准vr2下降至低位准vr0,因此可能会产生瞬时噪声(transient noise),对其他内部电路造成信号干扰。相较之下,波形20在电压下降期间中缓缓下降,并未超出屏蔽vmask,符合通信规范,且不易对其他装置或内部电路造成信号干扰。

9.电压控制电路1可藉由取样及保持电路14及追踪电路10在时间t2后使输入电压v1随着回馈电压v2而改变,例如在时间t2后随即将输入电压v1拉至回馈电压v2而产生符合通信规范的调节电压vreg的波形20。取样及保持电路14可耦接于追踪电路10、运算放大器12及回馈电路17。在电压下降期间中,取样及保持电路14可取样及保持输入电压v1以产生取样致能电压vset_max,及取样及保持回馈电压v2以产生取样参考电压vclamp。追踪电路10可依据致能电压vset、取样致能电压vset_max及取样参考电压vclamp产生随致能电压vset而更新的更新致能电压v’set。更新致能电压v’set可与取样参考电压vclamp成正相关,且与取样致能电压vset_max成负相关。具体而言,追踪电路10可将取样参考电压vclamp除以取样致能电压vset_max以产生比例(vclamp/vset_max),及将比例(vclamp/vset_max)及致能电压vset相乘以产生更新致能电压v’set,如公式1表示:v’set=(vclamp/vset_max)*vset

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

公式1

10.若参考电压vbat小于调节电压vreg的预定位准,回馈电压v2小于输入电压v1,取

样参考电压vclamp小于取样致能电压vset_max,更新致能电压v’set可为致能电压vset依据比例(vclamp/vset_max)产生的缩小值。追踪电路10可由乘法器电路实现。

11.在一实施例中,电压控制电路1可另包含开关sw1及sw2。开关sw1及sw2可被设定为在致能电压vset及更新致能电压v’set之间切换,而于电压下降期间依据更新致能电压v’set产生输入电压v1,及于非电压下降期间依据致能电压vset产生输入电压v1。非电压下降期间可为电压下降期间之外的所有时间,可包含电压上升期间、功率放大器开启期间及功率放大器关闭期间。由于更新致能电压v’set可为致能电压vset乘以比例(vclamp/vset_max)的缩小值,电压下降期间的输入电压v1可被拉至回馈电压v2而使输入电压v1从回馈电压v2开始下降,进而产生符合通信规范的调节电压vreg的波形20。开关sw1及sw2的导通状况可为相反。在非电压下降期间中,第一控制信号vc_bar会截止开关sw1,第二控制信号vc会导通开关sw2。在电压下降期间中,第一控制信号vc_bar会导通开关sw1第一预定时间,及第二控制信号vc会截止开关sw2第一预定时间。第一预定时间可小于电压下降期间。第二控制信号vc及第一控制信号vc_bar可互为反相信号,及可被设为逻辑低位准或逻辑高位准。第二控制信号vc可为高态有效(active high)信号,第一控制信号vc_bar可为低态有效(active high)信号。在本实施例中,开关sw1及开关sw2可为相同型式的晶体管,例如皆为n型晶体管,举例来说是nmos。在其他实施例中,开关sw1及开关sw2可为不同型式的晶体管,例如其中之一为n型晶体管而其中另一为p型晶体管,因此第二控制信号vc及第一控制信号vc_bar可为同相信号。开关sw1包含控制端,用以接收第一控制信号vc_bar;第一端,耦接于追踪电路10,用以接收更新致能电压v’set;及第二端,耦接于运算放大器12的第一输入端,用以输出输入电压v1。开关sw2包含控制端,用以接收第二控制信号vc;第一端,用以接收致能电压vset;及第二端,耦接于运算放大器12的第一输入端,用以输出输入电压v1。

12.回馈电路17可包含回馈阻抗r1及r2。回馈阻抗r1包含第一端,耦接于晶体管m1的第二端;及第二端,耦接于运算放大器12的第二输入端,用以产生回馈电压v2。回馈阻抗r2包含第一端,耦接于回馈阻抗r1的第二端;及第二端,耦接于参考端15。参考端15可提供接地电压,例如0v。回馈阻抗r1及r2的阻抗值可调整调节电压vreg的值。当回馈阻抗r1的阻抗值增加及/或回馈阻抗r2的阻抗值减少,调节电压vreg会增加;当回馈阻抗r1的阻抗值减少及/或回馈阻抗r2的阻抗值增加,调节电压vreg会降低。在一些实施例中,回馈阻抗r1及r2的阻抗值可将调节电压vreg调整为(8/3)v’set。在其他实施例中,调节电压vreg也可透过改变回馈阻抗r1及r2的阻抗值而调整为其他值。

13.在电压上升期间,致能电压vset可由低位准逐渐拉至高位准。在电压下降期间,致能电压vset可由高位准逐渐拉至低位准。在功率放大器开启期间,致能电压vset可维持在高位准。在功率放大器关闭期间,致能电压vset可维持在低位准。低位准可为0v,高位准可大于或等于逻辑高位准。致能电压vset可由外部输入或由电压产生器产生。

14.图3为取样及保持电路14的示意图。取样及保持电路14包含传输闸140、电阻r140、电容c140、传输闸142、电阻r142、电容c142。

15.传输闸140可依据取样控制电压vrd及反相取样控制电压vrd_bar取样输入电压v1以产生取样致能电压vset_max。电阻r140包含第一端,耦接于传输闸140;及第二端,用以输出取样致能电压vset_max。电容c140包含第一端,耦接于电阻r140的第二端;及第二端,耦接于参考端15。传输闸142可依据取样控制电压vrd及反相取样控制电压vrd_bar取样回馈

电压v2以产生取样参考电压vclamp。电阻r142包含第一端,耦接于传输闸142;及第二端,用以输出取样参考电压vclamp。电容c142包含第一端,耦接于电阻r142的第二端;及第二端,耦接于参考端15。

16.传输闸140包含晶体管m140及晶体管m141。晶体管m140包含控制端,用以接收取样控制电压vrd;第一端,用以接收输入电压v1;及第二端,耦接于电阻r140的第一端。晶体管m141包含控制端,用以接收反相取样控制电压vrd_bar;第一端,用以接收输入电压v1;及第二端,耦接于电阻r140的第一端。传输闸142包含晶体管m142及晶体管m143。晶体管m142包含控制端,用以接收取样控制电压vrd;第一端,用以接收回馈电压v2;及第二端,耦接于电阻r142的第一端。晶体管m143包含控制端,用以接收反相取样控制电压vrd_bar;第一端,用以接收回馈电压v2;及第二端,耦接于电阻r142的第一端。晶体管m140及晶体管m142可属于第一种半导体种类,晶体管m141及晶体管m143可属于第二种半导体种类,第一种半导体种类及第二种半导体种类可不同。举例而言,晶体管m140及晶体管m142可为n型晶体管,例如nmos。晶体管m141及晶体管m143可为p型晶体管,例如pmos。

17.取样控制电压vrd及反相取样控制电压vrd_bar可互为反相,及可被设为逻辑低位准或逻辑高位准。取样控制电压vrd可为高态有效信号,反相取样控制电压vrd_bar可为低态有效信号。在一些实施例中,取样控制电压vrd及第二控制信号vc可互为反相,反相取样控制电压vrd_bar及第一控制信号vc_bar可互为反相。在电压下降期间中,取样控制电压vrd可导通传输闸140第一预定时间,以从输入电压v1取样取样致能电压vset_max及将取样致能电压vset_max储存于电容c140。取样控制电压vrd可导通传输闸142第一预定时间,以从回馈电压v2取样取样参考电压vclamp及将取样参考电压vclamp储存于电容c142。取样控制电压vrd的第一预定时间可小于电压下降期间,及可实质上等于第一控制信号vc_bar导通开关sw1的第一预定时间。取样致能电压vset_max可为在第一预定时间中输入电压v1的最大取样值,及取样参考电压vclamp可为在第一预定时间中回馈电压v2的最大取样值。

18.图4为电压控制电路1的时序图,包含调节电压vreg、屏蔽vmask、致能电压vset、取样控制电压vrd、反相取样控制电压vrd_bar、第二控制信号vc、第一控制信号vc_bar、取样致能电压vset_max、取样参考电压vclamp及更新致能电压v’set。在时间t2,电压下降期间开始,取样控制电压vrd由逻辑低位准被拉至逻辑高位准,反相取样控制电压vrd_bar由逻辑高位准被拉至逻辑低位准,取样及保持电路14中的传输闸140被致能以取样输入电压v1而产生取样致能电压vset_max,取样及保持电路14中的传输闸142被致能以取样回馈电压v2而产生取样参考电压vclamp,追踪电路10依据公式(1)产生更新致能电压v’set,第二控制信号vc由逻辑高位准被拉至逻辑低位准,第一控制信号vc_bar由逻辑低位准被拉至逻辑高位准,开关sw1被导通及开关sw2被截止以依据更新致能电压v’set将输入电压v1拉低,使调节电压vreg开始下降。在时间t3,取样控制电压vrd由逻辑高位准被拉至逻辑低位准,反相取样控制电压vrd_bar由逻辑低位准被拉至逻辑高位准,取样及保持电路14中的传输闸140及142被失能,第二控制信号vc由逻辑低位准被拉至逻辑高位准,第一控制信号vc_bar由逻辑高位准被拉至逻辑低位准,开关sw1被截止及开关sw2被导通以依据致能电压vset将输入电压v1拉低。由于此时输入电压v1开始小于回馈电压v2,运算放大器12会依据输入电压v1逐渐将调节电压vreg拉低,回馈电压v2也会随调节电压vreg逐渐降低。在时间t4,电压下降期间结束,致能电压vset降至低位准vr0,同时调节电压vreg也降至低位准vr0。调节电

压vreg在电压下降期间中缓缓下降,未超出屏蔽vmask,符合通信规范,且不易对其他装置或内部电路造成信号干扰。

19.综上所述,本发明实施例在电压下降期间开始后,电压控制电路1藉由取样及保持电路14及追踪电路10可使输入电压v1随着回馈电压v2而改变,使调节电压vreg产生较平缓的下降波形,符合通信规范,减少瞬时噪声,不易对其他装置或内部电路造成信号干扰,增加装置效能。以上所述仅为本发明的较佳实施例,凡依本发明申请权利要求所做的等同变化与修饰,皆应属本发明的涵盖范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。