1.本发明涉及一种半导体元件,特别是涉及一种功率半导体元件(power semiconductor device)。

背景技术:

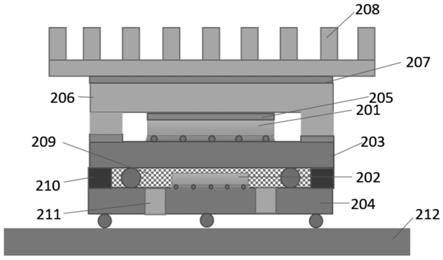

2.功率半导体元件,例如,金属氧化物半导体场效晶体管(metal-oxide-semiconductor field-effect transistor,mosfet),为电子信息产品的电源控制元件,具备大导通电流、低导通电阻值、高切换速度及耐高压电流的特性,主要应用于计算机、移动电话及可携式产品的交换式电源控制系统。

3.而为了实现更高电压的操作,现有的作法是延长金属氧化物半导体场效晶体管的栅极长度(lg),以防止热载流子注入(hot carriers injectionhci)所引发的击穿(punch through)漏电现象。然而考虑元件的尺寸(design rule)与制作工艺技术(例如,化学机械研磨(chemical-mechanical planarization,cmp)的平整度)的局限性,栅极长度无法过度延长。因此如何在不过度延长栅极长度的前提下,提高金属氧化物半导体场效晶体管的操作电压以及元件的可靠度,已经成为该技术领域的重要课题之一。

4.因此,有需要提供一种先进的功率半导体元件,来解决现有技术所面临的问题。

技术实现要素:

5.本发明的一实施例揭露一种功率半导体元件,其特征在于,该功率半导体元件包括:基材、第一阱区、第二阱区、漏极、源极、第一栅极结构、第二栅极结构以及掺杂区。第一阱区具有第一电性,由基材表面延伸进入基材之中。第二阱区具有第二电性,由基材表面延伸进入基材之中。漏极具有第一电性,并位于第一阱区之中。源极具有第一电性,并位于第二阱区之中。第一栅极结构位于基材表面上,且与第一阱区和第二阱区至少部分重叠。第二栅极结构位于基材表面上,且与第二阱区重叠,并与第一栅极结构隔离。掺杂区具有该第一电性,位于第二阱区之中,并且连接第一栅极结构和第二栅极结构。

6.根据上述实施例,本发明是在提供一种功率半导体元件包括至少二个金属氧化物半导体场效晶体管元件,其在源极和漏极之间至少形成彼此分隔的第一栅极结构和第二栅极结构,再以一个掺杂区将此二个栅极结构电连接在一起。其中,此一掺杂区的电性与源极和漏极相同,用于使第一栅极结构与源极和漏极组合形成一个第一晶体管单元;且使第二栅极结构与掺杂区和漏极的组合形成一个第二晶体管单元,并与第一晶体管单元彼此串连。通过此一设计可以在不过度延长栅极长度的前提下,提高功率半导体元件的操作电压以及可靠度。

附图说明

7.为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合所附的附图详细说明如下:

8.图1a至图1e为本发明的一实施例所绘示的一系列制作功率半导体元件的制作工艺结构剖面示意图;

9.图2为本发明的另一实施例所绘示的功率半导体元件的结构剖面示意图;

10.图3a为图2所提供的功率半导体元件和比较例的功率半导体元件的栅极-源极/漏极重叠长度-驱动电流(ion)关系曲线图;

11.图3b为图2所提供的功率半导体元件和比较例的功率半导体元件的栅极-源极/漏极重叠长度-截止电流(ioff)关系曲线图;

12.图3c为图2所提供的功率半导体元件和比较例的功率半导体元件的栅极-源极/漏极重叠长度-最大基材电流(isubmax)关系曲线图;

13.图4为本发明的又一实施例所绘示的功率半导体元件的结构剖面示意图;

14.图5a为图4所提供的功率半导体元件和比较例的功率半导体元件的栅极-源极/漏极重叠长度-驱动电流(ion)关系曲线图;

15.图5b为图4所提供的功率半导体元件和比较例的功率半导体元件的栅极-源极/漏极重叠长度-截止电流(ioff)关系曲线图;以及

16.图5c为图4所提供的功率半导体元件和比较例的功率半导体元件的栅极-源极/漏极重叠长度-最大基材电流(isubmax)关系曲线图。

17.符号说明

18.100、200、400:功率半导体元件

19.101、401:基材

20.101a、401a:基材表面

21.102、403:p型阱区

22.103、402:n型阱区

23.104:栅介电层

24.105:导体层

25.106、107、407:栅极结构

26.108、408:虚拟栅极结构

27.109、409:源极

28.110、410:漏极

29.111、411:掺杂区

30.112:金属内连线结构

31.113:共同电压源

32.120、130:金属氧化物半导体场效晶体管单元

33.240:浅沟隔离结构

34.301、302、303、311、312、313、501、502、503、511、512、513:栅极-源极/漏极重叠长度-驱动电流关系曲线

35.p:p型阱区和n型阱区之间的距离

36.lov2、lov4:栅极-源极/漏极重叠长度

37.h:p型阱区和n型阱区之间的距离

具体实施方式

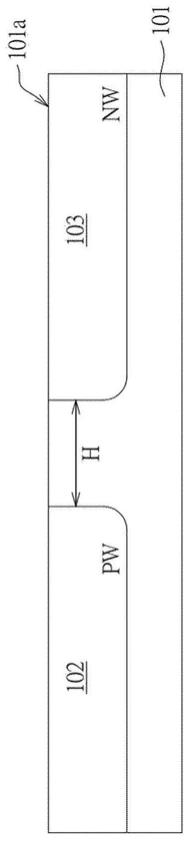

38.本发明是提供一种功率半导体元件,可在不过度延长栅极长度的前提下,提高金属氧化物半导体场效晶体管的操作电压以及元件可靠度。为了对本发明的上述实施例及其他目的、特征和优点能更明显易懂,下文特举多个实施例,并配合所附的附图作详细说明。

39.但必须注意的是,这些特定的实施案例与方法,并非用以限定本发明。本发明仍可采用其他特征、元件、方法及参数来加以实施。优选实施例的提出,仅用以例示本发明的技术特征,并非用以限定本发明的权利要求。该技术领域中具有通常知识者,将可根据以下的描述,在不脱离本发明的精神范围内,作均等的修饰与变化。在不同实施例与附图之中,相同的元件,将以相同的元件符号加以表示。

40.请参照图1a至图1e,图1a至图1e是根据本发明的一实施例所绘示的一系列制作功率半导体元件100的制作工艺结构剖面示意图。功率半导体元件100的制作方法包括下述步骤:首先提供一个基材101。在本发明的一些实施例中,基材101可以是由半导体材质,例如硅(silicon,si)、锗(germanium,ge),或化合半导体材质,例如砷化镓(gallium arsenide,gaas),所构成。但在另一些实施例中,基材101。也可以是一种绝缘层上覆硅(silicon oninsulator,soi)基板。在本实施例之中,基材101较佳是一种硅基材,例如是硅晶片(如图1a所绘示)。

41.接着,以至少一次离子掺杂(ion implantation)制作工艺,在元件基材101表面101a中形成至少一个p型阱区102以及至少一个n型阱区103。在本发明的一些实施例中,p型阱区102(或以pw表示)和n型阱区103(或以nw表示)都由基材101表面101a延伸进入基材101之中。其中,n型阱区103与p型阱区102邻接,但彼此隔离。在本实施例中,基材101具有p型电性;p型阱区102和n型阱区103具有比基材101还大的掺杂浓度,且二者是通过一部分的基材101彼此隔离。其中p型阱区102和n型阱区103之间的距离h(如图1b所绘示)。

42.然而n型阱区103与p型阱区102的配置并不以此为限,例如在本发明的另一实施例中,n型阱区103与p型阱区102并未彼此隔离。

43.接着,在基材101表面101a形成依序堆叠的栅介电层104和导体层105。在本发明的一些实施例中,构成介电层104的材料可以是二氧化硅(sio2)、氮化硅(sin)、氮氧化硅(sino)、高介电系数(high-κ)介电材料(例如,氧化鋡(hfo2)、氧化铝(alo

x

))或上述介电材料的组合。构成导体层105可以是多晶硅、金属(例如、金、银、铜、铝或钨)、金属化合物(例如,氮化钛或氮化钽)或上述的组合。

44.之后,以光致抗蚀剂蚀刻制作工艺对栅介电层104和导体层105进行图案化,用于在基材101表面101a形成多个包含一部分介电层104和一部分导体层105的栅极结构106和107。其中,栅极结构106与p型阱区102重叠;栅极结构107则分别与p型阱区102和n型阱区103至少部分重叠。换言之,栅极结构107横跨p型阱区102和n型阱区103,且与用来隔离p型阱区102和n型阱区103的一部分基材101重叠(如图1c所绘示)。

45.在本发明的一些实施例中,图案化介电层104和导体层105的步骤,还可以基材101表面101a上形成至少一个包含一部分介电层104和一部分导体层105的虚拟栅极结构108。例如,在本实施例中,图案化介电层104和导体层105的步骤还包括形成一个虚拟栅极结构108与n型阱区103重叠,并且与栅极结构106和107隔离。栅极结构107位于栅极结构106和虚拟栅极结构108之间。

46.后续,通过至少一次离子掺杂或外延制作工艺,在元件基材101表面101a中形成具有n型电性的源极109、漏极110和掺杂区111;使源极109位于p型阱区102之中,并且邻接栅极结构106;使漏极110位于n型阱区103之中,并邻接虚拟栅极结构108,且使虚拟栅极结构108位于栅极结构107和漏极110之间;使掺杂区111位于p型阱区102之中,并且连接栅极结构106和栅极结构107(如图1d所绘示)。在本发明的一些实施例中,源极109、漏极110和掺杂区111的掺杂浓度,都大于p型阱区102和n型阱区103的掺杂浓度,故而,源极109、漏极110和掺杂区111以n 表示之。

47.其中,栅极结构106、源极109、漏极110、p型阱区102、n型阱区103和基材101构成一个金属氧化物半导体场效晶体管单元120。栅极结构107、掺杂区111、漏极110、p型阱区102、n型阱区103和基材101构成另一个金属氧化物半导体场效晶体管单元130,且二个金属氧化物半导体场效晶体管单元120和130通过掺杂区111彼此串联。

48.后续,进行后段制作工艺,例如金属镶嵌制作工艺(metal damascene process),在基材101的表面101a上形成金属内连线结构112,使虚拟栅极结构108浮置(floating),并使栅极结构106和栅极结构107连接至一个共同电压源113,即可形成如图1e所绘示的功率半导体元件100。

49.制备完成的功率半导体元件100,包括:基材101、p型阱区102、n型阱区103、漏极110、源极109、栅极结构106、栅极结构107、虚拟栅极结构108以及掺杂区111。p型阱区102和n型阱区103由基材101表面101a延伸进入基材101之中,并且可(但不限)彼此隔离。源极109、漏极110和掺杂区111都具有n型电性,其中,漏极110位于n阱区103之中;源极109位于p型阱区102之中。栅极结构107位于基材101表面101a上,且与p型阱区102和n型阱区103至少部分重叠。栅极结构106位于基材101表面101a上,且与p型阱区102重叠,并与栅极结构107隔离。掺杂区111位于p型阱区102之中,并且连接栅极结构106和栅极结构107。虚拟栅极结构108位于基材101表面101a上,与n型阱区103重叠;且位于栅极结构107和漏极110之间。

50.然而值得注意的是,功率半导体元件100的结构并不以此为限,例如在本发明的另一些实施例中,功率半导体元件100可以包括更多的虚拟栅极结构(未绘示),具有与虚拟栅极结构108相同的结构,且位于栅极结构107和虚拟栅极结构108之间。在本发明的另一些实施例中,功率半导体元件100可以包括更多与栅极结构106相同的栅极结构,配置于栅极结构107和栅极结构106之间。

51.另外,请参照图2,图2是根据本发明的另一实施例所绘示的功率半导体元件200的结构剖面示意图。在本实施例中,功率半导体元件200的结构大致与功率半导体元件100类似,差别在于功率半导体元件200还包括一个隔离结构,例如浅沟隔离结构(shallow trench insulator,sti)240,位于型n阱区103之中,且位于栅极结构107和虚拟栅极结构108(或位于栅极结构107和漏极111)之间。

52.接着,按照本发明图2所述的功率半导体元件200的结构,制作出具有不同栅极-源极/漏极重叠长度(gate-to-s/d overlap length,lov)lov2的多个功率半导体元件200,并记录及分析这些功率半导体元件200的驱动电流(ion)、截止电流(ioff)和最大基材电流(isubmax)的变化。且与现有具有单一n型金属氧化物半导体场效晶体管单元的功率半导体元件的比较例进行比较。

53.请参照图3a至图3c,图3a是绘示图2所提供的功率半导体元件200和比较例的功率

半导体元件的栅极-源极/漏极重叠长度-驱动电流(ion)关系曲线图。图3b是绘示图2所提供的功率半导体元件200和比较例的功率半导体元件的栅极-源极/漏极重叠长度-截止电流(ioff)关系曲线图。图3c是绘示图2所提供的功率半导体元件200和比较例的功率半导体元件的栅极-源极/漏极重叠长度-最大基材电流(isubmax)关系曲线图。

54.其中,横轴代表标准化之后(normalized)的栅极-源极/漏极重叠长度(单位为a.u.),横轴分别代表标准化之后的驱动电流(ion)、截止电流(ioff)和最大基材电流(isubmax)(单位分别为a.u.)。曲线301、302和303分别代表功率半导体元件200的栅极-源极/漏极重叠长度-驱动电流(ion)关系曲线、栅极-源极/漏极重叠长度-截止电流(ioff)关系曲线以及栅极-源极/漏极重叠长度-最大基材电流(isubmax)关系曲线。曲线311、312和313分别代表比较例所提供的功率半导体元的栅极-源极/漏极重叠长度-驱动电流(ion)关系曲线、栅极-源极/漏极重叠长度-截止电流(ioff)关系曲线以及栅极-源极/漏极重叠长度-最大基材电流(isubmax)关系曲线。

55.由图3a至图3c可以看出,在相同栅极-源极/漏极重叠长度lov2下,功率半导体元件200的驱动电流(ion)、截止电流(ioff)和最大基材电流(isubmax),都小于比较例所提供的功率半导体元的驱动电流(ion)、截止电流(ioff)和最大基材电流(isubmax)。可见,和比较例所提供的功率半导体元件相比,当具有相同驱动电流(ion)、截止电流(ioff)和最大基材电流(isubmax)的情况下,功率半导体元件200可以具有较长的栅极-源极/漏极重叠长度lov2,较不易产生热载流子注入(所引发的击穿漏电现象,因此具有较高的操作电压。

56.另外,功率半导体元件200驱动电流(ion)、截止电流(ioff)和最大基材电流(isubmax),随着栅极-源极/漏极重叠长度的增长并无明显的波动。反观,比较例所提供的功率半导体元件的驱动电流(ion)、截止电流(ioff)和最大基材电流(isubmax)随着栅极-源极/漏极重叠长度的增长明显飙高。显示功率半导体元件200,相对于比较例所提供的功率半导体元,具有较高的设计弹性与操作可靠度。

57.另外,虽然上述实施例所述的功率半导体元件100和200所包含的且横向扩散金属氧化物半导体场效晶体管元件120和晶体管元件130,都为n型电性场效晶体管。但在本发明所述的功率半导体元件并不以此为限,在例如请参照图4,图4是根据本发明的又一实施例所绘示的功率半导体元件400结构剖面示意图。功率半导体元件400一些实施例中,功率半导体元件400的结构大致与功率半导体元件200类似,差别在于功率半导体元件400包括p型电性场效晶体管。

58.在本实施例中,功率半导体元件400,包括:基材401、n型阱区402、p型阱区403、漏极410、源极409、栅极结构406、栅极结构407、虚拟栅极结构408以及掺杂区411。其中基材401具有n型电性。

59.n型阱区402和p型阱区403由基材401表面401a延伸进入基材401之中,并且彼此隔离。源极409、漏极410和掺杂区411都具有p型电性。其中,漏极410位于p型阱区403之中;源极409位于n型阱区402之中。栅极结构407位于基材401表面401a上,且与n型阱区402和p型阱区403至少部分重叠。栅极结构406位于基材401表面401a上,且与n型阱区402重叠,并与栅极结构407隔离。掺杂区411位于n型阱区402之中,并且连接栅极结构406和栅极结构407。虚拟栅极结构408位于基材401表面401a上,与p型阱区403重叠;且位于栅极结构407和漏极410之间。浅沟隔离结构440,位于p型阱区403之中,且位于栅极结构407和虚拟栅极结构408

(或位于栅极结构407和漏极411)之间。

60.同样地,按照本发明图4所述的功率半导体元件400的结构,制作出具有不同栅极-源极/漏极重叠长度lov4的多个功率半导体元件400,并记录及分析这些功率半导体元件400的驱动电流(ion)、截止电流(ioff)和最大基材电流(isubmax)的变化。且与现有具有单一p型金属氧化物半导体场效晶体管单元的功率半导体元件的比较例进行比较。

61.请参照图5a至图5c,图5a是绘示图4所提供的功率半导体元件400和比较例的功率半导体元件的栅极-源极/漏极重叠长度-驱动电流(ion)关系曲线图。图5b是绘示图4所提供的功率半导体元件400和比较例的功率半导体元件的栅极-源极/漏极重叠长度-截止电流(ioff)关系曲线图。图5c是绘示图4所提供的功率半导体元件400和比较例的功率半导体元件的栅极-源极/漏极重叠长度-最大基材电流(isubmax)关系曲线图。

62.其中,横轴代表标准化之后的栅极-源极/漏极重叠长度(单位为a.u.),横轴分别代表标准化之后的驱动电流(ion)、截止电流(ioff)和最大基材电流(isubmax)(单位分别为a.u.)。曲线501、502和503分别代表功率半导体元件400的栅极-源极/漏极重叠长度-驱动电流(ion)关系曲线、栅极-源极/漏极重叠长度-截止电流(ioff)关系曲线以及栅极-源极/漏极重叠长度-最大基材电流(isubmax)关系曲线。曲线511、512和513分别代表比较例所提供的功率半导体元的栅极-源极/漏极重叠长度-驱动电流(ion)关系曲线、栅极-源极/漏极重叠长度-截止电流(ioff)关系曲线以及栅极-源极/漏极重叠长度-最大基材电流(isubmax)关系曲线。

63.由图5a至图5c可以看出,在相同栅极-源极/漏极重叠长度下,功率半导体元件400的驱动电流(ion)、截止电流(ioff)和最大基材电流(isubmax),都小于比较例所提供的功率半导体元的驱动电流(ion)、截止电流(ioff)和最大基材电流(isubmax)。可见,和比较例所提供的功率半导体元件相比,当具有相同驱动电流(ion)、截止电流(ioff)和最大基材电流(isubmax)的情况下,功率半导体元件400可以具有较长的栅极-源极/漏极重叠长度,较不易产生热载流子注入(所引发的击穿漏电现象,因此具有较高的操作电压。

64.另外,功率半导体元件400驱动电流(ion)、截止电流(ioff)和最大基材电流(isubmax),随着栅极-源极/漏极重叠长度的增长,并无明显的波动。反观,比较例所提供的功率半导体元件的驱动电流(ion)、截止电流(ioff)和最大基材电流(isubmax)随着栅极-源极/漏极重叠长度的增会长明显飙高。显示功率半导体元件400,相对于比较例所提供的功率半导体元,件具有较高的设计弹性与操作可靠度。

65.根据上述实施例,本发明是在提供一种功率半导体元件包括至少二个金属氧化物半导体场效晶体管元件,其在源极和漏极之间至少形成彼此分隔的第一栅极结构和第二栅极结构,再以一个掺杂区将此二个栅极结构电连接在一起。其中,此一掺杂区的电性与源极和漏极相同,用于使第一栅极结构与源极和漏极组合形成一个第一晶体管单元;使第二栅极结构与掺杂区和漏极的组合形成一个第二晶体管单元,并与第一晶体管单元彼此串连。通过此一设计可以在不过度延长栅极长度的前提下,提高功率半导体元件的操作电压以及可靠度。

66.虽然结合以上优选实施例公开了本发明,然而其并非用以限定本发明,任何该技术领域中具有通常知识者,在不脱离本发明的精神和范围内,可作些许的更动与润饰,因此本发明的保护范围应当以附上的权利要求所界定的为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。