1.本技术涉及数据存取技术领域,具体涉及一种数据存取方法、数据存储方法及数据存取控制器。

背景技术:

2.存储器中有些数据很重要,例如关键参数,如果读取和/或写入的数据有误,将影响存储器的正常工作甚至导致存储器不能工作,进而致使存储器的可靠性降低。

3.有鉴于此,有必要提供一种数据存取方法、数据存储方法及数据存取控制器,以提高存储器的可靠性。

技术实现要素:

4.本技术提供一种数据存取方法、数据存储方法及数据存取控制器,以缓解存储器可靠性较低的技术问题。

5.第一方面,本技术提供一种数据存取方法,其包括:获取与已写入数据对应的x个存储后编码,x为大于或者等于3的奇数;比较并择取x个存储后编码中相同位上码值相一致的各众数者;根据存储后编码的位序,确定各众数者为标的编码;基于标的编码,得到与已写入数据对应的标的读取数据。

6.在其中一些实施方式中,存储后编码包括存储后原码、存储后补码以及存储后反码中的任一种;数据存取方法还包括:若存储后编码为存储后补码或者存储后反码,则转换存储后补码或者存储后反码为对应原码;比较并择取多个对应原码或者存储后原码中相同位上码值相一致的各众数者;根据存储后编码的位序,确定各众数者为标的原码;基于标的原码,得到与已写入数据对应的标的读取数据。

7.在其中一些实施方式中,存储后编码包括存储后原码、存储后补码以及存储后反码中的任两种;数据存取方法还包括:若任两种包括存储后补码和/或存储后反码,则转换存储后补码和/或存储后反码为对应的第一对应原码和/或第二对应原码;若任两种包括存储后原码,则确定存储后原码为第三对应原码;比较并择取第一对应原码、第二对应原码以及第三对应原码中所存在的两种在相同位上码值相一致的各众数者;根据存储后编码的位序,确定各众数者为标的原码;基于标的原码,得到与已写入数据对应的标的读取数据。

8.在其中一些实施方式中,存储后编码包括第一码、第二码以及第三码,当第一码和第二码一致时,得到的第一比较结果即作为标的读取数据;当第一码和第二码不一致时,记录第一比较结果;第一码/第二码中的一个与第三码进行比较,记录第二比较结果;第一码/第二码中的另一个与第三码进行比较,记录第三比较结果;确定第一比较结果、第二比较结果以及第三比较结果中相同者为标的读出数据;其中,第一码为原码、补码以及反码中的一个,第二码为原码、补码以及反码中的另一个,第三码为原码、补码以及反码中的再一个。

9.在其中一些实施方式中,存储后编码包括存储后原码、存储后补码以及存储后反码;数据存取方法还包括:配置存储后原码、存储后补码以及存储后反码的个数依次分别为

j、k、l,j、k、l均为大于或者等于3的奇数;比较并择取j个存储后原码中相同位上码值相一致的各众数者;根据存储后原码的位序,确定各众数者为第一标的子原码;比较并择取k个存储后补码中相同位上码值相一致的各众数者;根据存储后补码的位序,确定各众数者为标的子补码;转换标的子补码为对应的第二标的子原码;比较并择取l个存储后反码中相同位上码值相一致的各众数者;根据存储后反码的位序,确定各众数者为标的子反码;转换标的子反码为对应的第三标的子原码;比较并择取第一标的子原码、第二标的子原码以及第三标的子原码中相同位上码值相一致的各众数者;根据存储后编码的位序,确定各众数者为标的原码;基于标的原码,得到与已写入数据对应的标的读取数据。

10.在其中一些实施方式中,数据存取方法还包括:转码待写入数据为与待写入数据对应的x个存储前编码;存储x个存储前编码以得到x个存储后编码。

11.第二方面,本技术提供一种数据存储方法,其包括:转码待写入数据为与待写入数据对应的x个存储前编码,x为大于或者等于3的奇数;存储x个存储前编码中的每个至不同的存储空间,以得到x个存储后编码。

12.在其中一些实施方式中,数据存储方法还包括:配置x个存储前编码包括j个存储前原码、k个存储前补码以及l个存储前反码,j、k、l均为大于或者等于3的奇数;存储每个存储前原码于不同的第一存储空间;存储每个存储前补码于不同的第二存储空间;存储每个存储前反码于不同的第三存储空间。

13.在其中一些实施方式中,每个第一存储空间、第二存储空间或者第三存储空间均包括一个或者多个相互离散的存储地址,每个存储地址对应一个存储单元。

14.第三方面,本技术提供一种数据存取控制器,其包括获取模块、比较选择模块、确定模块以及译码模块,获取模块用于获取与已写入数据对应的x个存储后编码,x为大于或者等于3的奇数;比较选择模块用于比较并择取x个存储后编码中相同位上码值相一致的各众数者;确定模块用于根据存储后编码的位序确定各众数者为标的编码;译码模块用于基于标的编码得到与已写入数据对应的标的读取数据。

15.本技术提供的数据存取方法、数据存取控制器,通过获取多个与已写入数据对应的存储后编码,再通过比较、选择x个存储后编码中相同位上码值相一致的各众数者,然后按照存储后编码的位序排列各众数者为标的编码,最后对该标的编码进行对应译码,得到与已写入数据对应的标的读取数据,可以减少或者避免电气性能和/或环境因素等导致数据读取的不准确性,进而提高了存储器的可靠性。

16.又,本技术提供的数据存储方法,通过对待写入数据进行转码可以得到x个与待写入数据对应的存储前编码,并存储x个存储前编码中的每个至不同的存储空间,如此,即使存在小部分的电气性能和/或环境因素等导致的错误写入结果,但是仍有大部分的正确写入结果,相较于单码单次写入和/或连续写入,提高了写入的正确率,进而提高了存储器的可靠性。

附图说明

17.下面结合附图,通过对本技术的具体实施方式详细描述,将使本技术的技术方案及其它有益效果显而易见。

18.图1为本技术实施例提供的数据存储方法的一种流程示意图。

19.图2为本技术实施例提供的数据存储方法的另一种流程示意图。

20.图3为本技术实施例提供的数据存取方法的一种流程示意图。

21.图4为本技术实施例提供的数据存取方法的另一种流程示意图。

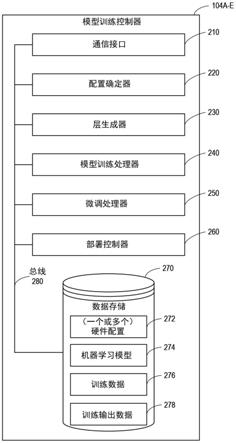

22.图5为本技术实施例提供的数据存取控制器的结构示意图。

具体实施方式

23.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

24.有鉴于现有存储器可靠性较低的缺陷,在其中一个实施例中,如图1所示,本实施例提供一种数据存储方法,其包括以下步骤:

25.步骤s100:转码待写入数据为与待写入数据对应的x个存储前编码,x为大于或者等于3的奇数。

26.步骤s200:存储x个存储前编码中的每个至不同的存储空间,以得到x个存储后编码。

27.可以理解的是,本实施例的数据存储方法,通过对待写入数据进行转码可以得到x个与待写入数据对应的存储前编码,并存储x个存储前编码中的每个至不同的存储空间,如此,即使存在小部分的电气性能和/或环境因素等导致的错误写入结果,但是仍有大部分的正确写入结果,相较于单码单次写入和/或连续写入,提高了写入的正确率,进而提高了存储器的可靠性。

28.需要进行说明的是,上述存储前编码可以为存储前原码、存储前补码以及存储前反码中的至少一种,存储前原码可以属于原码,存储前补码可以属于补码,存储前反码可以属于反码。其中,原码可以为待写入数据对应的机器数或者二进制数据。反码可以通过原码中各个位上的值取反得到,或者,也可以直接转码待写入数据为对应的反码。补码可以通过在反码的基础上加“1”得到,或者,也可以直接转码待写入数据为对应的补码。

29.其中,对应的原码存储于对应的存储地址或者存储空间之前即为存储前原码。对应的补码存储于对应的存储地址或者存储空间之前即为存储前补码。对应的反码存储于对应的存储地址或者存储空间之前即为存储前反码。

30.在其中一个实施例中,数据存储方法还可以包括:配置x个存储前编码包括j个存储前原码、k个存储前补码以及l个存储前反码,j、k、l均为大于或者等于3的奇数;存储每个存储前原码于不同的第一存储空间;存储每个存储前补码于不同的第二存储空间;存储每个存储前反码于不同的第三存储空间。

31.其中,一个存储空间可以包括至少一个存储单元,每个存储单元对应一个存储地址,每个存储单元可以存储1byte的数据。

32.每个存储空间中各存储单元的存储地址可以为连续或者离散的。其中,同一编码可以优选地存储于一个或者多个存储地址连续的存储单元中。

33.需要进行说明的是,在本实施例中,配置各编码于不同的存储地址或者存储空间可以有效避免存储过程中受到干扰导致待写入数据在存储的过程中发生变化,致使存储芯

片的工作可靠性降低。

34.具体地,如图2所示,数据存储的过程可以为如下:

35.首先,转码:转换待写入数据为data0原码,该data0原码为机器数,优选地,可以基于该data0原码取反得到data0反码,然后在data0反码的最低位加“1”得到data0补码。

36.然后,可以于addr0存储data0原码,addr1存储data0补码,addr2存储data0反码。其中,addr0、addr1以及addr2均可以表征至少一个存储地址。

37.优选地,可以于addr0 n中再次存储data0原码,于addr1 n中再次存储data0补码,于addr2 n中再次存储data0反码。同理,addr0 n、addr1 n以及addr2 n均可以表征至少一个存储地址。其中,n为正整数,可以根据存储的空间合理配置其数值,以避免不同的data0原码、data0补码以及data0反码存储于重复的地址单元中。

38.优选地,还可以于addr0 2n中再次存储data0原码,addr1 2n中再次存储data0补码,于addr2 2n中再次存储data0反码等等,如此可以根据需要进行多次存储,需要进行说明的是,该多次存储也可以于一次中存储完毕,也可以根据需要分次存储。其中,addr0 2n、addr1 2n以及addr2 2n也均可以表征至少一个存储地址。

39.一般而言,当一个存储单元受到干扰或出现故障时,该存储单元相邻的存储单元也会受到影响。而本实施例中,由于比如采用原码、补码、反码这种顺序的存储形式,能够有效避免当一个存储单元受到干扰或出现故障时,影响到相邻的存储单元,而导致的数据整体出错。尤其当多次存储时,能有效避免相邻存储单元受到的影响。

40.有鉴于现有存储器可靠性较低的缺陷,本实施例提供了一种数据存取方法,如图3所示,其包括以下步骤:

41.步骤s10:获取与已写入数据对应的x个存储后编码,x为大于或者等于3的奇数。

42.步骤s20:比较并择取x个存储后编码中相同位上码值相一致的各众数者。

43.步骤s30:根据存储后编码的位序,确定各众数者为标的编码。

44.步骤s40:基于标的编码,得到与已写入数据对应的标的读取数据。

45.可以理解的是,本实施例提供的数据存取方法,通过获取多个与已写入数据对应的存储后编码,再通过比较、选择x个存储后编码中相同位上码值相一致的各众数者,然后按照存储后编码的位序排列各众数者为标的编码,最后对该标的编码进行对应译码,得到与已写入数据对应的标的读取数据,可以减少或者避免电气性能和/或环境因素等导致数据读取的不准确性,进而提高了存储器的可靠性。

46.其中,对应的存储前原码存储于对应的存储地址或者存储空间之后即为存储后原码。同理,对应的存储前补码存储于对应的存储地址或者存储空间之后即为存储后补码。对应的存储前反码存储于对应的存储地址或者存储空间之后即为存储后反码。

47.在一些实施例中,当第一码和第二码一致时,得到第一比较结果即作为标的读取数据;当第一码和第二码不一致时,记录第一比较结果,并将第一码/第二码和第三码进行比较,记录第二比较结果,接着将第二码/第一码和第三码进行比较,记录第三比较结果;比较第一、第二、第三比较结果,取两者相同的为读出数据。其中,第一、第二、第三码可以分别为原码、补码、反码中的一个。由于将数据存储了三次,如此既避免了逻辑死循环,又提升了比较效率,还保证了数据的准确性。

48.在其中一个实施例中,存储后编码包括存储后原码、存储后补码以及存储后反码

中的任一种;数据存取方法还包括:若存储后编码为存储后补码或者存储后反码,则转换存储后补码或者存储后反码为对应原码;比较并择取多个对应原码或者存储后原码中相同位上码值相一致的各众数者;根据存储后编码的位序,确定各众数者为标的原码;基于标的原码,得到与已写入数据对应的标的读取数据。

49.例如,x个存储后编码若为3个存储后原码,该3个存储后原码例如均为001,则该3个存储后原码中最低位上码值相一致的众数者为1,该3个存储后原码中次低位上码值相一致的众数者为0,该3个存储后原码中最高位上码值相一致的众数者为0,根据存储后编码的位序即对应码值归位至对应的最低位、次低位...以及最高位,即得到标的原码为001。

50.同理,x个存储后编码若为3个存储后反码,该3个存储后反码例如均为110,对该存储后反码进行对应转换后即得到上述的对应原码为001,则该3个对应原码中最低位上码值相一致的众数者为1,该3个对应原码中次低位上码值相一致的众数者为0,该3个对应原码中最高位上码值相一致的众数者为0,根据存储后编码的位序即对应码值归位至对应的最低位、次低位...以及最高位,即得到标的原码为001。

51.同理,x个存储后编码若为3个存储后补码,该3个存储后补码例如均为111,对该存储后补码进行对应转换后即得到上述的对应原码为001,则该3个对应原码中最低位上码值相一致的众数者为1,该3个对应原码中次低位上码值相一致的众数者为0,该3个对应原码中最高位上码值相一致的众数者为0,根据存储后编码的位序即对应码值归位至对应的最低位、次低位...以及最高位,即得到标的原码为001。

52.在其中一个实施例中,存储后编码包括存储后原码、存储后补码以及存储后反码中的任两种;数据存取方法还包括:若任两种包括存储后补码和/或存储后反码,则转换存储后补码和/或存储后反码为对应的第一对应原码和/或第二对应原码;若任两种包括存储后原码,则确定存储后原码为第三对应原码;比较并择取第一对应原码、第二对应原码以及第三对应原码中所存在的两种在相同位上码值相一致的各众数者;根据存储后编码的位序,确定各众数者为标的原码;基于标的原码,得到与已写入数据对应的标的读取数据。

53.例如,x个存储后编码若为1个存储后原码001和2个存储后反码110,则转换该存储后反码110为第二对应原码001,则该1个存储后原码001、2个第二对应原码001中最低位上码值相一致的众数者为1,该1个存储后原码001、2个第二对应原码001中次低位上码值相一致的众数者为0,该1个存储后原码001、2个第二对应原码001中最高位上码值相一致的众数者为0,根据存储后编码的位序即对应码值归位至对应的最低位、次低位...以及最高位,即得到标的原码为001。

54.同理,x个存储后编码若为1个存储后原码001和2个存储后补码111,则转换该存储后补码111为第一对应原码001,则该1个存储后原码001、2个第一对应原码001中最低位上码值相一致的众数者为1,该1个存储后原码001、2个第一对应原码001中次低位上码值相一致的众数者为0,该1个存储后原码001、2个第一对应原码001中最高位上码值相一致的众数者为0,根据存储后编码的位序即对应码值归位至对应的最低位、次低位...以及最高位,即得到标的原码为001。

55.同理,x个存储后编码若为1个存储后反码110和2个存储后补码111,则转换该存储后补码111为第一对应原码001,转换该存储后反码110为第二对应原码001,则该1个第二对应原码001、2个第一对应原码001中最低位上码值相一致的众数者为1,该1个第二对应原码

001、2个第一对应原码001中次低位上码值相一致的众数者为0,该1个第二对应原码001、2个第一对应原码001中最高位上码值相一致的众数者为0,根据存储后编码的位序即对应码值归位至对应的最低位、次低位...以及最高位,即得到标的原码为001。

56.在其中一个实施例中,存储后编码包括存储后原码、存储后补码以及存储后反码;数据存取方法还包括:配置存储后原码、存储后补码以及存储后反码的个数依次分别为j、k、l,j、k、l均为大于或者等于3的奇数;比较并择取j个存储后原码中相同位上码值相一致的各众数者;根据存储后原码的位序,确定各众数者为第一标的子原码。

57.例如,取j为3,存储后原码均为001,则该3个存储后原码中最低位上码值相一致的众数者为1,该3个存储后原码中次低位上码值相一致的众数者为0,该3个存储后原码中最高位上码值相一致的众数者为0,根据存储后原码的位序即对应码值归位至对应的最低位、次低位...以及最高位,即得到第一标的子原码为001。

58.在其中一个实施例中,数据存取方法还包括:比较并择取k个存储后补码中相同位上码值相一致的各众数者;根据存储后补码的位序,确定各众数者为标的子补码;转换标的子补码为对应的第二标的子原码。

59.例如,取k为3,存储后补码均为111,则该3个存储后补码中最低位上码值相一致的众数者为1,该3个存储后补码中次低位上码值相一致的众数者为1,该3个存储后补码中最高位上码值相一致的众数者为1,根据存储后补码的位序即对应码值归位至对应的最低位、次低位...以及最高位,即得到标的子补码为111,然后转换该标的子补码为111为对应的第二标的子原码为001。

60.在其中一个实施例中,数据存取方法还包括:比较并择取l个存储后反码中相同位上码值相一致的各众数者;根据存储后反码的位序,确定各众数者为标的子反码;转换标的子反码为对应的第三标的子原码。

61.例如,取l为3,存储后反码均为110,则该3个存储后反码中最低位上码值相一致的众数者为0,该3个存储后反码中次低位上码值相一致的众数者为1,该3个存储后反码中最高位上码值相一致的众数者为1,根据存储后反码的位序即对应码值归位至对应的最低位、次低位...以及最高位,即得到标的子反码为110,然后转换该标的子反码为110为对应的第三标的子原码为001。

62.在其中一个实施例中,数据存取方法还包括:比较并择取第一标的子原码、第二标的子原码以及第三标的子原码中相同位上码值相一致的各众数者;根据存储后编码的位序,确定各众数者为标的原码;基于标的原码,得到与已写入数据对应的标的读取数据。

63.例如,承上,第一标的子原码、第二标的子原码以及第三标的子原码均为001,则第一标的子原码、第二标的子原码以及第三标的子原码中最低位上码值相一致的众数者为1,第一标的子原码、第二标的子原码以及第三标的子原码中次低位上码值相一致的众数者为0,第一标的子原码、第二标的子原码以及第三标的子原码中最高位上码值相一致的众数者为0,根据存储后编码的位序即对应码值归位至对应的最低位、次低位...以及最高位,得到标的原码为001。

64.基于上述可知,即使所有存储后编码中的少数者发生写入或者读出错误时,经过本技术的对应处理后,仍然可以确定标的原码为存储前的原码,因此,其可以降低或者避免数据存储错误的发生概率。

65.如图4所示,上述数据存取的具体过程也可以为如下所示:

66.可以同时读出addr0、addr3以及addr0 n中对应存储的data0原码。其中,addr0、addr3以及addr0 n均可以包括至少一个存储地址。

67.比较addr0、addr3、addr0 n的对应存储的data0原码的第0位,因取到的data0原码是奇数个,那么第0位比较得到“1”值多,那么取1;如果第0位比较得到“0”值多,那么取0。

68.接着比较addr0、addr3、addr0 n的对应存储的data0原码的第1位、第2位...第7位等等,依次类推。

69.然后可以得到新的原码数据data0_cmp。

70.同理,可以同时读出addr1、addr4以及addr1 n对应存储的data0补码。其中,addr1、addr4以及addr1 n均可以包括至少一个存储地址。

71.比较addr1、addr4、addr1 n的对应存储的data0补码的第0位,因取到的data0补码是奇数个,那么第0位比较得到“1”值多,那么取1;如果第0位比较得到“0”值多,那么取0。

72.接着比较addr1、addr4、addr1 n的对应存储的data0补码的第1位、第2位...第7位等等,依次类推。

73.然后可以得到新的补码数据,对该新的补码数据进行转码得到对应的新的原码数据data0_cmp_p。

74.同理,可以同时读出addr2、addr5以及addr2 n对应存储的data0反码。其中,addr2、addr5以及addr2 n均可以包括至少一个存储地址。

75.比较addr2、addr5、addr2 n的对应存储的data0反码的第0位,因取到的data0反码是奇数个,那么第0位比较得到“1”值多,那么取1;如果第0位比较得到“0”值多,那么取0。

76.接着比较addr2、addr5以及addr2 n的对应存储的data0反码的第1位、第2位...第7位等等,依次类推。

77.然后可以得到新的反码数据,对该新的反码数据进行转码得到对应的新的原码数据data0_cmp_i。

78.最后,比较并择取原码数据data0_cmp、原码数据data0_cmp_p以及原码数据data0_cmp_i中相同位上码值相一致的各众数者,根据存储后编码的位序整合该各众数者以得到标的原码,输出数据即为该标的原码对应的待读出的标的读取数据。

79.在其中一个实施例中,如图5所示,本实施例提供一种数据存取控制器,其包括获取模块100、比较选择模块200、确定模块300以及译码模块400,获取模块100用于获取与已写入数据对应的x个存储后编码,x为大于或者等于3的奇数;比较选择模块200用于比较并择取x个存储后编码中相同位上码值相一致的各众数者;确定模块300用于根据存储后编码的位序确定各众数者为标的编码;译码模块400用于基于标的编码得到与已写入数据对应的标的读取数据。

80.其中,获取模块100的输出端可以与比较选择模块200的输入端电性连接,比较选择模块200的输出端可以与确定模块300的输入端电性连接,确定模块300的输出端可以与译码模块400的输入端电性连接,译码模块400的输出端用于输出标的读取数据。

81.可以理解的是,本实施例提供的数据存取控制器,通过获取多个与已写入数据对应的存储后编码,再通过比较、选择x个存储后编码中相同位上码值相一致的各众数者,然后按照存储后编码的位序排列各众数者为标的编码,最后对该标的编码进行对应译码,得

到与已写入数据对应的标的读取数据,可以减少或者避免电气性能和/或环境因素等导致数据读取的不准确性,进而提高了存储器的可靠性。

82.在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。

83.以上对本技术实施例所提供的数据存取方法、数据存储方法及数据存取控制器进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的技术方案及其核心思想;本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例的技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。