用于加速存储器复制操作的自适应管线选择

背景技术:

1.概括地说,本发明的领域涉及计算系统中的存储器复制操作,并且更具体地说,本发明的领域涉及通过选择性地使用处理器核心管线或直接存储器存取(dma)管线来加速存储器复制操作。

2.一些处理器包括有效地执行存储器复制操作的dma引擎。在由dma引擎传输数据期间,不需要处理器干预。因此,在涉及大量数据移动的场景中使用dma引擎不仅可以潜在地提高存储器复制操作的性能,还可以节省宝贵的处理器资源。然而,利用dma引擎实现最佳系统性能并不简单。存在几个因素,包括复制缓冲器长度和复制操作的数量,这些因素可能会显著影响dma引擎存储器复制操作的性能。

3.在实际场景中,虚拟机(vm)和主机应用的工作负载特征具有非常大的差异。例如,存储器内键值存储(imkv)中的对象长度从字节到兆字节不等。由于设置存储器复制操作所需的开销,某些imkv工作负载可能变得太小而不适用于dma引擎加速。静态处理器管线和dma引擎管线设计会导致严重的资源利用不足,从而导致计算系统的性能欠佳。

附图说明

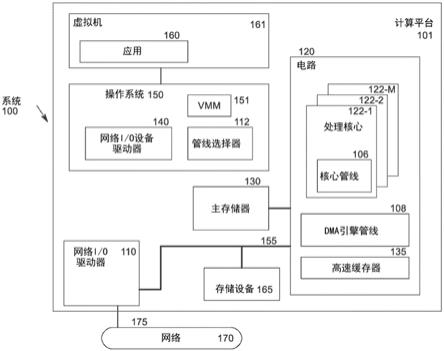

4.图1示出了根据一些实施例的示例计算系统。

5.图2示出了根据一些实施例的、与虚拟机管理器交互的虚拟机的示例。

6.图3示出了根据一些实施例的自适应管线选择系统的示例。

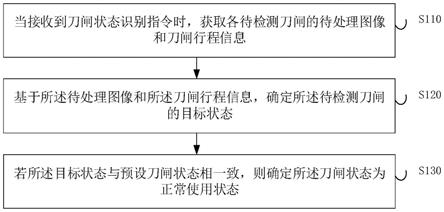

7.图4是根据一些实施例的、针对存储器复制操作选择管线的示例过程的流程图。

8.图5是根据一些实施例的、处理存储器复制操作的描述符的第一遍的示例的流程图。

9.图6是根据一些实施例的、处理存储器复制操作的描述符的第二遍的示例的流程图。

10.图7是根据一些实施例的、处理存储器复制操作的示例的流程图。

11.图8示出了存储介质的示例。

12.图9示出了另一个示例计算平台。

具体实施方式

13.本发明的实施例提供了自适应处理器核心管线和dma引擎管线设计,以在运行时期间根据工作负载特性灵活地选择最合适的底层计算硬件来最优地执行针对多样化和动态工作负载的存储器复制操作。

14.在运行虚拟机(vm)和应用之前(例如,在计算系统的初始化期间),本发明的实施例确定计算系统的多个阈值。在实施例中,阈值包括阈值复制长度和复制操作的阈值数量。在运行时期间,实施例动态地概述每个传入分组的分组缓冲器长度以及要在一批传入分组中处理的存储器复制操作的数量;并且至少部分地基于该概述和阈值,实施例选择处理器核心管线或dma引擎管线来针对该批次传入分组的一部分执行存储器复制操作。

15.在本发明的实施例中,dma引擎管线的性能受到要被复制的分组缓冲器长度和存储器复制操作的数量的影响。此外,调用dma引擎来复制数据需要处理器按门铃并轮询dma引擎的存储器映射的输入/输出(i/o)(mmio)状态寄存器以检查数据传输是否完成。

16.在示例计算系统中,测得当分组缓冲器长度小于或等于1,024字节时,处理器核心在存储器复制操作方面达到了比dma引擎更高的性能。dma引擎仅在分组缓冲器长度大于1,024字节后才优于处理器核心。当与处理器高速缓存到存储器复制操作相比时,dma引擎显示出类似的特性。因此,如果将dma引擎用于存储器复制操作以实现比处理器核心更高的性能,则分组缓冲器长度必须大于第一确定阈值。在一个实施例中,第一确定阈值(例如,阈值复制长度为1,024字节)。在其他计算系统中,可以使用阈值复制长度的另一个值。

17.在一些计算系统中,可以测得,当存储器复制操作的数量(每批)大于或等于8时,针对所有分组缓冲器长度,dma引擎优于处理器核心;在其他情况下,处理器核心实现更高的性能。因此,如果使用dma引擎来实现比处理器核心更高的性能,则存储器复制操作的数量必须大于第二确定阈值。在一个实施例中,第二确定阈值(例如,复制操作的阈值数量)是八。在其他计算系统中,可以使用复制操作的阈值数量的另一个值。

18.通常,在vm中以及在应用中运行的工作负载在分组缓冲器长度方面具有很大差异。例如,存储器内键值存储(imkv)存储各种键值对象,例如用户帐户状态和媒体数据。imkv对象的长度从几个字节到几兆字节不等(在一个示例中,从128字节到100万字节(mb))。在一些情况下,分组太小而不适合用于存储器复制操作的dma引擎加速。将不合适的工作负载卸载到dma引擎会降低系统性能。因此,本发明的实施例提供了自适应处理器核心和dma引擎管线选择过程,以将工作负载动态地分配给适当的硬件以便有效地执行存储器复制操作。

19.图1示出了示例计算系统100。如图1所示,计算系统100包括耦合到网络170(例如可以是互联网)的计算平台101。在一些示例中,如图1所示,计算平台101经由网络通信信道175并通过至少一个网络(nw)输入/输出(i/o)设备110耦合到网络170。在实施例中,网络i/o设备110包括交换机、具有连接到或耦合到网络通信信道175的一个或多个目的地端口(未示出)的网络接口控制器(nic)。在实施例中,网络通信信道175包括phy设备(未示出)。在实施例中,网络i/o设备110包括以太网nic。网络i/o设备110通过网络170将数据分组从计算平台101发送到其他目的地,并从其他目的地接收数据分组以转发到计算平台101。

20.根据一些示例,如图1所示,计算平台101包括电路120、主存储器130、操作系统(os)150、nw i/o设备驱动器140、虚拟机管理器(vmm)(也被称为管理程序)151、在虚拟机(vm)161中运行的至少一个应用160、管线选择器112,以及一个或多个存储设备165。在一个实施例中,os 150是linux

tm

。在另一实施例中,os 150是服务器。也可以使用其他os。网络i/o设备驱动器140操作以初始化和管理由网络i/o设备110执行的i/o请求。在实施例中,发送到网络i/o设备110和/或从网络i/o设备110接收的分组和/或分组元数据存储在主存储器130和/或存储设备165中的一个或多个中。在一个实施例中,应用160是在用户模式下操作的分组处理应用。

21.在实施例中,管线选择器112(下文进一步描述)是os的一部分。在另一个实施例中,管线选择器112是存储器设备驱动器(未示出)的一部分。在另一个实施例中,管线选择器112在电路120中实现。

22.在至少一个实施例中,存储设备165可以是硬盘驱动器(hdd)和/或固态驱动器(ssd)中的一个或多个。在实施例中,存储设备165可以是非易失性存储器(nvm)。在一些示例中,如图1所示,电路120可以经由通信链路155通信地耦合到网络i/o设备110。在一个实施例中,通信链路155是符合pci特别兴趣组(pci-sig)发布的pcie标准的3.0版或其他版本的快速外围组件接口(pcie)总线。

23.在一些示例中,操作系统150、nw i/o设备驱动器140、管线选择器112、vm 161以及应用160是至少部分地经由包括在主存储器130中的一个或多个存储器设备(例如,易失性或非易失性存储器设备)、存储设备165以及电路120的元件(例如处理核心122-1至122-m)之间的协作实现的,其中,“m”是大于2的任何正整数。在实施例中,os 150、vmm 151、nw i/o设备驱动器140、管线选择器112、vm 161和应用160由一个或多个处理核心122-1至122-m执行。

24.在一些示例中,计算平台101包括但不限于服务器、服务器阵列或服务器群、web服务器、网络服务器、互联网服务器、工作站、微型计算机、大型计算机、超级计算机、网络设备、web设备、分布式计算系统、多处理器系统、基于处理器的系统、膝上型计算机、平板计算机、智能手机、片上系统(soc),或其组合。在一个示例中,计算平台101是分解服务器。分解服务器是将组件和资源分解为子系统(例如,网络板(sled))的服务器。分解服务器可以根据需要适用于变化的存储或计算负载,而无需在很长一段时间内更换或中断整个服务器。例如,服务器可以被分解为可以在其他附近的服务器之间共享的模块化计算、i/o、电源和存储模块。

25.具有处理核心122-1至122-m的电路120可以包括各种商用处理器,包括但不限于core(2)core i3、core i5、core i7、或xeon处理器、arm处理器以及类似处理器。电路120可以包括用于存储数据的至少一个高速缓存器135。在一些实施例中,电路120包括dma引擎管线108以执行去往和来自主存储器130的存储器复制操作。在一些实施例中,每个处理核心包括用于执行指令的核心管线106,这些指令包括用于去往和来自主存储器130的存储器复制操作的指令。

26.根据一些示例,主存储器130可由一个或多个存储器设备或管芯组成,其可以包括各种类型的易失性和/或非易失性存储器。易失性类型的存储器可以包括但不限于动态随机存取存储器(dram)、静态随机存取存储器(sram)、晶闸管ram(tram)或零电容ram(zram)。非易失性类型的存储器可以包括具有3维(3-d)交叉点存储器结构的字节或块可寻址类型的非易失性存储器,该3维(3-d)交叉点存储器结构包括硫属化物相变材料(例如,硫属化物玻璃),在下文中被称为“3-d交叉点存储器”。非易失性类型的存储器还可以包括其他类型的字节或块可寻址非易失性存储器,例如但不限于多阈值级nand闪存、nor闪存、单级或多级相变存储器(pcm)、电阻式存储器、纳米线存储器、铁电晶体管随机存取存储器(fetram)、采用忆阻器技术的磁阻式随机存取存储器(mram)、自旋转移扭矩mram(stt-mram),或者上述任何一项的组合。在另一实施例中,主存储器130可以包括计算平台101内和/或可由计算平台101访问的一个或多个硬盘驱动器。

27.其中自适应地选择dme引擎管线108或核心管线106以加速存储器复制操作的一个示例在实现virtio(如在www.linux-kvm.org上所描述的)时是有利的。virtio是用于vm和

主机通信的半虚拟i/o标准。在virtio中,主机(例如,os 150)通过复制来自vm的存储器(例如,主存储器130的一部分)和去往vm的存储器的分组来与vm 161通信。当启用tcp片段卸载时,vm可以使用非常大的tcp分组(例如64千字节(kb))来减轻每分组的处理开销。然而,复制主存储器130中的大量数据的开销使得virtio主机接口成为i/o瓶颈。

28.图2示出了根据一些实施例的、与虚拟机管理器交互的虚拟机的示例200。vm161中的virtio前端204和vmm 151中的virtio后端216利用virtio环,被称为virtqueue(在图2中示为队列206、208),来实现数据交换。virtqueue上的tx(例如,出队)操作210包括前端204向后端216发送数据,并且virtqueue上的rx(例如,入队)操作212包括后端216向前端204发送数据。在tx和rx操作二者中,后端216需要复制在主存储器130中的vm的存储器和vmm的存储器之间的分组缓冲器。

29.在virtio中,每个tx/rx操作可以生成与通过的缓冲器数量一样多的存储器副本。在后端216,处理器周期用于执行存储器复制操作。此外,通过在vm中启用tcp片段卸载和用户数据协议(udp)分段卸载,tcp/udp分组长度可达64kb,这远大于默认的最大传输单元(mtu)的大小1,500字节。因此,复制大量数据的开销使得virtio后端216成为联网i/o瓶颈。

30.尽管本文中讨论了virtio,但其他虚拟设备(例如,可从vmware,inc.购买的vmxnet3,以及可从微软公司购买的vmbus)可以使用本发明的实施例的方法来使用dma引擎管线实现存储器复制加速。

31.图3示出了根据一些实施例的自适应管线选择器系统的示例300。描述符302用于描述用于执行存储器复制操作的请求。在实施例中,用于存储器复制操作目的的每个数据分组由描述符描述。描述符由描述符处理管线304处理。在实施例中,描述符处理管线304包括至少一个核心管线106和至少一个dma引擎管线108。调度器310确定如何以及何时将存储器复制操作插入到所选择的管线中。本发明的实施例包括管线选择器112以确定哪个管线将处理每个描述符(例如,导致复制请求的执行)。当管线选择器112选择核心管线106时,则核心管线106执行指令以执行由描述符描述的存储器复制操作。当管线选择器112选择dma引擎管线108时,dma引擎管线108针对描述符所描述的分组执行存储器复制操作。在一些实施例中,描述符被分批组装到管线中以提高处理效率。管线选择器112使用阈值复制长度304和复制操作的阈值数量306的值,连同从描述符302获得的值,针对由描述符302描述的分组进行针对存储器复制操作的管线选择。

32.图4是根据一些实施例的、针对存储器复制操作选择管线的示例过程400的流程图。在实施例中,图4的动作由管线选择器112执行。在块402处,在计算平台101的初始化期间,管线选择器112确定要用于管线选择的阈值。在一些实施例中,管线选择器112确定适用于计算平台101的阈值复制长度和复制操作的阈值数量。在其他实施例中也可以使用其他阈值。在实施例中,阈值的值是特定于计算平台的并且可以在主机应用和vm运行之前在计算平台上测量。在块404处,在运行时期间,管线选择器112至少部分地基于为dma引擎管线108选择的批次中的描述符数量、阈值、以及分组的缓冲器长度,来选择核心管线106或dma引擎管线108以对由描述符描述的分组的缓冲器执行存储器复制操作。在实施例中,当针对一批分组中的每个描述符选择管线时,执行一个或多个管线以执行所请求的存储器复制操作。

33.根据本发明的实施例,管线选择处理在两遍中通过一批描述符来执行。

34.图5是根据一些实施例的、处理用于存储器复制操作的描述符的第一遍的示例500的流程图。在实施例中,图5的动作由管线选择器112执行。在块502处,从一批一个或多个描述符中获得描述符。在块504处,如果由描述符描述的分组的缓冲器长度大于或等于阈值复制长度,则针对该描述符预先选择dma引擎管线108。在实施例中,在该批次中针对dma引擎管线预先选择的描述符的数量的计数增加。如果描述符描述的分组的缓冲器长度小于阈值复制长度,则针对该描述符预先选择核心管线106。在块510处,如果在当前批次中有更多的描述符要处理,则处理在块502处继续处理下一个描述符。如果这是批次的结束(例如,该批次的所有描述符都已被处理),则第一遍处理在块512处结束。当第一遍完成时,存在针对批次的每个描述符的管线的初始选择(例如,预先选择)以及针对dma引擎管线108预先选择的描述符的数量的计数。

35.图6是根据一些实施例的、处理用于存储器复制操作的描述符的第二遍的示例600的流程图。在实施例中,图6的动作由管线选择器112执行。在块602处,从该批的一个或多个描述符中获得描述符。在块604处,如果已经针对由dma引擎管线108进行的存储器复制操作处理预先选择了描述符,则处理继续进行到块606。在块606处,如果针对dma引擎管线108预先选择的描述符的数量大于或等于复制操作306的阈值数量,则在块608处针对描述符选择dma引擎管线108。在块604处,如果没有针对由dma引擎管线108进行的存储器复制操作处理预先选择描述符(例如,描述符被预先选择用于核心管线106),则处理继续进行到块610。在块610处,针对描述符选择核心管线106。在块606处,如果针对dma引擎管线108预先选择的描述符的数量小于复制操作306的阈值数量,则在块610处针对描述符选择核心管线106。块608和610之后的处理在块612处继续。在块612处,如果在当前批次中有更多的描述符要处理,则处理在块602处继续处理下一个描述符。如果这是批次的结束(例如,该批次的所有描述符都已被处理),则第二遍处理在块614处结束。该批次的所有描述符现在都已分配给管线用于执行描述符的存储器复制操作。

36.图7是根据一些实施例的、处理存储器复制操作的示例700的流程图。在块702处,管线选择器112针对描述符选择管线(例如,如图4-图6中所描述的)。在块704处,管线选择器112对针对所选择的管线的描述符的复制请求进行批处理。针对批处理中的每个描述符重复块702和704。在块706处,该批次被发送到所选择的管线。即,针对分配给dma引擎管线108的描述符的复制请求被发送到dma引擎管线,并且针对分配给核心管线106的描述符的复制请求被发送到核心管线。在处理完一个批次的所有传入描述符后,执行管线。对于核心管线106,在块708处,核心管线根据描述符将分组缓冲器复制到virtqueue(在virtio的示例中)。在块710处,核心管线返回描述符。对于dma引擎管线108,处理包括五个阶段。对于每个复制请求,dma引擎管线108在块714处将分组缓冲器的虚拟地址(va)转换为物理地址(pa),因为在一些实施例中,dma引擎管线只能处理物理地址。在块716处,dma引擎管线将复制请求入队到dma引擎设备的描述符环。在块718处,dma引擎管线调用dma操作以通过按门铃来传输数据。在按门铃之后,dma数据传输和处理器核心操作可以同时执行。为了减轻门铃开销,dma管线在按门铃之前重复块714和716以便批量复制请求。如果存在未经处理的复制请求,则dma管线重复块714、716和718,直到它们都被分配给dma引擎设备。在块720处,处理器核心等待dma引擎管线完成所有复制请求。最后,在块722处,dma引擎管线将描述符返回到virtqueue(在virtio的示例中)。

37.图8示出了存储介质800的示例。存储介质800可以包括制品。在一些示例中,存储介质800可以包括任何非临时性计算机可读介质或机器可读介质,诸如光、磁或半导体存储。存储介质800可以存储各种类型的计算机可执行指令,例如用于实现上文在图2至图7中描述的逻辑流程的指令802。计算机可读或机器-可读存储介质的示例可以包括能够存储电子数据的任何有形介质,其包括易失性存储器或非易失性存储器、可移动或不可移动存储器,可擦除或不可擦除存储器,可写或可重写存储器,等等。计算机可执行指令的示例可以包括任何合适类型的代码,诸如源代码、编译代码、解释代码、可执行代码、静态代码、动态代码、面向对象的代码、可视代码等等。这些示例并不局限于此上下文。

38.图9示出了示例计算平台900。在一些示例中,如图9所示,计算平台900可以包括处理组件902、其他平台组件904和/或通信接口906。

39.根据一些示例,处理组件902可以执行用于存储在存储介质800上的指令的处理操作或逻辑。处理组件902可以包括各种硬件元件、软件元件或这二者的组合。硬件元件的示例可以包括:器件、逻辑器件、组件、处理器、微处理器、电路、处理器电路、电路元件(例如,晶体管、电阻器、电容器、电感器等)、集成电路、专用集成电路(asic)、可编程逻辑器件(pld)、数字信号处理器(dsp)、现场可编程门阵列(fpga)、存储器单元、逻辑门、寄存器、半导体器件、芯片、微芯片、芯片组,等等。软件元件的示例可以包括:软件组件、程序、应用、计算机程序、应用程序、设备驱动器、系统程序、软件开发程序、机器程序、操作系统软件、中间件、固件、软件模块、例程、子例程、函数、方法、过程、软件接口、应用程序接口(api)、指令集、计算代码、计算机代码、代码段、计算机代码段、字、值、符号、或它们的任意组合。确定使用硬件元件和/或软件元件来实现示例可以根据多种因素而不同,多种因素诸如对于给定的示例所需要的期望的计算速率、功率电平、耐热性、处理周期预算、输入数据速率、输出数据速率、存储器资源、数据总线速度以及其它设计或性能约束。

40.在一些示例中,其它平台组件904可以包括通用计算元件,诸如一个或多个处理器、多核处理器、协处理器、存储器单元、芯片组、控制器、外围设备、接口、振荡器、定时设备、显卡、声卡、多媒体输入/输出(i/o)组件(例如,数字显示器)、电源等等。存储器单元的示例可以包括但不限于一种或多种高速存储器单元形式的各种类型的计算机可读和机器可读存储介质,例如只读存储器(rom)、随机存取存储器(ram)、动态ram(dram)、双倍数据速率dram(ddram)、同步dram(sdram)、静态ram(sram)、可编程rom(prom)、可擦除可编程rom(eprom)、电可擦除可编程rom(eeprom)、各种类型的非易失性存储器,例如可以是可字节寻找或块寻址的3-d交叉点存储器。非易失性类型的存储器还可以包括其他类型的字节或块可寻址非易失性存储器,例如但不限于多阈值级nand闪存、nor闪存、单级或多级pcm、电阻式存储器、纳米线存储器、fetram、结合了忆阻器技术的mram、stt-mram,或者上述任意一项的组合。其他类型的计算机可读和机器可读存储介质也可以包括磁卡或光卡、诸如独立磁盘冗余阵列(raid)驱动器的器件的阵列、固态存储器设备(例如usb存储器)、固态驱动器(ssd)和适用于存储信息的任何其它类型的存储介质。

41.在一些示例中,通信接口906可以包括支持通信接口的逻辑和/或特征。对于这些示例,通信接口906可以包括根据各种通信协议或标准操作以通过直接或网络通信链路或信道进行通信的一个或多个通信接口。直接通信可以经由使用在一个或多个行业标准(包括子代和变体)中描述的通信协议或标准发生,所述通信协议或标准例如与快速外围组件

互连(pcie)规范相关联的那些。网络通信可以经由使用通信协议或标准发生,所述通信协议或标准例如在由电气和电子工程师协会(ieee)颁布的一个或多个以太网标准中描述的那些。例如,一种这样的以太网标准可以包括ieee 802.3。网络通信也可以根据一个或多个开放流规范(例如开放流交换机规范)发生。

42.计算平台900的组件和特征,包括由存储在存储介质800上的指令表示的逻辑,可以使用分立电路、asic、逻辑门和/或单芯片架构的任何组合来实现。此外,计算平台900的特征可以使用微控制器、可编程逻辑阵列和/或微处理器或前述合适的任意组合来实现。应该注意的是:硬件、固件和/或软件元件在本文中被统称为或分别称为“逻辑”或“电路。

43.应该认识到的是:图9的框图中示出的示例性计算平台900可以表示多种潜在实现的一种功能上描述性的示例。因此,对附图中描绘的模块功能的分割、省略或包括并不能推断出用于实现这些功能的硬件组件、电路、软件和/或元件一定被分割、省略或包括在实施例中。

44.可以使用硬件元件、软件元件或二者的组合来来实现各个示例。在一些示例中,硬件元件可以包括设备、组件、处理器、微处理器、电路、电路元件(例如,晶体管、电阻器、电容器、电感器等)、集成电路、asic、可编程逻辑器件(pld)、数字信号处理器(dsp)、fpga、存储器单元、逻辑门、寄存器、半导体器件、芯片、微芯片、芯片组等。在一些示例中,软件元件可以包括:软件组件、程序、应用、计算机程序、应用程序、系统程序、机器程序、操作系统软件、中间件、固件、软件模块、例程、子例程、函数、方法、过程、软件接口、应用程序接口(api)、指令集、计算代码、计算机代码、代码段、计算机代码段、字、值、符号、或它们的任意组合。确定使用硬件元件和/或软件元件来实现示例可以根据多种因素而不同,多种因素诸如对于给定实现所需要的期望的计算速率、功率电平、耐热性、处理周期预算、输入数据速率、输出数据速率、存储器资源、数据总线速度以及其它设计或性能约束。

45.一些示例可以包括制品或至少一种计算机可读介质。计算机可读介质可以包括用于存储逻辑的非暂时性存储介质。在一些示例中,非暂时性存储介质可以包括能够存储电子数据的一种或多种类型的计算机可读存储介质,计算机可读存储介质包括易失性存储器或非易失性存储器、可移动或不可移动存储器,可擦除或不可擦除存储器,可写或可重写存储器等。在一些示例中,逻辑可以包括各种软件元件,例如软件组件、程序、应用、计算机程序、应用程序、系统程序、机器程序、操作系统软件、中间件、固件、软件模块、例程、子例程、函数、方法、过程、软件接口、api、指令集、计算代码、计算机代码、代码段、计算机代码段、字、值、符号、或它们的任意组合。

46.可以使用“在一个示例中”或者“示例”的表述及其衍生物来描述一些示例。这些术语意指结合该示例描述的特定的特征、结构或特性包括在至少一个示例中。在本说明的各个地方出现短语“在一个示例中”并不一定全部指的是相同的示例。

47.本文中包括表示用于执行所公开的架构的新颖方面的示例方法的逻辑流或方案。同时,为简化说明的目的,将本文中所示的一种或多种方法示为和描述为一系列的动作,但本领域技术人员将理解并认识到:这些方法并不受动作顺序的限制。据此,一些动作可以以与本文中描述和示出的顺序不同的顺序发生和/或与其它动作并行发生。例如,本领域技术人员将会理解和意识到,方法能够可替代地表示为一系列相互关联的状态或事件(例如在状态图中)。另外,对于新颖实现来说,并非方法中说明的所有动作都是必需的。

48.逻辑流或方案可以实现为软件、固件和/或硬件。在软件和固件实施例中,逻辑流或方案可由存储在至少一个非临时性计算机可读介质或机器可读介质(诸如光、磁或半导体存储)上的计算机可执行指令来实现。这些实施例并不局限于此上下文。

49.使用“耦合”和“连接”的表述及其衍生物描述了一些示例。这些术语并不一定旨在作为彼此的同义词。例如,使用术语“连接”和/或“耦合”可以指示两个或更多元素彼此直接物理或电接触。然而,术语“耦合”也可以意指两个或更多元素并不彼此直接物理接触,但仍协同操作或彼此交互。

50.应该强调的是:提供了本公开内容的摘要以符合37c.f.r.1.72(b)节,其要求将使读者能够快速确定本技术公开的本质的摘要。基于其将不会被用来解释或限制权利要求的范围或含义的理解来提交摘要。此外,在前面的具体实施方式中,可以看到:出于精简本公开内容的目的,在单个示例中将各个特征组合在一起。本公开内容的方法不应该被解释为反映了以下意图,即:所要求保护的示例需要比明确陈述于每一项权利要求中的更多的特征。而是如同后面的权利要求所反映的,发明主题在于少于单个所公开的示例的所有特征。因此,在每一项权利要求自身作为单独的示例的前提下,在此将后面的权利要求并入具体实施方式。在所附权利要求书中,术语“包括(including)”和“其中(in which)”分别用作相应术语“包括(comprising)”和“其中(wherein)”的通俗英语等同物。另外,术语“第一”、“第二”、“第三”等等仅仅用作标签,且并不意图对它们的对象施加数值要求。

51.虽然以特定于结构特征和/或方法动作的语言对发明主题进行了描述,但应当理解的是:所附权利要求书中定义的发明主题并不一定受限于上述具体特征或动作。而是,上述具体特征或动作作为实现权利要求书的示例形式而公开的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。