1.本发明是一种宽带非线性传输线梳谱发生器芯片,属于微电子与固体电子学的射频微波集成电路技术领域。

背景技术:

2.近年来随着无线通信系统在雷达、制导等不同高端设备上的快速应用,高功率、宽带调制信号更有利于信息的传输。非线性传输线广泛应用于高速采样示波器、时域反射计、梳谱发生器和频率合成器中,非线性传输线梳谱发生器则一般利用信号的高阶脉冲压缩技术,实现低频信号的高次倍频。

3.传统的倍频器一般可实现低次倍频,对于高次倍频,电路设计复杂并且芯片面积大、流片成本高。

技术实现要素:

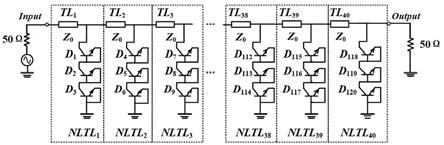

4.本发明提出的是一种工作频率范围宽、谐波输出功率高、倍频次数高、芯片尺寸小的宽带非线性传输线梳谱发生器芯片,其目的在于针对现有技术存在的缺陷,基于非线性传输线与孤子波理论,利用非线性传输线上的孤子波分解特性从而实现高阶梳状谱,提供一种工作频率范围宽、谐波输出功率高、倍频次数高、芯片尺寸小的宽带非线性传输线梳谱发生器。

5.本发明的技术解决方案:一种宽带非线性传输线梳谱发生器芯片,由多级非线性传输线单元周期级联构成,每一级非线性传输单元包括一段高阻微带线和三个晶体管,所述晶体管均基极和发射极短接。

6.所述芯片版图布局采用弯曲折叠走线。

7.所述芯片包括40级非线性传输单元。

8.所述40级非线性传输单元中,第一高阻微带线tl1、第一基极-发射极短接晶体管d1、第二基极-发射极短接晶体管d2、第三基极-发射极短接晶体管d3构成第一非线性传输线单元nltl1,其中,第一高阻微带线tl1的一端作为梳谱发生器的输入端,另一端与第一基极-发射极短接晶体管d1的集电极相连,第一基极-发射极短接晶体管d1的基极与第二基极-发射极短接晶体管d2的集电极相连,第二基极-发射极短接晶体管d2的基极与第三基极-发射极短接晶体管d3的集电极相连,第三基极-发射极短接晶体管d3的基极接地;第二高阻微带线tl2、第四基极-发射极短接晶体管d4、第五基极-发射极短接晶体管d5、第六基极-发射极短接晶体管d6构成第二非线性传输线单元nltl2,其中,第二高阻微带线tl2的一端与第一基极-发射极短接晶体管d1的集电极相连,另一端与第四基极-发射极短接晶体管d4的集电极相连,第四基极-发射极短接晶体管d4的基极与第五基极-发射极短接晶体管d5的集电极相连,第五基极-发射极短接晶体管d5的基极与第六基极-发射极短接晶体管d6的集电极相连,第六基极-发射极短接晶体管d6的基极接地;第三高阻微带线tl3、第七基极-发射极短接晶体管d7、第八基极-发射极短接晶体管d8、第九基极-发射极短接晶体管d9构

成第三非线性传输线单元nltl3,其中,第三高阻微带线tl3的一端与第四基极-发射极短接晶体管d4的集电极相连,另一端与第七基极-发射极短接晶体管d7的集电极相连,第七基极-发射极短接晶体管d7的基极与第八基极-发射极短接晶体管d8的集电极相连,第八基极-发射极短接晶体管d8的基极与第九基极-发射极短接晶体管d9的集电极相连,第九基极-发射极短接晶体管d9的基极接地;以此类推,第四十高阻微带线tl40、第一百一十八基极-发射极短接晶体管d118、第一百一十九基极-发射极短接晶体管d119、第一百二十基极-发射极短接晶体管d120构成第四十非线性传输线单元nltl40,其中,第四十高阻微带线tl40的一端与第一百一十五基极-发射极短接晶体管d115的集电极相连,另一端与第一百一十八基极-发射极短接晶体管d118的集电极相连,第一百一十八基极-发射极短接晶体管d118的基极与第一百一十九基极-发射极短接晶体管d119的集电极相连,第一百一十九基极-发射极短接晶体管d119的基极与第一百二十基极-发射极短接晶体管d120的集电极相连,第一百二十基极-发射极短接晶体管d120的基极接地。

9.所述第一百一十八基极-发射极短接晶体管d118的集电极作为梳谱发生器的输出端。

10.本发明的有益效果:电路拓扑结构简单、工作频率宽,并且通过弯曲折叠走线减小谐波的能量反射,实现了更高的谐波功率输出与更小的芯片尺寸,填补了国内有关高次倍频梳谱发生器芯片的空白。

附图说明

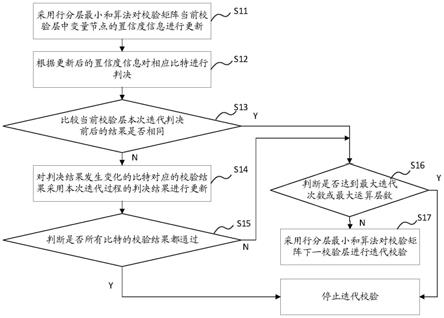

11.图1是宽带非线性传输线梳谱发生器的电路结构图。

12.图2是本发明实施例中宽带非线性传输线梳谱发生器的电路版图;图3是本发明实施例中输入信号1ghz、功率23dbm时,谐波输出功率谱线图;图4是实施例中输入信号1ghz、功率23dbm时,输入、输出信号波形曲线;图5是实施例中输入信号5ghz、功率23dbm时,谐波输出功率谱线图;图6是实施例中输入信号5ghz、功率23dbm时,输入、输出信号波形曲线;图7是实施例中输入信号10ghz、功率23dbm时,谐波输出功率谱线图;图8是实施例中输入信号10ghz、功率23dbm时,输入、输出信号波形曲线。

13.图中tl1-tl40是高阻微带线、d1-120是发射极短接晶体管、nltl140是非线性传输线单元,1是信号输入端口,2是信号输出端口。

具体实施方式

14.一种高功率宽带非线性传输线梳谱发生器芯片。该梳谱发生器芯片由40级非线性传输线单元周期级联构成,其中每个非线性传输线单元由高阻微带线与三个基极-发射极短接的晶体管组成。所述高阻微带线和强非线性变容二极管,二者周期级联构成一段能产生孤波的非线性传输线,利用非线性传输线上孤子波的分解特性得到系列脉冲信号。

15.进一步地,所述输入信号经过非线性传输线后得到高次脉冲信号。

16.作为一种具体示例,所述梳谱发生器芯片由四十级非线性传输线单元周期级联构成,其中包括第一~第四十高阻微带线、第一基极-发射极短接晶体管~第一百二十基极-发射极短接晶体管。

17.第一高阻微带线、第一基极-发射极短接晶体管、第二基极-发射极短接晶体管、第三基极-发射极短接晶体管构成第一非线性传输线单元。其中,第一高阻微带线的一端作为梳谱发生器的输入端,另一端与第一基极-发射极短接晶体管的集电极相连,第一基极-发射极短接晶体管的基极与第二基极-发射极短接晶体管的集电极相连,第二基极-发射极短接晶体管的基极与第三基极-发射极短接晶体管的集电极相连,第三基极-发射极短接晶体管的基极接地。第二高阻微带线、第四基极-发射极短接晶体管、第五基极-发射极短接晶体管、第六基极-发射极短接晶体管构成第二非线性传输线单元。其中,第二高阻微带线的一端与第一基极-发射极短接晶体管的集电极相连,另一端与第四基极-发射极短接晶体管的集电极相连,第四基极-发射极短接晶体管的基极与第五基极-发射极短接晶体管的集电极相连,第五基极-发射极短接晶体管的基极与第六基极-发射极短接晶体管的集电极相连,第六基极-发射极短接晶体管的基极接地。第三高阻微带线、第七基极-发射极短接晶体管、第八基极-发射极短接晶体管、第九基极-发射极短接晶体管构成第三非线性传输线单元。其中,第三高阻微带线的一端与第四基极-发射极短接晶体管的集电极相连,另一端与第七基极-发射极短接晶体管的集电极相连,第七基极-发射极短接晶体管的基极与第八基极-发射极短接晶体管的集电极相连,第八基极-发射极短接晶体管的基极与第九基极-发射极短接晶体管的集电极相连,第九基极-发射极短接晶体管的基极接地。以此类推,第四十高阻微带线、第一百一十八基极-发射极短接晶体管、第一百一十九基极-发射极短接晶体管、第一百二十基极-发射极短接晶体管构成第四十非线性传输线单元。其中,第四十高阻微带线的一端与第一百一十五基极-发射极短接晶体管的集电极相连,另一端与第一百一十八基极-发射极短接晶体管的集电极相连,第一百一十八基极-发射极短接晶体管的基极与第一百一十九基极-发射极短接晶体管的集电极相连,第一百一十九基极-发射极短接晶体管的基极与第一百二十基极-发射极短接晶体管的集电极相连,第一百二十基极-发射极短接晶体管的基极接地。

18.所述梳谱发生器的第一百一十八基极-发射极短接晶体管(d118)的集电极作为梳谱发生器的输出端。

19.进一步地,所述非线性传输线梳谱发生器,晶体管基极-发射极短接构成的可变电容具有很强的非线性、电容充放电快,梳谱发生器输出波形更接近矩形脉冲,具有更好的非线性,有利于产生高功率谐波信号;理论上提高非线性传输线单元数量可以有效地提高谐波输出功率,但达到一定数量时非线性传输线的损耗和分布参数影响将会大于它的非线性。所述梳谱发生器,通过合理选择晶体管、非线性传输线单元数量和信号走线方式来使谐波输出功率最大化。

20.下面结合附图对本发明技术方案进一步说明如附图1所示,一种宽带非线性传输线梳谱发生器,包括高阻微带线、基极-发射极短接晶体管构成的强非线性变容二极管。

21.所述非线性传输线梳谱发生器芯片,输入信号经过多级非线性传输线单元后实现波形的高阶压缩,可以得到高次脉冲信号,后可通过高矩形系数的选频网络滤出孤波中所需的脉冲成分。

22.作为一种具体示例,所述梳谱发生器芯片由四十级非线性传输线单元周期级联构成,其中包括第一~第四十高阻微带线tl1~tl40、第一基极-发射极短接晶体管~第一百二十

基极-发射极短接晶体管d1~d120。

23.第一高阻微带线tl1、第一基极-发射极短接晶体管d1、第二基极-发射极短接晶体管d2、第三基极-发射极短接晶体管d3构成第一非线性传输线单元nltl1。其中,第一高阻微带线tl1的一端作为梳谱发生器的输入端,另一端与第一基极-发射极短接晶体管d1的集电极相连,第一基极-发射极短接晶体管d1的基极与第二基极-发射极短接晶体管d2的集电极相连,第二基极-发射极短接晶体管d2的基极与第三基极-发射极短接晶体管d3的集电极相连,第三基极-发射极短接晶体管d3的基极接地。第二高阻微带线tl2、第四基极-发射极短接晶体管d4、第五基极-发射极短接晶体管d5、第六基极-发射极短接晶体管d6构成第二非线性传输线单元nltl2。其中,第二高阻微带线tl2的一端与第一基极-发射极短接晶体管d1的集电极相连,另一端与第四基极-发射极短接晶体管d4的集电极相连,第四基极-发射极短接晶体管d4的基极与第五基极-发射极短接晶体管d5的集电极相连,第五基极-发射极短接晶体管d5的基极与第六基极-发射极短接晶体管d6的集电极相连,第六基极-发射极短接晶体管d6的基极接地。第三高阻微带线tl3、第七基极-发射极短接晶体管d7、第八基极-发射极短接晶体管d8、第九基极-发射极短接晶体管d9构成第三非线性传输线单元nltl3。其中,第三高阻微带线tl3的一端与第四基极-发射极短接晶体管d4的集电极相连,另一端与第七基极-发射极短接晶体管d7的集电极相连,第七基极-发射极短接晶体管d7的基极与第八基极-发射极短接晶体管d8的集电极相连,第八基极-发射极短接晶体管d8的基极与第九基极-发射极短接晶体管d9的集电极相连,第九基极-发射极短接晶体管d9的基极接地。以此类推,第四十高阻微带线tl40、第一百一十八基极-发射极短接晶体管d118、第一百一十九基极-发射极短接晶体管d119、第一百二十基极-发射极短接晶体管d120构成第四十非线性传输线单元nltl40。其中,第四十高阻微带线tl40的一端与第一百一十五基极-发射极短接晶体管d115的集电极相连,另一端与第一百一十八基极-发射极短接晶体管d118的集电极相连,第一百一十八基极-发射极短接晶体管d118的基极与第一百一十九基极-发射极短接晶体管d119的集电极相连,第一百一十九基极-发射极短接晶体管d119的基极与第一百二十基极-发射极短接晶体管d120的集电极相连,第一百二十基极-发射极短接晶体管d120的基极接地。

24.进一步地第一百一十八基极-发射极短接晶体管d118的集电极作为梳谱发生器的输出端。

25.实施例1本实施例宽带非线性传输线梳谱发生器,其电路结构框图如图1所示。

26.如图1所示,本发明一种宽带非线性梳谱发生器芯片由40级非线性传输线单元级联构成,每个非线性单元则是由一段高阻微带线以及三个基极-发射极短接的晶体管组成。为保证非线性传输线具有很强的非线性,三个基极-发射极短接的晶体管可变电容需远远大于微带线的寄生电容,微带线的特征阻抗应大于75ω。

27.本发明选择晶体管基极-发射极短接,其c-v曲线斜率最大,电容充放电越快、梳谱发生器输出波形更接近矩形脉冲,具有更好的非线性,有利于产生高功率的脉冲信号。并且晶体管尺寸越大、谐波输出功率越大,但当输入频率提高时,变容管的寄生参数会变得更加显著,导致谐波输出功率变低。

28.梳谱发生器为进一步提高谐波输出功率与倍频次数,必须使输出波形的上升/下

降沿斜率足够大,通过级联更高的布拉格截止频率传输线实现高阶脉冲压缩。理论上,输入信号经过足够数量的非线性单元后可使输出信号得到理想的矩形波,但实际上当非线性单元数量增加到一定数量后,非线性传输线的损耗和分布参数带来的影响将会大于它的非线性,导致谐波输出功率并不会持续增加,所以选择最佳的非线性单元数量是本发明的关键难点之一。

29.本发明实施例宽带非线性传输线梳谱发生器电路版图如图2所示,版图主要由0.7μm inp hbt晶体管、微带线、地孔、射频端口组成。射频信号从信号输入端口1进入,通过40个非线性传输线单元后,从信号输出端口2输出。

30.图3~图8分别为本发明宽带非线性传输线梳谱发生器的实测频谱曲线与输入、输出信号波形曲线,图3为输入信号频率1ghz、功率23dbm下的谐波输出功率谱线,图4为此工作条件下输入、输出信号波形曲线;图5为输入信号频率5ghz、功率23dbm下的谐波输出功率谱线,图6为此工作条件下输入、输出信号波形曲线;图7为输入信号频率10ghz、功率23dbm下的谐波输出功率谱线,图8为此工作条件下输入、输出信号波形曲线。从时域波形中可以看出,输入正弦信号经过非线性传输线后波形产生了压缩,在频域中可产生丰富的高次谐波分量,此梳谱发生器工作频率范围宽,可覆盖dc-100ghz,1ghz正弦信号注入时、60次谐波输出可达到-36dbm以上,较国内外同类设计实现了更高的倍频次数和谐波输出功率。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。