1.本发明关于一种柱状半导体装置及其制造方法。

背景技术:

2.近年来,已于lsi(large scale integration,大型集成电路)中使用三维结构晶体管(transistor)。其中,属于柱状半导体装置的sgt(surrounding gate transistor,环绕栅极晶体管)作为提供高集积度的半导体装置的半导体元件而受到瞩目。此外,具有sgt的半导体装置的更进一步的高集积化、高性能化也受到要求。

3.在一般的平面(planar)型mos(metal oxide semiconductor,金属氧化物半导体)晶体管中,其通道(channel)朝沿着半导体基板的上表面的水平方向延伸。相对于此,sgt的通道朝相对于半导体基板的上表面为垂直的方向延伸(例如,参照专利文献1、非专利文献1)。因此,相比于平面型mos晶体管,sgt更可达成半导体装置的高密度化。

4.图5为显示n通道sgt的示意结构图。图5的(a)部分为剖面图,图5的(b)部分为俯视图。在具有p型或i型(本征型)导电型的si柱120(以下,将硅半导体柱称为“si柱”)内的上下的位置,形成有当一方成为源极(source)时另一方成为汲极(drain)的n

层121a、121b(以下,将含有高浓度供体(donor)杂质的半导体区域称为“n

层”)。成为此源极、汲极的n

层121a、121b间的si柱120的部分即成为通道区域122。栅极绝缘层123以包围此通道区域122的方式形成。栅极导体层124以包围此栅极绝缘层123的方式形成。sgt由成为源极、汲极的n

层121a、121b、通道区域122、栅极绝缘层123、及栅极导体层124所构成。n

层121b与源极配线金属层s通过开设于n

层121b上的绝缘层125的接触孔c而连接。据此,于俯视观察时,sgt的占有面积相当于平面型mos晶体管的单一源极或汲极n

层的占有面积。因此,具有sgt的电路芯片(chip),相比于具有平面型mos晶体管的电路芯片,能够实现芯片尺寸更进一步的缩小化。

5.另外,当更进一步谋求芯片尺寸的缩小化时,有应要克服的问题。如图5所示,连接源极配线金属层s与n

层121b的接触孔c形成于俯视观察时si柱120的上方。当芯片尺寸进一步缩小化时,si柱120与邻接的si柱的距离即变短。于俯视观察时与接触孔c邻接的接触孔的距离也随之变短。因此,乃要求接触孔形成步骤的微细化与高密度化。

6.图6为显示使用了sgt的sram(静态随机存取内存;static random access memory)单元(cell)电路图。本sram单元电路包含二个反相器(inverter)电路。一个反相器电路由作为负载晶体管的p通道sgt_pc1、及作为驱动晶体管的n通道sgt_nc1所构成。另一个反相器电路由作为负载晶体管的p通道sgt_pc2、及作为驱动晶体管的n通道sgt_nc2所构成。p通道sgt_pc1的栅极与n通道sgt_nc1的栅极相连接。p通道sgt_pc2的汲极与n通道sgt_nc2的汲极相连接。p通道sgt_pc2的栅极与n通道sgt_nc2的栅极相连接。p通道sgt_pc1的汲极与n通道sgt_nc1的汲极相连接。

7.如图6所示,p通道sgt_pc1、pc2的源极连接于电源端子vdd。另外,n通道sgt_nc1、nc2的源极连接于接地(ground)端子vss。选择n通道sgt_sn1、sn2配置于二个反相器电路的

两侧。选择n通道sgt_sn1、sn2的栅极连接于字符(word)线端子wlt。选择n通道sgt_sn1的源极、汲极连接于n通道sgt_nc1、p通道sgt_pc1的汲极与位元(bit)线端子blt。选择n通道sgt_sn2的源极、汲极连接于n通道sgt_nc2、p通道sgt_pc2的汲极与反转位元线端子blrt。如此,具有sram单元的电路由二个负载p通道sgt_pc1、pc2、二个驱动用n通道sgt_nc1、nc2、及二个选择用sn1、sn2所组成的合计共六个sgt所构成(例如,参照专利文献2)。在此sram单元中,二个负载p通道sgt_pc1、pc2的si柱以最接近的方式形成。此时,负载p通道sgt_pc1、pc2的上部p

层上的接触孔形成,在sram单元的高集积化上会变成问题。

8.[现有技术文献]

[0009]

[专利文献]

[0010]

专利文献1:日本特开平2-188966号公报

[0011]

专利文献2:美国专利申请公开第2010/0219483号说明书

[0012]

专利文献3:美国注册us8530960b2号说明书。

[0013]

[非专利文献]

[0014]

非专利文献1:hiroshi takato,kazumasa sunouchi,naoko okabe,akihiro nitayama,katsuhiko hieda,fumio horiguchi,and fujio masuoka:ieee transaction on electron devices,vol.38,no.3,pp.573-578(1991)

[0015]

非专利文献2:c.y.ting,v.j.vivalda,and h.g.schaefer:“study of planarized sputter-deposited sio2”,j.vac.sci.technol.15(3),p.p.1105-1112,may/june(1978)

[0016]

非专利文献3:a.raley,s.thibaut,n.mohanty,k.subhadeep,s.nakamura,etal.:“self-aligned quadruple patterning integration using spacer on spacer pitch splitting at the resist level for sub-32nm pitch applications”proc.of spie vol.9782,2016。

技术实现要素:

[0017]

[发明所欲解决的课题]

[0018]

要求使用sgt的电路的高性能化、高集积化。

[0019]

[用以解决课题的手段]

[0020]

本技术的第一观点的发明为一种柱状半导体装置的制造方法,该柱状半导体装置具有:半导体柱,朝垂直方向立于基板上;栅极绝缘层,包围前述半导体柱;及栅极导体层,包围前述栅极绝缘层;该柱状半导体装置的制造方法具有下列步骤:

[0021]

形成第一半导体柱和第二半导体柱的步骤,该第一半导体柱为前述半导体柱而且在其顶部具有第一材料层,该第二半导体柱邻接于前述第一半导体柱且为前述半导体柱,而且在其顶部具有第二材料层;

[0022]

于比前述栅极导体层上表面更上方,且于前述第一半导体柱和前述第二半导体柱的顶部外周部形成第一层间绝缘层的步骤;

[0023]

形成第三材料层和第四材料层的步骤,该第三材料层位于前述第一层间绝缘层上而且包围前述第一半导体柱的顶部侧面,该第四材料层位于前述第一层间绝缘层上而且包围前述第二半导体柱的顶部侧面;

[0024]

在与前述第三材料层和前述第四材料层的侧面相接的外周部形成第二层间绝缘层的步骤;

[0025]

将前述第一材料层、前述第二材料层、前述第三材料层、和前述第四材料层予以去除而形成第一凹部和第二凹部与步骤的步骤,该第一凹部包围前述第一半导体柱的顶部,该第二凹部包围前述第二半导体柱的顶部;

[0026]

以包围前述第一半导体柱的顶部的方式在前述第一凹部内形成第一杂质层的步骤,与以包围前述第二半导体柱的顶部的方式在前述第二凹部内形成第二杂质层的步骤;

[0027]

于前述第一杂质层上而且在前述第一凹部内形成第一导体层的步骤,与于前述第二杂质层上而且在前述第二凹部内形成第二导体层的步骤;及

[0028]

形成连接前述第一导体层和前述第二导体层的第一配线导体层的步骤;

[0029]

于俯视观察时,在前述第一配线导体层的形成区域,未形成有非为前述第一半导体柱和前述第二半导体柱的其它的前述半导体柱。

[0030]

本发明更具有下列步骤:

[0031]

在前述第一导体层、前述第二导体层、和前述第二层间绝缘层的上方,形成第三层间绝缘层的步骤;

[0032]

在前述第三层间绝缘层,形成俯视观察时与前述第一导体层的一部分区域和前述第二导体层的一部分区域重叠而且相接的第一带状接触孔的步骤;及

[0033]

填埋前述第一带状接触孔以形成前述第一配线导体层的步骤;

[0034]

于俯视观察时,前述第一导体层和前述第二导体层的一部分区域比前述第一带状接触孔更突出于外侧。

[0035]

本发明更具有下列步骤:

[0036]

在形成前述第二层间绝缘层之后,形成俯视观察时与前述第一材料层和前述第三材料层的一部分区域、及前述第二材料层和前述第四材料层的一部分区域重叠而且予以相连接而呈现空隙的第一遮罩材料层的步骤;

[0037]

以前述第一遮罩材料层为遮罩,将前述第一材料层、前述第三材料层、前述第二材料层、前述第四材料层、和前述第二层间绝缘层进行蚀刻以形成第三凹部的步骤;

[0038]

在前述第三凹部内,与前述第一杂质层和前述第二杂质层的形成同时地形成与前述第一杂质层和前述第二杂质层相连接的第三杂质层的步骤;

[0039]

于前述第一杂质层、前述第二杂质层、和前述第三杂质层的上方而且在前述第三凹部内形成第三导体层的步骤;及

[0040]

在前述第三导体层形成与其连接的前述第一配线导体层的步骤;

[0041]

于俯视观察时,前述第一带状接触孔位于前述第三导体层的内侧,而且前述第一杂质层、前述第二杂质层、和前述第三杂质层由相同的半导体材料层所构成。

[0042]

前述第三导体层可设为前述第一配线导体层。

[0043]

前述第一杂质层和前述第二杂质层可通过磊晶结晶成长而形成。

[0044]

本发明更具有下列步骤:

[0045]

在前述第一凹部和前述第二凹部的底部面上形成单结晶半导体薄膜层的步骤;及

[0046]

接着在前述第一凹部和前述第二凹部形成前述第一杂质层和前述第二杂质层的步骤。

[0047]

可设为在前述第一半导体柱和前述第二半导体柱形成有sram(静态随机存取内存;static random access memory)单元电路的负载用sgt(环绕栅极晶体管;surrounding gate transistor)。

[0048]

本技术的第二观点的发明为一种柱状半导体装置,具有:

[0049]

第一半导体柱,朝垂直方向立于基板上;

[0050]

第二半导体柱,邻接于前述第一半导体柱而站立;

[0051]

栅极绝缘层,其上表面位置位于比前述第一半导体柱和前述第二半导体柱的顶部上表面更下方,而且包围前述第一半导体柱和前述第二半导体柱;

[0052]

栅极导体层,包围前述栅极绝缘层;

[0053]

第一层间绝缘层,位于前述栅极导体层上;

[0054]

第一杂质层和第二杂质层,该第一杂质层覆盖前述第一半导体柱顶部,而且于俯视观察时,其外周与前述第一半导体柱的外周等宽地隔开,该第二杂质层覆盖前述第二半导体柱顶部,而且于俯视观察时,与其外周等宽地隔开;

[0055]

第一导体层和第二导体层,该第一导体层位于前述第一杂质层上,该第二导体层位于前述第二杂质层上;

[0056]

第二层间绝缘层,位于前述第一杂质层、前述第二杂质层、前述第一导体层、和前述第二导体层的外周部;

[0057]

第三层间绝缘层,位于前述第一导体层、前述第二导体层、和前述第二层间绝缘层的上方;

[0058]

第一带状接触孔,位于前述第三层间绝缘层,且于俯视观察时,与前述第一导体层的一部分区域和前述第二导体层的一部分区域重叠而且相接;及

[0059]

第一配线导体层,填埋前述第一带状接触孔而成;

[0060]

于俯视观察时,前述第一导体层和前述第二导体层的一部分区域比前述第一带状接触孔更突出于外侧。

[0061]

本发明更具有:

[0062]

第三杂质层,位于与前述第一杂质层和前述第二杂质层相同的表面上,而且与前述第一杂质层和前述第二杂质层相连接;

[0063]

第三导体层,位于前述第一杂质层、第二杂质层、和前述第三杂质层的上方,而且于俯视观察时,与前述第一杂质层、第二杂质层、和前述第三杂质层为相同的形状;及

[0064]

前述第一配线导体层,连接于前述第三导体层;

[0065]

于俯视观察时,前述第一带状接触孔可设为位于前述第三导体层的内侧。

[0066]

前述第三导体层可设为前述第一配线导体层。

[0067]

前述第一杂质层和前述第二杂质层可设为磊晶结晶成长半导体材料层。

[0068]

可设为在前述第一杂质层和前述第二杂质层的侧面及底部具有单结晶半导体薄膜层。

[0069]

可设为在前述第一半导体柱和前述第二半导体柱设有sram(静态随机存取内存;static random access memory)单元电路的负载用sgt(环绕栅极晶体管;surrounding gate transistor)。

附图说明

[0070]

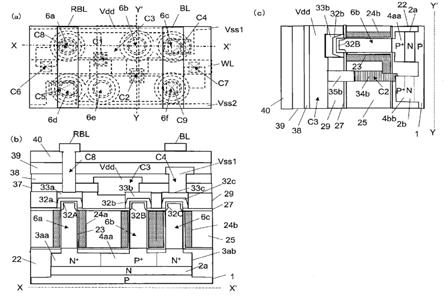

图1a为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0071]

图1b为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0072]

图1c为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0073]

图1d为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0074]

图1e为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0075]

图1f为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0076]

图1g为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0077]

图1h为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0078]

图1i为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0079]

图1j为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0080]

图1k为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0081]

图1l为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0082]

图1m为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0083]

图1n为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0084]

图1o为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0085]

图1p为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0086]

图1q为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0087]

图1r为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0088]

图1s为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0089]

图1t为用以说明第一实施方式的具有sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0090]

图2a为用以说明具有本发明第二实施方式的sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0091]

图2b为用以说明具有本发明第二实施方式的sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0092]

图2c为用以说明具有本发明第二实施方式的sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0093]

图2d为用以说明具有本发明第二实施方式的sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0094]

图2e为用以说明具有本发明第二实施方式的sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0095]

图2f为用以说明具有本发明第二实施方式的sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0096]

图2g为用以说明具有本发明第二实施方式的sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0097]

图3a为用以说明具有本发明第三实施方式的sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0098]

图3b为用以说明具有本发明第三实施方式的sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0099]

图3c为用以说明具有本发明第三实施方式的sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0100]

图4为用以说明具有本发明第三实施方式的sgt的柱状半导体装置的制造方法的俯视图与剖面结构图。

[0101]

图5为显示熟知例的sgt的示意结构图。

[0102]

图6为使用熟知例的sgt的sram单元电路图。

具体实施方式

[0103]

以下参照附图说明本发明的实施方式的柱状半导体装置的制造方法。

[0104]

(第一实施方式)

[0105]

以下参照图1a至图1t来说明本发明的第一实施方式的具有sgt的sram单元电路的制造方法。图的(a)部分为俯视图,图的(b)部分为沿着(a)部分的x-x’线的剖面结构图,图的(c)部分为沿着(a)部分的y-y’线的剖面结构图。

[0106]

如图1a所示,通过磊晶(epitaxial)结晶成长法在p层基板1(权利要求的“基板”的一例)上形成n层2。另外,通过离子注入法在n层2的表层形成n

层3与p

层4a、4b。另外,形成i层6。另外,例如,形成由sio2层、氧化铝(al2o3,以下称为alo)层、sio2层所构成的遮罩材料层7。另外,堆积硅锗(sige)层8。另外,堆积由sio2层所构成的遮罩材料层9。另外,堆积由sin层所构成的遮罩材料层10。另外,i层6也可由包含少量供体或受体(acceptor)杂质原子的n型或p型si所形成。

[0107]

接着,以通过微影(lithography)法所形成的俯视观察时朝y方向延伸的带状阻剂(resist)层(未图示)为遮罩,将遮罩材料层10进行蚀刻。据此,形成于俯视观察时朝y方向延伸的带状遮罩材料层(未图示)。以阻剂层为遮罩,将该带状遮罩材料层进行等向性蚀刻,据此将带状遮罩材料层的宽度,形成为较阻剂层的宽度更窄。据此,即可形成具有较可通过微影法所形成的最小的阻剂层的宽度更小宽度的带状遮罩材料层10a、10b。另外,以带状遮罩材料层10a、10b作为蚀刻遮罩,将遮罩材料层9例如通过rie(reactive ion etching,反应离子蚀刻)进行蚀刻而形成带状遮罩材料层9a、9b。通过等向蚀刻所形成的带状遮罩材料层10a、10b的剖面形成为其底部的宽度较顶部的宽度为大的梯形,相对于此,由于带状遮罩材料层9a、9b的剖面通过rie进行蚀刻,因此形成为矩形。此矩形剖面将会关系到以带状遮罩材料层9a、9b为遮罩的蚀刻图案(etching pattern)的精确度的提升。接着,如图1b所示,以带状遮罩材料层9a、9b为遮罩,将sige层8通过例如rie法进行蚀刻,据此形成带状sige层8a、8b。前述的带状遮罩材料层9a、9b上的带状遮罩材料层10a、10b可在sige层8蚀刻之前去除,或也可使其残存。

[0108]

接着,整体通过ald(atomic layered deposition,原子层堆积)法,以覆盖遮罩材料层7、带状sige层8a、8b、带状遮罩材料层9a、9b的方式形成sin层(未图示)。此时,sin层的剖面在顶部形成圆弧。此圆弧较优选为形成为比带状sige层8a、8b更上部。另外,将整体以例如通过流动化学气相沉积(flow chemical vapor deposition)法所形成的sio2层(未图示)覆盖,然后,通过cmp(chemical mechanical polishing,化学机械研磨)研磨sio2层和sin层以使上表面位置成为带状遮罩材料层9a、9b的上表面位置,而形成sin层13a、13b、13c。另外,将sin层13a、13b、13c的顶部进行蚀刻而形成凹部。此凹部的底部位置形成为位于带状遮罩材料层9a、9b的下部位置。另外,整体覆盖sin层(未图示),且将整体通过cmp法将sin层进行研磨以使上表面位置成为遮罩材料层9a、9b的上表面位置。另外,将通过流动cvd所形成的sio2层予以去除。据此,如图1c所示,在带状遮罩材料层9a、9b的两侧,形成于俯视观察时具有与sin层13a、13b、13c的顶部形状呈相同形状的带状遮罩材料层12aa、12ab、12ba、12bb。

[0109]

接着,如图1d所示,以带状遮罩材料层9a、9b、12aa、12ab、12ba、12bb为遮罩,将sin层13a、13b、13c进行蚀刻,而形成带状sin层13aa、13ab、13ba、13bb。此时,于俯视观察时,带状sin层13aa、13ab、13ba、13bb的宽度将会相同。

[0110]

接着将带状遮罩材料层9a、9b、带状sige层8a、8b予以去除。据此,如图1e所示,在遮罩材料层7上,形成于俯视观察时在各自的顶部上具有朝y方向延伸而且彼此平行排列的带状遮罩材料层12aa、12ab、12ba、12bb的带状sin层13aa、13ab、13ba、13bb。

[0111]

接着,以覆盖整体的方式形成通过流动cvd法所形成的sio2层(未图示)。另外,通过cmp法将sio2层进行研磨以使其上表面位置与带状遮罩材料层12aa、12ab、12ba、12bb的上表面位置相同,且如图1f所示,形成sio2层15。另外,在sio2层15、带状遮罩材料层12aa、12ab、12ba、12bb上形成sin层16。另外,使用与形成带状sin层13aa、13ab、13ba、13bb的方法相同的基本的方法,在sin层16上形成朝x方向延伸而且彼此平行排列的带状遮罩材料层17a、17b。

[0112]

接着,如图1g所示,以带状遮罩材料层17a、17b为遮罩,将sin层16、带状遮罩材料层12aa、12ab、12ba、12bb、带状sin层13aa、13ab、13ba、13bb、遮罩材料层7进行rie蚀刻。另

外,将残存的sin层16、sio2层15予以去除。据此,形成于俯视观察时顶部具有矩形的遮罩材料层19a、19b、19c、19d、19e、19f、19g、19h的sin柱20a、20b、20c、20d、20e、20f、20g、20h。

[0113]

接着,如图1h所示,将矩形的遮罩材料层19b、19g、sin柱20b、20g予以去除。

[0114]

接着,如图1i所示,以遮罩材料层19a、19c、19d、19e、19f、19h和sin柱20a、20c、20d、20e、20f、20h为遮罩将遮罩材料层7进行蚀刻,而形成遮罩材料层7a、7b(权利要求的“第一材料层”的一例)、7c、7d、7e(权利要求的“第二材料层”的一例)、7f。在此蚀刻中,例如进行通过cde(chemical dry etching,化学干蚀刻)法的等向性蚀刻,于俯视观察时,使遮罩材料层7a、7b、7c、7d、7e、7f的形状为圆形。此cde蚀刻当在此步骤之前遮罩材料层7a、7b、7c、7d、7e、7f的俯视观察形状已为圆形时则不需要。另外,将遮罩材料层19a、19c、19d、19e、19f、19h和sin柱20a、20c、20d、20e、20f、20h予以去除。另外,以遮罩材料层7a、7b、7c、7d、7e、7f为遮罩将i层6进行蚀刻,在n

层3、p

层4a、4b上形成si柱6a、6b(权利要求的“第一半导体柱”的一例)、6c、6d、6e(权利要求的“第二半导体柱”的一例)、6f。

[0115]

接着,如图1j所示,将相连于si柱6a、6b、6c的底部的n

层3、p

层4a、n层2、p层基板1进行蚀刻,而形成由p层基板1的上部、n层2a、n

层3aa、3ab、p

层4aa所构成的si柱台21a。同时,将相连于si柱6d、6e、6f的底部的n

层3、p

层4b、n层2、p层基板1进行蚀刻,而形成由p层基板1的上部、n层2b、n

层3ba(未图示)、3bb(未图示)、p

层4bb所构成的si柱台21b。另外,在n

层3aa、3ab、3ba、3bb、p

层4aa、4bb、n层2a、2b的外周部、和p层基板1上形成sio2层22。另外,通过ald法,以覆盖整体的方式形成hfo2层23(权利要求的“栅极绝缘层”的一例)、tin层(未图示)。此时,在si柱6b、6c间和si柱6d、6e间,tin层以侧面彼此接触。另外,在包围si柱6a的外周而成的hfo2层23上形成tin层24a、以包围si柱6b、6c的外周的hfo2层23的方式形成tin层24b(权利要求的“栅极导体层”的一例)、以包围si柱6d、6e的外周的hfo2层23的方式形成tin层24c(权利要求的“栅极导体层”的一例)、以包围si柱6f的外周的hfo2层23的方式形成tin层24d。另外,整体覆盖sio2层(未图示),之后,通过cmp法将整体进行研磨以使其上表面位置成为遮罩材料层7a、7b、7c、7d、7e、7f的上表面位置。另外,将经由rie法平坦化后的sio2层(未图示)进行蚀刻,而形成sio2层25。另外,以遮罩材料层7a、7b、7c、7d、7e、7f、sio2层25为遮罩,而将hfo2层23、tin层24a、24b、24c、24d的顶部去除。tin层24a、24b、24c、24d成为sgt的栅极导体层。此栅极导体层为有助于sgt的临限值电压的设定的层,可由单层或多层所组成的栅极导体层所形成。此栅极导体材料层与si柱6b、6c间、及si柱6d、6e间的侧面整体邻接地形成。另外,也可相连于tin层24a、24b、24c、24d而形成例如钨(w)层,且使用此w层作为栅极导体层。此w层也可为其它导体材料层。

[0116]

接着,如图1k所示,在si柱6a至6f的外周部的sio2层25上,形成sin层27(权利要求的“第一层间绝缘层”的一例)。另外,整体覆盖sio2层(未图示)。另外,通过rie法将该sio2层进行蚀刻,据此在露出的si柱6a至6f的顶部和遮罩材料层7a至7f的侧面,形成于俯视观察时等宽的sio2层28a、28b(权利要求的“第三材料层”的一例)、28c、28d、28e(权利要求的“第四材料层”的一例)、28f。此时,sio2层28b与sio2层28c为分开地形成。同样地,sio2层28d与sio2层28e为分开地形成。另外,sin层27至少形成于属于栅极导体层的tin层24a、24b、24c、24d上即可。

[0117]

接着,整体覆盖氧化铝(alo)层(未图示)。另外,如图1l所示,通过cmp法进行研磨以使alo层的上表面位置成为遮罩材料层7a至7f的上表面位置,而形成alo层29(权利要求

的“第二层间绝缘层”的一例)。另外,将包围si柱6a至6f的顶部的sio2层28a、28b、28c、28d、28e、28f予以去除,而形成包围si柱6a至6f的顶部的凹部30a、30b、30c、30d、30e、30f。由于sio2层28a、28b、28c、28d、28e、28f为相对于si柱6a至6f的顶部自行对准地形成,因此凹部30a、30b、30c、30d、30e、30f为相对于si柱6a至6f自行对准地形成。

[0118]

接着,如图1m所示,将遮罩材料层7a、7b、7c、7d、7e、7f予以去除,而在si柱6a至6f的顶部外周与上部,形成凹部30a、30b(权利要求的“第一凹部”的一例)、30c、30d、30e(权利要求的“第二凹部”的一例)、30f。

[0119]

接着,通过cvd法于整体覆盖sio2层(未图示)。另外,如图1n所示,通过cmp法将sio2层的上表面位置研磨至alo层29的上表面位置,并以覆盖si柱6a至6f的顶部的方式在凹部30a、30b、30c、30d、30e、30f内形成sio2层31a、31b(未图示)、31c、31d、31e(未图示)、31f。另外,通过微影法和化学蚀刻法将sio2层31b、31e予以去除。另外,通过选择磊晶结晶成长法将含有受体杂质的p

层32b(权利要求的“第一杂质层”的一例)、32e(权利要求的“第二杂质层”的一例)以覆盖si柱6b、6e的顶部的方式形成于凹部30b、30e内。p

层32b、32e的外周形成为于俯视观察时不会较凹部30b、30e的外周更外侧。另外,较优选为在形成p

层32b、32e之前,于将si柱6b、6e的顶部略为氧化之后,进行去除此氧化膜的处理,且进行si柱6b、6e的顶部表层的损伤(damage)层的去除及清洗。另外,p

层层32b、32e也可使用选择磊晶结晶成长法以外的例如分子线结晶成长法等其它方法而形成属于单结晶的p

层层32b、32e。此外,p

层层32b、32e也可于整面地覆盖含有受体杂质的半导体层之后,通过cmp法进行研磨以使其上表面位置到达alo层29的上表面位置之后,将上表面通过cde法或进行化学蚀刻来形成。

[0120]

接着,于整体覆盖sio2层(未图示),且通过cmp法进行研磨以使sio2层的上表面位置与alo层29的上表面位置相同,而使sio2层(未图示)覆盖于p

层32b、32e上。另外,通过微影法和化学蚀刻,将sio2层31a、31c、31d、31f予以去除。另外,如图1o所示,通过选择磊晶结晶成长法将含有供体杂质的n

层32a、32c、32d、32f,以覆盖si柱6a、6c、6d、6f的顶部的方式形成于凹部30a、30c、30d、30f内。n

层32a、32c、32d、32f的外周形成为于俯视观察时不会较凹部30a、30c、30d、30f的外周更外侧。另外,将p

层32b、32e上的sio2层予以去除。

[0121]

接着,于整体覆盖薄的ta层(未图示)与w层(未图示)。另外,如图1p所示,通过cmp法进行研磨以使w层的上表面位置成为alo层29的上表面位置,而形成于侧面与底部具有ta层的w层33a、33b(权利要求的“第一导体层”的一例)、33c、33d、33e(权利要求的“第二导体层”的一例)、33f。此时,位于n

层32a、32c、32d、32f、p

层32b、32e、与w层33a、33b、33c、33d、33e、33f之间的ta层,为用以减小此二层的接触电阻的缓冲层。此缓冲层也可为单层或多层的其它材料层。

[0122]

接着,如图1q所示,在tin层24c、n

层3aa、和p

层4aa的上方形成接触孔c1。同时,在tin层24b、n

层3bb、和p

层4bb的上方形成接触孔c2。另外,于整体覆盖薄的缓冲ti层(未图示)与w层(未图示)。另外,进行通过rie的回蚀(etch back)以使w层的上表面位置成为比接触孔c1、c2的上表面位置更下方,而于接触孔c1、c2内形成w层34a(未图示)、34b。另外,于整体覆盖sin层(未图示)。另外,使用cmp法将sin层进行研磨以使上表面位置成为w层33a、33b、33c、33d、33f的上表面位置,而于接触孔c1内的w层34a上方和接触孔c2内的w层34b上方形成sin层35a(未图示)、35b。

[0123]

接着,于整体覆盖sio2层(未图示)。另外,如图1r所示,于整体形成sio2层37(权利要求的“第三层间绝缘层”的一例)之后,使用微影法、rie法,形成俯视观察时与si柱6b、6e上的w层33b、33e的至少一部分重叠且朝y方向延伸的带状接触孔c3(权利要求的“第一带状接触孔”的一例)。另外,带状接触孔c3的底部也可到达sin层27的上表面。

[0124]

接着,如图1s所示,填埋带状接触c3,形成连接w层33b和33e的电源配线金属层vdd(权利要求的“第一配线导体层”的一例)。另外,电源配线金属层vdd不仅可为金属,也可使用单层或多层由合金、较多地含有受体或供体杂质的半导体所构成的材料层来形成。

[0125]

接着,如图1t所示,以覆盖整体的方式形成上表面平坦的sio2层38。另外,通过形成于n

层32c上的w层33c上的接触孔c4而形成接地配线金属层vss1。同时,通过形成于n

层32d上的w层33d上的接触孔c5而形成接地配线金属层vss2。以覆盖整体的方式形成上表面平坦的sio2层39。另外,通过形成于tin层24a、24d上的接触孔c6、c7而形成字符配线金属层wl。另外,以覆盖整体的方式形成上表面平坦的sio2层40。另外,通过形成于n

层32a、32f上的w层33a、33f的接触孔c8、c9而形成反转位元输出配线金属层rbl、位元输出配线金属层bl。据此,在p层基板1上形成sram单元电路。在本sram单元电路中,于si柱6b、6e形成有负载sgt,于si柱6c、6d形成有驱动sgt,且于si柱6a、6f形成有选择sgt。

[0126]

另外,通过图1n、图1o所示的形成n

层32a、32c、32d、32f、p

层32b、32e后的热步骤,以供体或受体杂质从n

层32a、32c、32d、32f、p

层32b、32e扩散至si柱6a至6f的顶部的方式,形成n

层32a、32c、32d、32f(未图示)、p

层32b、32e(未图示)。n

层32a、32c、32d、32f、p

层32b、32e的分布形状依据热步骤的纪录及si柱6a至6f的直径而形成于si柱6a至6f的顶部表层或顶部内部整体。据此,n

层32a、32c、32d、32f、p

层32b、32e、n

层32a、32c、32d、32f、p

层32b、32e以连接于si柱6a至6f的顶部的方式形成。另外,n

层32a、32c、32d、32f、p

层32b、32e的垂直方向的下端的位置,只要可进行正常的sgt动作,无论与栅极tin层24a、24b、24c、24d的上端位置相同、或是分开、或是重叠均可。

[0127]

此外,在图1j的状态中,也可无遮罩材料层7a、7b、7c、7d、7e、7f。此时,在图1k或图1l中,通过将si柱6a至6f的顶部进行蚀刻、或在将si柱6a至6f的顶部进行氧化之后予以去除的步骤等,可使si柱6a至6f顶部的上表面位置比alo层29更低。

[0128]

另外,在图1r所示的带状接触孔c3的形成中,需要下列条件。

[0129]

(条件一)

[0130]

于俯视观察时,在带状接触孔c3的区域内无负载sgt以外的si柱(在本实施方式中对应6a、6c、6d、6f)。

[0131]

(条件二)

[0132]

于俯视观察时,带状接触孔c3可形成为与在y方向上邻接的其它sram单元相连,也可形成为与其分离。然而,于俯视观察时,形成负载sgt的si柱(本实施方式中对应si柱6b、6c)间必须在x方向、y方向的两方向上相连。

[0133]

(条件三)

[0134]

带状接触孔c3是为了连接杂质区域(在本实施方式中对应p

层32b、32e)和金属、合金等配线导电层而形成,该杂质区域形成为连接于si柱的顶部的sgt的源极或汲极。

[0135]

依据第一实施方式的制造方法,可获得下列特征。

[0136]

(特征一)

[0137]

在本实施方式中,p

层32b、32e形成于与si柱6b、6e自行对准地形成的凹部30b、30e内。另外,同样地p

层32b、32e上的w层33b、33e也形成于凹部30b、30e内。据此,w层33b、33e为与同样地形成的邻接的n

层32c、33d、w层33c、33d确实地分离。而且,由于p

层32b、32e为覆盖si柱6b、6e的顶部而形成,因此相比于仅在si柱6b、6e的顶部形成杂质层而形成sgt的源极或汲极,可将源极或汲极电阻减小。另外,由于w层33b、33e相接于p

层32b、32e的上表面整体,因此属于配线导体层的电源配线金属层vdd为与邻接的w层33c、33d分离地与w层33b、33e的一部分区域连接即可。此点显示可将用以连接属于配线导体层的电源配线金属层vdd与w层33b、33e的接触孔c3,以离开w层33c、33d的方式形成。据此,形成使用了高密度而且具有低的源极或汲极电阻的sgt的sram单元电路。另外,形成于si柱6b、6c的二个sgt形成了cmos(complementary metal oxide semiconductor,互补性金属氧化半导体)反相器电路,同样地形成于si柱6d、6e的二个sgt形成了cmos反相器电路。此点显示了可将本实施方式应用于其它逻辑电路。据此,本实施方式有助于使用sgt的高密度而且高性能的电路形成。

[0138]

(特征二)

[0139]

以往,在形成有负载sgt的si柱6b、6e上各自形成独立的接触孔。此二个接触孔的距离,相比于其它驱动sgt、选择sgt于接触孔的距离为最近。此时,当sram单元更进一步高集积化时,即难以将此二个独立的接触孔通过一次的微影法、rie蚀刻法来形成。因此,将会产生例如要分成二次进行微影法、rie蚀刻法的步骤的必要性。此时,除了伴随着步骤数增加导致成本增加的问题外,还会有为了要加入二次微影步骤间的遮罩对位裕度所引起的集积度降低的问题。此外,为了精确度良好地形成独立的微细的邻接的二个接触孔,会产生制造上困难的问题。针对此点,在本实施方式中,于俯视观察时,与形成有负载sgt的二个si柱6b、6e上的p

层32b、32e、w层33b、33e重叠地形成带状接触孔c3。据此,通过带状接触孔c3而连接电源配线金属层vdd和p

层32b、32e。如此,在本实施方式中,不会在si柱6b、6e上形成独立的接触孔。据此,即可达成通过一次微影法、rie蚀刻法形成接触孔而降低成本、及不会因为有遮罩对位裕度的问题而降低集积度。另外,由于带状接触孔c3相比于熟知的形成二个独立的接触孔的方法可形成为更宽广,因此具有使图案精确度更为良好的优点。据此,依据本实施方式,可用底成本形成使用高集积度、高性能的sgt的sram单元电路。同样地,可形成使用高集积度、高性能的sgt的逻辑电路。

[0140]

(第二实施方式)

[0141]

以下参照图2a至图2c来说明本发明的第二实施方式的具有sgt的sram单元电路的制造方法。图的(a)部分为俯视图,图的(b)部分为沿着(a)部分的x-x’线的剖面结构图,图的(c)部分为沿着(a)部分的y-y’线的剖面结构图。

[0142]

在本实施方式中,首先进行第一实施方式中所说明的图1a至图1q的步骤。另外,于整体覆盖阻剂层(未图示)。另外,如图2a所示,使用微影法,在sin层41、遮罩材料层7a至7f、sio2层28a至28f的上方,形成俯视观察时与si柱6b、6e重叠而且呈带状空隙的阻剂层42(权利要求的“第一遮罩材料层”的一例)。

[0143]

接着,如图2b所示,以阻剂层42为遮罩,通过rie法将sin层41、遮罩材料层7b、7e、sio2层28a、28e进行蚀刻以使其上表面位置成为比si柱6b、6e的顶部上表面位置更下方,而形成凹部43。另外,此凹部43的底部也可到达sin层27。

[0144]

接着,将阻剂层42去除。另外,如图2c所示,将si柱6b、6e上的遮罩材料层7b、7e、和sio2层28b、28e予以去除,而形成凹部43a(权利要求的“第三凹部”的一例)。凹部43a由朝y方向延伸的矩形部、和包围si柱6b、6e的顶部的所去除的sio2层28b、28e部分所构成。

[0145]

接着,于整体覆盖通过ald法所形成的薄的单结晶si层(未图示)、和通过磊晶结晶成长法所形成的含有受体杂质的p

层(未图示)。另外,将p

层、薄的si层进行研磨以使其上表面位置成为sin层41的上表面位置,且如图2d所示,形成薄的单结晶si层45b(权利要求的“单结晶半导体薄膜层”的一例)、p

层46。

[0146]

接着,如图2e所示,将薄的si层45、p

层46的上部进行蚀刻而形成p

层46b。另外,使用cvd法与cmp法,形成位于p

层46b的上部而且其上表面位置位于sin层41的上表面位置的遮罩材料层49b。另外,将位于si柱6a、6c、6d、6f的顶部的外周部与上方的遮罩材料层7a、7c、7d、7f、sio2层28a、28c、28d、28f予以去除,而于si柱6a、6c、6d、6f的顶部上形成凹部43a、43c、43d、43e。另外,p

层46b由第一实施方式的图1n所示的与p

层32b(权利要求的“第一杂质层”的一例)和p

层32e(权利要求的“第二杂质层”的一例)相连接的杂质层(权利要求的“第三杂质层”的一例)所构成。此外,如第一实施方式所示,p

层46b也可通过选择磊晶结晶成长法而形成。此外,也可使用例如分子线结晶成长法等其它方法来形成属于单结晶的p

层46b。

[0147]

接着,如图2f所示,使用与形成p

层46b的方法相同的方法,在凹部43a、43c、43d、43e内,形成薄的单结晶si层45a、45c(未图示)、45d、45e(未图示)、和含有供体杂质的n

层46a、46c、46d(未图示)、46e(未图示)。另外,在n

层46a、46c、46d、46e上,形成其上表面位置成为与sin层41的上表面位置相同的遮罩材料层49a、49c、49d、49e。

[0148]

接着,将遮罩材料层49a、49b、49c、49d、49e予以去除。另外,如图2g所示,使用cvd法、cmp法,在n

层46a、46c、46d、46e、p

层46b上形成w层50a、50b(权利要求的“第三导体层”的一例)、50c、50e。另外,于整体形成sio2层52。另外,使用微影法和rie蚀刻法,形成去除w层50b上的sio2层52后的带状接触孔c10。另外,通过带状接触孔50b,形成与w层50b相连接的带状电源配线金属层vdd。另外,通过进行图1t所示的步骤,在p层基板1上形成sram单元电路。另外,w层50a、50b、50c、50e也可由单层或多层其它金属或合金所构成的导体层来形成。

[0149]

另外,由于薄的单结晶si层45a至45e为用以形成结晶性良好的p

层46b、n

层48a、48b、48c、48d的层,因此若符合此目的,也可为其它单结晶半导体薄膜层。

[0150]

另外,也可在薄的单结晶si层45a至45e的下方的si柱6a、6c、6d、6f的顶部不形成含有供体杂质原子的杂质层,在si柱6b、6e的顶部不形成含有受体杂质原子的杂质层。此杂质层也可在形成薄的单结晶si层45a至45e之后,通过从p

层46b、n

层46a、46c、46e进行受体杂质原子及供体杂质原子的热扩散来形成。此外,此杂质层也可在形成薄的单结晶si层45a至45e之前,使si柱6a至6f的顶部含有受体杂质原子及供体杂质原子,而形成p

层46b、n

层46a、46c、46e。

[0151]

依据第二实施方式的制造方法,可获得下列特征。

[0152]

(特征一)

[0153]

在第一实施方式中,p

层32b、32e通过选择磊晶结晶成长法,形成于si柱6b、6e的顶部外周部的凹部30b、30e之中。与si柱6b、6e的顶部相接的p

层32b、32e,被要求要具有良

好的结晶性。当此结晶性不良好时,会产生p

层32b、32e所形成的二极管的电阻变大、或泄漏电流变大、或接合耐压降低等问题。若欲使此结晶性变良好,较优选为增宽要使其结晶成长的凹部32b、32e的俯视观察时的面积。然而,由于凹部32b、32e的面积会因为sram单元的高密度化而变小,因此难以形成具有良好结晶性的p

层32b、32e。相对于此,在本实施方式中,由于要使磊晶结晶成长的凹部43a的面积比第一实施方式的凹部32b、32e更大,因此可形成结晶性良好的p

层46。据此,可谋求二极管电阻、泄漏电流的降低、及高耐压化。另外,可在形成单结晶薄膜si层45之后,通过使p

层46磊晶结晶成长而形成结晶性更良好的p

层46。

[0154]

(特征二)

[0155]

在本实施方式中,p

层46b、n

层46a、46c、46d、46e为相对于si柱6a至6f的顶部,包含有自行对准地围成同心圆状的杂质区域。据此,可将邻接的si柱6b、6c、与同样邻接的si柱6d、6e的二个si柱间的距离缩短。据此,可谋求sram单元的高密度化。同样地,位于p

层46b、n

层46a、46c、46d、46e上的w层50a至50e形成于通过自行对准而形成的凹部43a至43e内。据此,可使用以连接w层50b上和电源配线金属层vdd的接触孔c10,从邻接的si柱6a、6c、6d、6f上的w层50a、50c、50d、50e离开。据此,可谋求sram单元的高密度化。

[0156]

(第三实施方式)

[0157]

以下参照图3a至图3c说明本发明的第三实施方式的具有sgt的sram单元电路的制造方法。图的(a)部分为俯视图,图的(b)部分为沿着(a)部分的x-x’线的剖面结构图,图的(c)部分为沿着(a)部分的y-y’线的剖面结构图。

[0158]

如图3a所示,在p层基板1上,形成由n层2a、n

层3aa、3ab、p

层4aa所构成的si柱台55a、和由n层2b、n

层3ba(未图示)、3bb(未图示)、p

层4ba所构成的si柱台55b。另外,在si柱台55a、55b上,形成si柱6a、6b、6c、6d、6e、6f。连结si柱6b、6e的中心的直线为沿着y方向。同样地,连结si柱6a、6d的直线、和连结si柱6c、6f的中心的直线也沿着y方向。另外,在si柱6a至6f的底部外周部形成sio2层22a。另外,以覆盖整体的方式通过ald法形成栅极hfo2层23a。另外,以围着包围si柱6a的栅极hfo2层23a的方式形成栅极tin层24a。同时,以围着包围si柱6b、6c的hfo2层23a的方式形成tin层24b。同时,以围着包围si柱6d、6e的hfo2层23a的方式形成栅极tin层24c。同时,以围着包围si柱6f的hfo2层23a的方式形成tin层24d(未图示)。另外,以围着栅极tin层24a、24b、24c、24d的方式形成sio2层25a。另外,通过形成于sio2层25a的接触孔ca,形成连接tin层24c和n

层3aa、p

层4aa而且上表面位置比tin层24a至24d上表面位置更低的w层26a。同时,通过形成于sio2层25a的接触孔cb,形成连接tin层24b和n

层3bb、p

层4ba而且上表面位置比tin层24a至24d上表面位置更低的w层26b。另外,在si柱6a至6f的顶部的外周部,且于栅极tin层24a至24d的上端上形成sin层27a。另外,在si柱6a、6c、6d、6f的顶部形成n

层46a、46c、46d(未图示)、46f(未图示)、在si柱6b、6e的顶部形成p

层46b、46e。另外,通过与第一实施方式的图1k至图1p所示的步骤相同的步骤,以选择磊晶结晶成长法形成n

层47a、47c、47d(未图示)、47f(未图示)、p

层47b、47e,另外,在n

层47a、47c、47d、47f、p

层47b、47e的上方形成w层48a、48b、48c、48d(未图示)、48e、48f(未图示)。另外,在n

层47a、47c、47d、47f、p

层47b、47e、w层48a、48b、48c、48d、48e、48f的外周部形成sio2层49。

[0159]

接着,如图3b所示,在w层48a、48b、48c、48d、48e、48f、sio2层49的上方形成sio2层

50。另外,通过微影法和rie蚀刻,形成底部位置位于p

层47b、47e的上面表位置而且俯视观察时与w层48b、48e重叠而朝y方向延伸的带状接触孔cc。在俯视观察时的x-x'线上,带状接触孔cc位于w层48b的内侧。另外,带状接触孔cc与w层48e的关系也复相同。另外,以填埋接触孔cc的方式形成与p

层47b、47e连接的电源配线金属层vdd。此时,通过cmp,使sio2层50、与电源配线金属层vdd的上表面位置相同。据此,于俯视观察时,电源配线金属层vdd不会比带状接触孔cc更突出于外侧。

[0160]

接着,如图3c所示,以覆盖整体的方式形成上表面平坦的sio2层51。另外,通过形成于w层48a上的接触孔cd形成接地配线金属层vss1。同时,通过形成于w层48f上的接触孔ce形成接地配线金属层vss2。另外,以覆盖整体的方式形成上表面平坦的sio2层52。另外,通过形成于tin层24a、24d上的接触孔cf、cg形成字符配线金属层wl。另外,以覆盖整体的方式形成上表面平坦的sio2层53。另外,通过形成于w层48c、48d上的接触孔ch、ci形成位元输出配线金属层bl、反转位元输出配线金属层rbl。据此,在p层基板1上形成sram单元电路。

[0161]

依据第三实施方式的制造方法,可获得下列特征。

[0162]

(特征一)

[0163]

在第一实施方式中,si柱6b、6e在x方向上错开地形成。相对于此,在本实施方式中,si柱6b、6e的中心位于朝y方向延伸的一条线上。如此,在本实施方式中的si柱6a至6f于sram单元内的配置,虽与第一实施方式中的si柱6a至6f的配置不同,但本实施方式具有与第一实施方式相同的特征。p

层47b、47e、和w层48b、48e为与si柱6b、6e自行对准地形成。据此,p

层47b、47e、和w层48b、48e,即可与形成于邻接的si柱6c、6d顶部的n

层47c、47d、w层48c、48d确实地分离。而且,由于p

层47b、47e覆盖着p

层46b、46e,因此形成低电阻源极或汲极区域。

[0164]

(特征二)

[0165]

在本实施方式中,带状接触孔cc在x-x'线上位于w层48b的内侧。带状接触孔cc与w层48e的关系也复相同。而且,由于带状接触孔cc为于俯视观察时连接于w层48b、48e的一部分即可,因此可防止因为遮罩对位偏移所引起的合格率降低。另外,由于带状接触孔cc相比于在w层48b、48e上形成二个独立的接触孔的方法可形成为更宽广,因此具有可使图案精确度良好的优点。据此,可以低成本形成使用高集积度、高精确度的sgt的sram单元。

[0166]

(第四实施方式)

[0167]

以下参照图4来说明本发明的第四实施方式的具有sgt的sram单元电路的制造方法。图4的(a)部分为俯视图,图4的(b)部分为沿着图4的(a)部分的x-x’线的剖面结构图,图4的(c)部分为沿着图4的(a)部分的y-y’线的剖面结构图。

[0168]

如图4所示,不形成图2g所示的接触孔c10、电源配线金属层vdd。w层50b成为电源配线金属层vdd。

[0169]

依据第四实施方式的制造方法,可获得下列特征。

[0170]

在本实施方式中,由于w层50b成为电源配线金属层vdd,因此不需要第二实施方式的图2g所示在sram单元区域形成接触孔c10、电源配线金属层vdd的步骤。据此,即可防止伴随着sram单元内的接触孔、和配线金属层的形成所导致的集积度的降低、合格率的降低。此外,当将本发明应用于逻辑电路时,可将单位电路区域至外部的配线取出端子的距离缩短,因此可使对应于前述的w层50b的导体层形成更为容易。此外,在微处理器电路中,也可将本

实施方式仅应用于逻辑电路区域。

[0171]

(其它实施方式)

[0172]

另外,在本发明的实施方式中,虽于一个半导体柱形成一个sgt,但本发明也可适用于形成二个以上的电路形成上。本发明可应用于形成有二个以上sgt的二个半导体柱的最上部的sgt的顶部杂质层间的连接上。

[0173]

另外,在第一实施方式中,虽形成了si柱6a至6f,但也可为由其它半导体材料所构成的半导体柱。此点在本发明的其它实施方式中也复相同。

[0174]

此外,第一实施方式中的n

层32a、32c、32d、32f、p

层32b、32e,也可由含有供体或受体杂质的si、或其它半导体材料层所形成。此外,n

层32a、32c、32d、32f、p

层32b、32e也可由不同的半导体材料层所形成。此点在本发明的其它实施方式中也复相同。

[0175]

此外,在第一实施方式中,n

层32a、32c、32d、32f、p

层32b、32e使用选择磊晶结晶成长法而形成。也可通过其它方法而选择性地形成n

层32a、32c、32d、32f、p

层32b、32e,包含重复cde(chemical dry etching)与一般的磊晶结晶成长法而于凹部30a至30f内的si柱6a至6f的顶部上形成n

层32a、32c、32d、32f、p

层32b、32e的方法。此点在本发明的其它实施方式中也复相同。

[0176]

此外,第一实施方式中的si柱6a至6f的外周部的sin层27、露出的si柱6a至6f的顶部、遮罩材料层7a至7f的侧面上所形成的sio2层28a至28f、及包围sio2层28a至28f的alo层29,若为符合本发明目的的材料,则也可使用由单层或多层所构成的含有有机材料或无机材料的其它材料层。此点在本发明的其它实施方式中也复相同。

[0177]

此外,在第一实施方式中,遮罩材料层7由sio2层、氧化铝(al2o3,也称为alo)层、sio2层所形成。遮罩材料层7若为符合本发明目的的材料,则也可使用由单层或多层所构成的含有有机材料或无机材料的其它材料层。此点在本发明的其它实施方式中也复相同。

[0178]

此外,在第一实施方式中,如图1c、图1d所示,将通过ald法所形成的带状sin层13aa、13ab、13ba、13bb于整体形成于带状sige层8a、8b的两侧。带状sin层13aa、13ab、13ba、13bb、和带状sige层8a、8b,若为符合本发明目的的材料,则也可使用由单层或多层所构成的含有有机材料或无机材料的其它材料层。此点在本发明的其它实施方式中也复相同。

[0179]

此外,如图1a至图1g所述,通过与形成带状sin材料层13aa、13ab、13ba、13bb的方法相同的方法,形成与朝y方向延伸的带状遮罩材料层12a、12ab、12ba、12bb、带状sin层13aa、13ab、13ba、13bb正交而朝x方向延伸的带状遮罩材料层17a、17b。据此,x方向、y方向上均以高精确度而且高密度地形成si柱6a至6f。另外,在本实施方式的说明中,于形成带状遮罩材料层12a、12ab、12ba、12bb、带状sin层13aa、13ab、13ba、13bb之后,形成了带状遮罩材料层17a、17b。相对于此,在形成了带状遮罩材料层17a、17b之后,于形成带状sin材料层12a、12ab、12ba、12bb、带状sin层13aa、13ab、13ba、13bb的步骤中,也可同样以高精确度且高密度地形成si柱6a至6f。此外,在设计中,当y方向上有余裕时,也可不使用本方法而通过微影法和rie蚀刻法直接地形成带状遮罩材料层17a、17b。此外,当x方向上有余裕时,也可不使用本方法而通过微影法和rie蚀刻法直接地形成带状遮罩材料层13aa、13ab、13ba、13bb。此外,若可满足sram单元性能,也可使用sadp(self-aligned double patterning(自对准双重图案法),例如参照非专利文献3)、saqp(self-aligned quadruple patterning(自对准四重图案法),例如参照非专利文献3)来形成朝x方向延伸的带状遮罩材料层12a、

12ab、12ba、12bb、带状sin层17a、17b。此点在本发明的其它实施方式中也复相同。

[0180]

此外,在第一实施方式中,如图1h、图1i所说明,在形成顶部具有矩形的遮罩材料层19a、19b、19c、19d、19e、19f、19g、19h的sin柱20a、20b、20c、20d、20e、20f、20g、20h之后,将矩形的遮罩材料层19b、19g、sin柱20b、20g予以去除。据此,形成俯视观察时于图1所示的具有接触孔c1、c2的区域不具有si柱的接触孔c1、c2形成区域。相对于此,也可在形成si柱于接触孔c1、c2形成区域之后,将这些si柱予以去除,而形成接触孔c1、c2形成区域。此外,也可通过在形成带状遮罩材料层17a、17b之后,进行将接触孔c1、c2形成区域的带状遮罩材料层17a、17b予以去除的步骤,而不在具有接触孔c1、c2的区域形成si柱的方法,形成接触孔c1、c2形成区域。综上所述,也可通过第一实施方式所说明的方法以外的方法作成接触孔c1、c2形成区域。此点在本发明的其它实施方式中也复相同。

[0181]

此外,如图1t所示,在第一实施方式中,于si柱6a至6f的下部,在n层2a、2b上相连接地形成有成为sgt的源极或汲极的n

层3aa、3ab、3ba、3bb、p

层4aa、4bb。相对于此,也可将n

层3aa、3ab、3ba、3bb、p

层4aa、4bb形成于si柱6a至6f的底部,而且通过金属层、合金层来连接n

层3aa、3ab、3ba、3bb、p

层4aa、4bb间。此外,n

层3aa、3ab、3ba、3bb、p

层4aa、4bb也可以连接于si柱6a至6f的底部侧面的方式形成。综上所述,成为sgt的源极或汲极的n

层3aa、3ab、3ba、3bb、p

层4aa、4bb,也可以相接于si柱6a至6f的底部的内部或侧面外侧的方式形成于其外周,另外,也可分别以其它导体材料来电性连接。此点在本发明的其它实施方式中也复相同。

[0182]

此外,在第一实施方式中,虽将带状遮罩材料层9a、9b、12aa、12ab、12ba、12bb的各自的上表面、和底部的垂直方向上的位置形成为相同,但若符合本发明目的,则各自的上表面、和底部的位置也可在垂直方向上不同。此点在本发明的其它实施方式中也复相同。此点在本发明的其它实施方式中也复相同。

[0183]

此外,在第一实施方式中,带状遮罩材料层9a、9b、12aa、12ab、12ba、12bb的厚度及形状,因为cmp所进行的研磨、及rie蚀刻、清洗而变化。此变化若为符合本发明目的的程度内,则无问题。此点在本发明的其它实施方式中也复相同。

[0184]

此外,第一实施方式中的各种配线金属层34a、34b、wl、vdd、vss、bl、rbl的材料不仅为金属,也可为合金、较多地含有受体或供体杂质的半导体层等导电材料层,另外,也可将这些组合单层或多层来构成。此点在本发明的其它实施方式中也复相同。

[0185]

此外,在第一实施方式中,如图1j所示,使用了tin层24a、24b、24c、24d作为栅极金属层。此tin层24a、24b、24c、24d若为符合本发明目的的材料,则可使用由单层或多层所构成的材料层。tin层24a、24b、24c、24d可由至少具有所希望的工作函数的单层或多层金属层等导体层所形成。也可在此外侧,形成例如w层等其它导电层。此时,w层发挥连接栅极金属层的金属配线层的作用。除w层以外也可使用单层或多层金属层。此外,虽使用了hfo2层23作为栅极绝缘层,但也可分别使用由单层或多层所构成的其它材料层。此点在本发明的其它实施方式中也复相同。

[0186]

在第一实施方式中,si柱6a至6f的俯视观察时的形状为圆形。另外,si柱6a至6f的一部分或所有俯视观察时的形状,可为圆形、椭圆、朝一方向延伸较长的形状等。另外,在从sram区域离开地形成的逻辑电路区域中,也可依据逻辑电路设计而在逻辑电路区域上混合地形成俯视观察时形状不同的si柱。这些各点在本发明的其它实施方式中也复相同。

[0187]

此外,在第一实施方式中为连接于si柱6a至6f的底部而形成了n

层3aa、3ab、3ba、3bb、p

层4aa、4bb。也可在n

层3aa、3ab、33ba、3bb、p

层4aa、4bb上表面形成金属、硅化物等合金层。此外,也可在si柱6a至6f的底部的外周,形成通过例如磊晶结晶成长法所形成的含有供体或受体杂质的p

层或n

层,以形成sgt的源极或汲极杂质区域。此时,也可在与通过磊晶结晶成长法所形成的n

层或p

层相接的si柱内部形成n

层或p

层,也可不形成n

层或p

层。或者,也可以邻接于这些p

层、n

层的方式设置延伸的金属层或合金层。此点在本发明的其它实施方式中也复相同。

[0188]

此外,在第一实施方式中,虽在p层基板1上形成sgt,但也可使用soi(silicon on insulator,绝缘体上硅薄膜)基板以取代p层基板1。或者,若是发挥作为基板的作用,也可使用其它材料基板。此点在本发明的其它实施方式中也复相同。

[0189]

此外,在第一实施方式中,虽已说明了在si柱6a至6f的上下,使用具有相同极性的导电性的n

层3aa、3ab、3ba、3bb、3aa、3ab、3ba、3bb、p

层44b、44g、n

层32a、32c、32d、32f、p

层32b、32e而构成源极、汲极的sgt,但本发明也可适用于具有极性不同的源极、汲极的通道型sgt。此点在本发明的其它实施方式中也复相同。

[0190]

此外,在第一实施方式中为于形成了栅极hfo2层23、栅极tin层24a、24b、240c、24d之后,形成n

层43a、43c、43d、43e、43f、44a、44c、44d、44e、44f、44h、p

层43b、43g、44b、44g。相对于此,也可在形成了n

层32a、32c、32d、32f、p

层32b、32e之后,形成栅极hfo2层23、栅极tin层24a、24b、240c、24d。此点在本发明的其它实施方式中也复相同。

[0191]

此外,在第二实施方式中,形成通过ald法所形成的薄的单结晶si层45、和通过磊晶结晶成长法所形成的含有受体杂质的p

层46。薄的单结晶si层45为用以获得结晶性良好的p

层46的材料层。若为用以获得结晶性良好的p

层46的材料层,也可为其它单层或多层的材料层。

[0192]

此外,在纵型nand型快闪内存(flash memory)电路中,是以半导体柱为通道,朝垂直方向形成多段由包围该半导体柱的通道氧化层、电荷存储层、层间绝缘层、控制导体层所构成的内存单元。在这些内存单元的两端的半导体柱中,具有对应源极的源极线杂质层、及对应汲极的位元线杂质层。此外,相对于一个内存单元,若其两侧的内存单元的一方为源极,则另一方则发挥作为汲极的作用。如此,纵型nand型快闪内存电路为sgt电路的一种。因此,本发明也可应用于与nand型快闪内存电路的混合电路。

[0193]

本发明在不脱离本发明的广义的精神与范围下,也可进行各种实施方式及变更。此外,上述的实施方式为用以说明本发明的一实施例,非限定本发明的范围。上述实施例及变形例可任意地组合。另外,任选而除去上述实施方式的构成要件的一部分也属本发明的技术思想的范围内。

[0194]

本技术主张根据2019年7月11日所申请的日本国际申请第pct/jp2019/027541号的优先权。成为此基础的专利申请的揭示内容整体作为参照包含于本技术中。

[0195]

[产业上的可利用性]

[0196]

依据本发明的柱状半导体装置及其制造方法,可获得高密度的柱状半导体装置。

[0197]

附图标记说明

[0198]

1:p层基板

[0199]

2,2a,2b,2a,2b:n层

[0200]

3,3aa,3ab,3ba,3bb,3aa,3ab,3ba,3bb,32a,32c,32d,32f,32a,32c,32d,32f,46a,46c,46d,46e,47a,47c,47d,47e:n

层

[0201]

4a,4b,4aa,4bb,4aa,4ba,32b,32e,32b,32e,40b,46,46b,47b,47e:p

层

[0202]

6:i层

[0203]

7,10,7a,7b,7c,7d,7e,7f,49a,49b,49c,49d,49e:遮罩材料层

[0204]

9a,9b,10,10a,10b,12aa,12ab,2ba,12bb,17a,17b:带状遮罩材料层

[0205]

19a,19b,19c,19d,19e,19f,19g,19h:矩形的遮罩材料层

[0206]

8:sige层

[0207]

8a,8b:带状sige层

[0208]

13a,13b,13c,16,27,27a,35a,35b,41:sin层

[0209]

9a,9b,13aa,13ab,13ba,13bb:带状sin层

[0210]

6a,6b,6c,6d,6e,6f,6a,6b,6c,6d,6e,6f:si柱

[0211]

15,22,22a,25,25a,28a,28b,28c,28d,28e,28f,31a,31b31c,31d,31e,31f,37,38,38,39,40,49,50,51,52:sio2层

[0212]

20a,20b,20c,20d,20e,20f,20g,20h:sin柱

[0213]

21a,21b,55a,55b:si柱台

[0214]

21a,21b,30a,30b,30c,30d,30e,30f,30a,30b,30c,30d,30e,30f,43,43a:凹部

[0215]

23,23a:hfo2层

[0216]

24a,24b,24c,24d,24a,24b,24c,24d:tin层

[0217]

33a,33b,33c,33d,33e,33f,34a,34b,48a,48b,48d,48

[0218]

え

,48f,50a,50b,50c,50d,50e:w层

[0219]

29:alo层

[0220]

42:阻剂层

[0221]

45:si层

[0222]

c1,c2,c3,c4,c5,c6,c7,c8,c9,c10,ca,cb,cc,cd,ce,cf,cg,ch:接触孔

[0223]

wl:字符配线金属层

[0224]

bl:位元配线金属层

[0225]

rbl:反转位元配线金属层

[0226]

vss1,vss2:接地配线金属层

[0227]

vdd,vdd:电源配线金属层

[0228]

xc1,xc2:连接配线金属层。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。