技术特征:

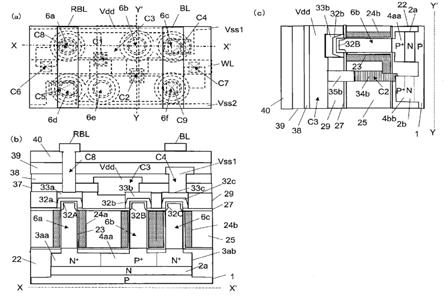

1.一种柱状半导体装置的制造方法,该柱状半导体装置具有:半导体柱,朝垂直方向立于基板上;栅极绝缘层,包围前述半导体柱;及栅极导体层,包围前述栅极绝缘层;该柱状半导体装置的制造方法具有下列步骤:形成第一半导体柱和第二半导体柱的步骤,该第一半导体柱为前述半导体柱而且在其顶部具有第一材料层,该第二半导体柱邻接于前述第一半导体柱且为前述半导体柱,而且在其顶部具有第二材料层;于比前述栅极导体层上表面更上方,且于前述第一半导体柱和前述第二半导体柱的顶部外周部形成第一层间绝缘层的步骤;形成第三材料层和第四材料层的步骤,该第三材料层位于前述第一层间绝缘层上而且包围前述第一半导体柱的顶部侧面,该第四材料层位于前述第一层间绝缘层上而且包围前述第二半导体柱的顶部侧面;在与前述第三材料层和前述第四材料层的侧面相接的外周部形成第二层间绝缘层的步骤;将前述第一材料层、前述第二材料层、前述第三材料层、和前述第四材料层予以去除而形成第一凹部和第二凹部与步骤的步骤,该第一凹部包围前述第一半导体柱的顶部,该第二凹部包围前述第二半导体柱的顶部;以包围前述第一半导体柱的顶部的方式在前述第一凹部内形成第一杂质层的步骤,与以包围前述第二半导体柱的顶部的方式在前述第二凹部内形成第二杂质层的步骤;于前述第一杂质层上而且在前述第一凹部内形成第一导体层的步骤,与于前述第二杂质层上而且在前述第二凹部内形成第二导体层的步骤;及形成连接前述第一导体层和前述第二导体层的第一配线导体层的步骤;于俯视观察时,在前述第一配线导体层的形成区域,未形成有非为前述第一半导体柱和前述第二半导体柱的其它的前述半导体柱。2.根据权利要求1所述的柱状半导体装置的形成方法,具有下列步骤:在前述第一导体层、前述第二导体层、和前述第二层间绝缘层的上方,形成第三层间绝缘层的步骤;在前述第三层间绝缘层,形成俯视观察时与前述第一导体层的一部分区域和前述第二导体层的一部分区域重叠而且相接的第一带状接触孔的步骤;及填埋前述第一带状接触孔以形成前述第一配线导体层的步骤;于俯视观察时,前述第一导体层和前述第二导体层的一部分区域比前述第一带状接触孔更突出于外侧。3.根据权利要求2所述的柱状半导体装置的形成方法,具有下列步骤:在形成前述第二层间绝缘层之后,形成俯视观察时与前述第一材料层和前述第三材料层的一部分区域、及前述第二材料层和前述第四材料层的一部分区域重叠而且予以相连接而呈现空隙的第一遮罩材料层的步骤;以前述第一遮罩材料层为遮罩,将前述第一材料层、前述第三材料层、前述第二材料层、前述第四材料层、和前述第二层间绝缘层进行蚀刻以形成第三凹部的步骤;在前述第三凹部内,与前述第一杂质层和前述第二杂质层的形成同时地形成与前述第一杂质层和前述第二杂质层相连接的第三杂质层的步骤;

于前述第一杂质层、前述第二杂质层、和前述第三杂质层的上方而且在前述第三凹部内形成第三导体层的步骤;及在前述第三导体层形成与其连接的前述第一配线导体层的步骤;于俯视观察时,前述第一带状接触孔位于前述第三导体层的内侧,而且前述第一杂质层、前述第二杂质层、和前述第三杂质层由相同的半导体材料层所构成。4.根据权利要求3所述的柱状半导体装置的形成方法,其中,前述第三导体层为前述第一配线导体层。5.根据权利要求1所述的柱状半导体装置的制造方法,通过磊晶结晶成长而形成前述第一杂质层和前述第二杂质层。6.根据权利要求1所述的柱状半导体装置的制造方法,具有下列步骤:在前述第一凹部和前述第二凹部的底部面上形成单结晶半导体薄膜层的步骤;及接着在前述第一凹部和前述第二凹部形成前述第一杂质层和前述第二杂质层的步骤。7.根据权利要求1所述的柱状半导体装置的形成方法,在前述第一半导体柱和前述第二半导体柱形成有sram(静态随机存取内存;static random access memory)单元电路的负载用sgt(环绕栅极晶体管;surrounding gate transistor)。8.一种柱状半导体装置,具有:第一半导体柱,朝垂直方向立于基板上;第二半导体柱,邻接于前述第一半导体柱而站立;栅极绝缘层,其上表面位置位于比前述第一半导体柱和前述第二半导体柱的顶部上表面更下方,而且包围前述第一半导体柱和前述第二半导体柱;栅极导体层,包围前述栅极绝缘层;第一层间绝缘层,位于前述栅极导体层上;第一杂质层和第二杂质层,该第一杂质层覆盖前述第一半导体柱顶部,而且于俯视观察时,其外周与前述第一半导体柱的外周等宽地隔开,该第二杂质层覆盖前述第二半导体柱顶部,而且于俯视观察时,与其外周等宽地隔开;第一导体层和第二导体层,该第一导体层位于前述第一杂质层上,该第二导体层位于前述第二杂质层上;第二层间绝缘层,位于前述第一杂质层、前述第二杂质层、前述第一导体层、和前述第二导体层的外周部;第三层间绝缘层,位于前述第一导体层、前述第二导体层、和前述第二层间绝缘层的上方;第一带状接触孔,位于前述第三层间绝缘层,且于俯视观察时,与前述第一导体层的一部分区域和前述第二导体层的一部分区域重叠而且相接;及第一配线导体层,填埋前述第一带状接触孔而成;于俯视观察时,前述第一导体层和前述第二导体层的一部分区域比前述第一带状接触孔更突出于外侧。9.根据权利要求8所述的柱状半导体装置,具有:第三杂质层,位于与前述第一杂质层和前述第二杂质层相同的表面上,而且与前述第一杂质层和前述第二杂质层相连接;

第三导体层,位于前述第一杂质层、第二杂质层、和前述第三杂质层的上方,而且于俯视观察时,与前述第一杂质层、第二杂质层、和前述第三杂质层为相同的形状;及前述第一配线导体层,连接于前述第三导体层;于俯视观察时,前述第一带状接触孔位于前述第三导体层的内侧。10.根据权利要求9所述的柱状半导体装置,其中,前述第三导体层为前述第一配线导体层。11.根据权利要求8所述的柱状半导体装置,其中,前述第一杂质层和前述第二杂质层为磊晶结晶成长半导体材料层。12.根据权利要求8所述的柱状半导体装置,在前述第一杂质层和前述第二杂质层的侧面及底部具有单结晶半导体薄膜层。13.根据权利要求8所述的柱状半导体装置,在前述第一半导体柱和前述第二半导体柱设有sram(静态随机存取内存;static random access memory)单元电路的负载用sgt((环绕栅极晶体管surrounding gate transistor)。

技术总结

覆盖Si柱(6b、6e)的顶部整体,而且于俯视观察时与Si柱(6b、6e)自行对准地形成等宽地包围Si柱(6b、6e)的P

技术研发人员:原田望

受保护的技术使用者:新加坡优尼山帝斯电子私人有限公司

技术研发日:2020.03.19

技术公布日:2022/3/1

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。