1.本发明涉及半导体制造技术领域,尤其涉及一种三维存储器及其形成方法。

背景技术:

2.随着平面型闪存存储器的发展,半导体的生产工艺取得了巨大的进步。但是最近几年,平面型闪存的发展遇到了各种挑战:物理极限、现有显影技术极限以及存储电子密度极限等。在此背景下,为解决平面闪存遇到的困难以及追求更低的单位存储单元的生产成本,各种不同的三维(3d)闪存存储器结构应运而生,例如3d nor(3d或非)闪存和3d nand(3d与非)闪存。

3.其中,3d nand存储器以其小体积、大容量为出发点,将储存单元采用三维模式层层堆叠的高度集成为设计理念,生产出高单位面积存储密度,高效存储单元性能的存储器,已经成为新兴存储器设计和生产的主流工艺。但是,当前三维存储器在形成复杂图案方面还存在缺陷,从而限制了三维存储器性能的提高。

4.因此,如何提高三维存储器的性能,是当前亟待解决的技术问题。

技术实现要素:

5.本发明提供一种三维存储器及其形成方法,用于解决现有技术中无法形成复杂图案的问题,以改善三维存储器的性能。

6.为了解决上述问题,本发明提供了一种三维存储器的形成方法,包括如下步骤:

7.提供基底;

8.形成包括第一刻蚀图案的第一牺牲层于所述基底上;

9.回填所述第一刻蚀图案,形成包括第二刻蚀图案的第二牺牲层于所述第一牺牲层上,在沿垂直于所述基底的方向上,所述第一刻蚀图案的投影与所述第二刻蚀图案的投影相交;

10.沿所述第二刻蚀图案刻蚀所述第一牺牲层,形成与所述第一刻蚀图案连通的第三刻蚀图案;

11.沿所述第一刻蚀图案和所述第三刻蚀图案刻蚀所述基底,于所述基底中形成组合图案。

12.可选的,形成包括第一刻蚀图案的第一牺牲层于所述基底上之前,还包括如下步骤:

13.形成掩模层于所述基底表面。

14.可选的,形成包括第一刻蚀图案的第一牺牲层于所述基底上的具体步骤包括:

15.形成第一牺牲层于所述掩模层表面;

16.刻蚀所述第一牺牲层,形成贯穿所述第一牺牲层的第一刻蚀图案,在沿平行于所述基底的顶面的方向上,所述第一刻蚀图案的截面包括第一连接图案、以及至少连接于所述第一连接图案一侧端部的第一外凸图案。

17.可选的,所述第一连接图案为矩形图案,所述第一外凸图案为圆形或者椭圆形图案。

18.可选的,所述第一外凸图案的数量为两个,且两个所述第一外凸图案连接于所述第一连接图案的相对两端部。

19.可选的,回填所述第一刻蚀图案,形成包括第二刻蚀图案的第二牺牲层于所述第一牺牲层上的具体步骤包括:

20.形成填充满所述第一刻蚀图案并覆盖所述第一牺牲层的第二牺牲层;

21.刻蚀所述第二牺牲层,形成贯穿所述第二牺牲层的所述第二刻蚀图案。

22.可选的,所述第二刻蚀图案包括第二连接图案、以及至少连接于所述第二连接图案一侧端部的第二外凸图案。

23.可选的,所述第二连接图案为矩形图案,所述第二外凸图案为圆形或者椭圆形图案。

24.可选的,所述第二外凸图案的数量为两个,且两个所述第二外凸图案连接于所述第二连接图案的相对两端部。

25.可选的,在沿垂直于所述基底的方向上,所述第一刻蚀图案的投影与所述第二刻蚀图案的投影相交位置的夹角小于或者等于90度。

26.可选的,沿所述第二刻蚀图案刻蚀所述第一牺牲层,形成与所述第一刻蚀图案连通的第三刻蚀图案的具体步骤包括:

27.沿所述第二刻蚀图案刻蚀所述第一牺牲层,形成贯穿所述第一牺牲层的第三刻蚀图案,所述第三刻蚀图案包括第三连接图案、以及至少连接于所述第三连接图案一侧端部的第三外凸图案,所述第三连接图案与所述第一连接图案相交并连通;

28.去除所述第二牺牲层。

29.可选的,所述基底包括衬底以及位于所述衬底上的堆叠层;沿所述第一刻蚀图案和所述第三刻蚀图案刻蚀所述基底,于所述基底中形成组合图案的具体步骤包括:

30.沿所述第一刻蚀图案和所述第三刻蚀图案刻蚀所述掩模层,形成贯穿所述掩模层的组合刻蚀图案;

31.沿所述组合刻蚀图案刻蚀所述堆叠层,形成贯穿所述堆叠层的组合图案。

32.可选的,所述组合图案在沿平行于所述基底的表面的方向上的截面为包括多个外凸部的花瓣形,且相邻两个所述外凸部相交位置的夹角小于或者等于90度。

33.为了解决上述问题,本发明还提供了一种三维存储器,包括:

34.基底;

35.组合图案,位于所述基底内,在沿平行于所述基底的表面的方向上,所述组合图案的截面为包括多个外凸部的花瓣形,且相邻两个所述外凸部相交位置的夹角小于或者等于90度。

36.可选的,所述基底包括堆叠层;

37.所述组合图案为贯穿所述堆叠层的沟道孔。

38.可选的,所述外凸部的数量为4个,且4个所述外凸部呈中心对称分布。

39.可选的,多个所述外凸部的形状均相同;或者,

40.至少两个所述外凸部的形状不同。

41.本发明提供的三维存储器及其形成方法,通过将最终要形成的组合图案拆分成多个部分,且将多个部分分别于不同的工艺步骤中、形成于不同的膜层上之后,再进行组合,从而降低了组合图案的形成难度,改善了最终形成的组合图案的形貌,实现了在半导体结构中形成复杂图案,确保了最终形成的多个组合图案的形貌一致性,从而改善了三维存储器的性能。

附图说明

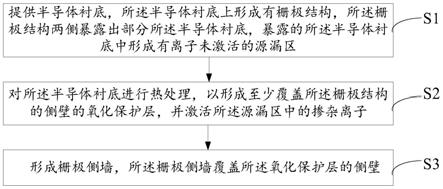

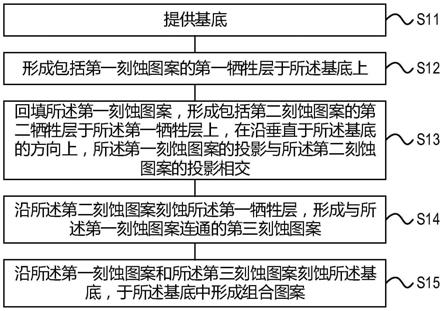

42.附图1是本发明具体实施方式中三维存储器的形成方法流程图;

43.附图2a-2j是本发明具体实施方式在形成三维存储器的过程中主要的工艺结构示意图;

44.附图3是本发明具体实施方式中组合图案的俯视结构示意图;

45.附图4是本发明具体实施方式中对组合图案进行拆分的示意图;

46.附图5是本发明具体实施方式中三维存储器的结构示意图。

具体实施方式

47.下面结合附图对本发明提供的三维存储器及其形成方法的具体实施方式做详细说明。

48.由于光学极限分辨率和图形尺寸的限制,在光阻层上形成包括多个子图案的复杂图案时,相邻两个子图案之间的边界容易连接在一起,例如在形成花瓣状图案时,相邻两个花瓣的边缘连接在一起,导致相邻两个花瓣之间的角度大于90度(即为钝角),当采用光刻、刻蚀工艺将所述光阻层中的复杂图案向下转移至晶圆上时,于所述晶圆上形成的图案基本为边界模糊的近似矩形图案,与预设的所述复杂图案的形貌存在较大偏差,导致所述复杂图案无法在晶圆上实现,从而限制了三维存储器性能的提高。同时,由于因光学极限分辨率和图形尺寸的限制导致的图案差异是不确定的,导致在晶圆上形成的多个复杂图案之间的一致性较差,从而导致三维存储器的性能稳定性较差。

49.本具体实施方式提供了一种三维存储器,附图1是本发明具体实施方式中三维存储器的形成方法流程图,附图2a-2j是本发明具体实施方式在形成三维存储器的过程中主要的工艺结构示意图。本具体实施方式中所述的三维存储器可以是但不限于3d nand存储器。如图1、图2a-图2j所示,所述三维存储器的形成方法,包括如下步骤:

50.步骤s11,提供基底20。

51.具体来说,所述基底20可以仅包括衬底,也可以包括衬底以及位于所述衬底上的若干半导体层。所述衬底可以是si衬底、ge衬底、sige衬底、soi(silicon on insulator,绝缘体上硅)衬底或者goi(germanium on insulator,绝缘体上锗)衬底等。

52.步骤s12,形成包括第一刻蚀图案221的第一牺牲层22于所述基底20上,如图2b所示。

53.可选的,形成包括第一刻蚀图案221的第一牺牲层22于所述基底20上之前,还包括如下步骤:

54.形成掩模层21于所述基底20表面。

55.可选的,形成包括第一刻蚀图案221的第一牺牲层22于所述基底20上的具体步骤

包括:

56.形成第一牺牲层22于所述掩模层21表面;

57.刻蚀所述第一牺牲层22,形成贯穿所述第一牺牲层22的第一刻蚀图案221,在沿平行于所述基底20的顶面的方向上,所述第一刻蚀图案221的截面包括第一连接图案2211、以及至少连接于所述第一连接图案2211一侧端部的第一外凸图案2212,如图2c所示。

58.具体来说,在沉积所述第一牺牲层22于所述基底20上之前,于所述基底20表面形成所述掩模层21,以确保最后转移至所述基底20中的图案的形貌,并避免图案化所述第一牺牲层22的过程中对所述基底20造成损伤。所述掩模层21也以为有机掩模层(例如碳掩模层),也可以为硬掩模层(例如氮化硅掩模层)。之后,沉积第一牺牲层22于所述掩模层21的表面、并沉积图案化的第一光阻层23于所述第一牺牲层22背离所述基底20的表面,如图2a所示。所述第一光阻层23中具有沿垂直于所述基底20的顶面(即所述基底20朝向所述第一牺牲层22的表面)方向贯穿所述第一光阻层23的第一窗口231。沿所述第一窗口231向下刻蚀所述第一牺牲层22,于所述第一牺牲层22中形成沿垂直于所述基底20的顶面方向贯穿所述第一牺牲层22的所述第一刻蚀图案221,去除所述第一光阻层23之后,得到如图2b所示的结构。

59.可选的,所述第一连接图案2211为矩形图案,所述第一外凸图案2212为圆形或者椭圆形图案。

60.本具体实施方式中所述的第一外凸图案2212是指沿平行于所述第一连接图案2211的中心指向边缘的方向凸出的图案。

61.可选的,所述第一外凸图案2212的数量为两个,且两个所述第一外凸图案2212连接于所述第一连接图案2211的相对两端部。

62.图2c是所述第一刻蚀图案的俯视结构示意图,图2b是图2c沿ab线方向的截面示意图。附图3是本发明具体实施方式中组合图案的俯视结构示意图,附图4是本发明具体实施方式中对组合图案进行拆分的示意图。举例来说,可以根据最终所要形成的组合图案的形状来设置所述第一刻蚀图案。当最终所要形成的组合图案27在沿平行于所述基底20的顶面方向的截面形状为如图3所示的花瓣形形状时,可以采用如图4所示的方式,对所述组合图案27进行拆分,将一个花瓣形形状的所述组合图案27拆分成一个哑铃状的所述第一刻蚀图案221和一个哑铃状的第二刻蚀图案241,哑铃状的所述第一刻蚀图案221与哑铃状的所述第二刻蚀图案241的倾斜方向不同。

63.以上拆分方式仅是示例性说明。在其他具体实施方式中,本领域技术人员可以根据实际需要对所述组合图案进行拆分,例如可以将一个花瓣形的所述组合图案27拆分成四个刻蚀图案,每个所述刻蚀图案包括一个圆形图案和一个与所述圆形图案相连的矩形图案。在拆分所述组合图案的过程中,拆分成的多个所述刻蚀图案可以相同、也可以互不相同,本领域技术人员根据实际的刻蚀精度要求进行选择。本具体实施方式中所述的多个是指两个以上。

64.步骤s13,回填所述第一刻蚀图案221,形成包括第二刻蚀图案241的第二牺牲层24于所述第一牺牲层22上,如图2e所示,在沿垂直于所述基底20的方向上,所述第一刻蚀图案221的投影与所述第二刻蚀图案241的投影相交。

65.可选的,回填所述第一刻蚀图案221,形成包括第二刻蚀图案241的第二牺牲层24

于所述第一牺牲层22上的具体步骤包括:

66.形成填充满所述第一刻蚀图案221并覆盖所述第一牺牲层22的第二牺牲层24;

67.刻蚀所述第二牺牲层24,形成贯穿所述第二牺牲层24的所述第二刻蚀图案241。

68.可选的,所述第二刻蚀图案241包括第二连接图案2411、以及至少连接于所述第二连接图案2411一侧端部的第二外凸图案2412。

69.可选的,所述第二连接图案2411为矩形图案,所述第二外凸图案2412为圆形或者椭圆形图案。

70.可选的,所述第二外凸图案2412的数量为两个,且两个所述第二外凸图案2412连接于所述第二连接图案2412的相对两端部。

71.图2f是所述第一刻蚀图案的俯视结构示意图,图2e是图2f沿cd线方向的截面示意图。具体来说,在形成所述第一刻蚀图案221之后,形成填充满所述第一刻蚀图案221并覆盖所述第一牺牲层22的第二牺牲层24,并形成覆盖所述第二牺牲层24的图案化的第二光阻层25,如图2d所示。所述第二光阻层25中具有沿垂直于所述基底20的顶面的方向贯穿所述第二光阻层25的第二窗口251。沿所述第二窗口251向下刻蚀所述第二牺牲层24,形成沿垂直于所述基底20的顶面的方向贯穿所述第二牺牲层24的所述第二刻蚀图案241。所述第二刻蚀图案241的截面形状为哑铃状,包括矩形的所述第二连接图案2411和圆形或者椭圆形形状的所述第二外凸图案2412。所述第二外凸图案2412指沿平行于所述第二连接图案2411的中心指向边缘的方向凸出的图案。

72.当所述第一刻蚀图案221与所述第二刻蚀图案241均为哑铃状图案时,所述第一刻蚀图案221的投影与所述第二刻蚀图案241的投影相交是指,所述第一刻蚀图案221中的所述第一连接图案2211的投影与所述第二刻蚀图案241中的所述第二连接图案2411的投影相交。

73.可选的,在沿垂直于所述基底20的方向上,所述第一刻蚀图案221的投影与所述第二刻蚀图案241的投影相交位置的夹角小于或者等于90度。

74.举例来说,所述第一刻蚀图案221中的所述第一连接图案2211的投影与所述第二刻蚀图案241中的所述第二连接图案2411的投影相交位置的角度小于或者等于90度。

75.步骤s14,沿所述第二刻蚀图案241刻蚀所述第一牺牲层22,形成与所述第一刻蚀图案221连通的第三刻蚀图案222,如图2g。

76.可选的,沿所述第二刻蚀图案241刻蚀所述第一牺牲层22,形成与所述第一刻蚀图案221连通的第三刻蚀图案222的具体步骤包括:

77.沿所述第二刻蚀图案241刻蚀所述第一牺牲层22,形成贯穿所述第一牺牲层22的第三刻蚀图案222,所述第三刻蚀图案222包括第三连接图案、以及至少连接于所述第三连接图案一侧端部的第三外凸图案,所述第三连接图案与所述第一连接图案相交并连通;

78.去除所述第二牺牲层24。

79.图2h是所述第一牺牲层22中包括所述第一刻蚀图案221和所述第三刻蚀图案222的初始组合刻蚀图案的俯视结构示意图,图2g是图2h沿ef线方向的截面示意图。由于本具体实施方式先于所述第二牺牲层24中形成所述第二刻蚀图案241,再将所述第二刻蚀图案241向下转移至所述第一牺牲层22中,从而与所述第一牺牲层22中的所述第一刻蚀图案221组合成所述初始组合刻蚀图案,从而能够减小甚至是避免光学极限分辨率和图形尺寸对所

要形成的所述初始组合刻蚀图案的形貌的影响,从而使得所述初始组合刻蚀图案中的所述第一刻蚀图案221与所述第三刻蚀图案222相交位置的夹角γ(即所述第一刻蚀图案221在沿垂直于所述基底20的方向上的投影与所述第二刻蚀图案241在沿垂直于所述基底20的方向上的投影相交位置的夹角)小于或者等于90度。

80.步骤s15,沿所述第一刻蚀图案221和所述第三刻蚀图案222刻蚀所述基底20,于所述基底20中形成组合图案27,如图2j所示和图3所示,图2j是图3沿gh线方向的截面示意图。

81.可选的,所述基底20包括衬底以及位于所述衬底上的堆叠层;沿所述第一刻蚀图案221和所述第三刻蚀图案222刻蚀所述基底,于所述基底20中形成组合图案27的具体步骤包括:

82.沿所述第一刻蚀图案221和所述第三刻蚀图案222刻蚀所述掩模层21,形成贯穿所述掩模层21的组合刻蚀图案;

83.沿所述组合刻蚀图案刻蚀所述堆叠层,形成贯穿所述堆叠层的组合图案。

84.具体来说,所述堆叠层可以包括沿垂直于所述衬底指向所述堆叠层的方向交替堆叠的第三牺牲层和层间绝缘层。沿所述掩模层21中的所述组合刻蚀图案向下刻蚀所述堆叠层,形成贯穿所述堆叠层的所述组合图案27,并以所述组合图案27作为所述堆叠层中的沟道孔。

85.可选的,所述组合图案27在沿平行于所述基底20的表面的方向上的截面为包括多个外凸部的花瓣形,且相邻两个所述外凸部相交位置的夹角小于或者等于90度。

86.举例来说,如图3所示,所述组合图案27包括第一外凸部271和与所述第一外凸部271相邻的第二外凸部272,所述第一外凸部271的边缘与所述第二外凸部272的边缘之间的夹角δ(即所述第一外凸部271与所述第二外凸部272相交位置的夹角)小于或者等于90度。

87.本具体实施方式是以所述组合图案27包括四个外凸部为例进行说明,本领域技术人员可以根据实际需要设置所述外凸部的数量,例如可以是两个、三个、或者五个以上。本具体实施方式中所述组合图案27中的所有所述外凸部的形状和尺寸均相同。在其他具体实施方式中,所述组合图案27中的所述外凸部的形状和/或尺寸也可以不同。

88.不仅如此,本具体实施方式还提供了一种三维存储器。附图5是本发明具体实施方式中三维存储器的结构示意图。本具体实施方式提供的三维存储器可以采用如图1、图2a-图2j和图3-图4所示的三维存储器的形成方法形成。本具体实施方式中所述的三维存储器可以是但不限于3d nand存储器。如图3-图5所示,所述三维存储器,包括:

89.基底20;

90.组合图案27,位于所述基底20内,在沿平行于所述基底20的表面的方向上,所述组合图案27的截面为包括多个外凸部的花瓣形,且相邻两个所述外凸部相交位置的夹角小于或者等于90度。

91.可选的,所述基底20包括堆叠层;

92.所述组合图案27为贯穿所述堆叠层的沟道孔。

93.可选的,所述外凸部的数量为4个,且4个所述外凸部呈中心对称分布。

94.本具体实施方式通过将多个(例如4个)所述外凸部呈中心对称分布,可以简化掩模板的设计操作,从而简化三维存储器的制造流程。

95.本具体实施方式是以所述外凸部的数量为4个为例进行说明。在其他具体实施方

式中,所述外凸部的数量可以为任意数量,例如3个、5个或者6个以上。

96.可选的,多个所述外凸部的形状均相同;或者,

97.至少两个所述外凸部的形状不同。

98.本具体实施方式提供的三维存储器及其形成方法,通过将最终要形成的组合图案拆分成多个部分,且将多个部分分别于不同的工艺步骤中、形成于不同的膜层上之后,再进行组合,从而降低了组合图案的形成难度,改善了最终形成的组合图案的形貌,实现了在半导体结构中形成复杂图案,确保了最终形成的多个组合图案的形貌一致性,从而改善了三维存储器的性能。

99.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。