1.本公开的实施例大体上涉及微电子器件,且更具体地说,涉及具有倒装芯片架构的射频(rf)功率管芯和包含倒装芯片rf功率管芯的功率放大器模块。

背景技术:

2.功率放大模块(pam)通常包括模块基板和至少一个射频(rf)功率管芯,所述rf功率管芯以非倒置朝向安装到模块基板。所述模块基板可以是例如印刷电路板(pcb)、陶瓷基板或具有与rf功率管芯电互连的导电布线特征的另一基板。给定的pam可以包含单个rf功率管芯或多个rf功率管芯以及任意数目的其它微电子部件,例如离散放置的电容器和电阻器。pam内的一个或多个rf功率管芯在操作期间可能容易产生多余热量,特别是当在更高射频(例如,接近或超过3千兆赫的频率)下操作或使用例如分层氮化镓管芯结构之类的功率密集管芯技术制造时。通过常规设计,rf功率管芯通常包括用作rf功率管芯的后侧(例如,接地)触点的金属化后侧,所述金属化后侧电耦合到集成到管芯中的晶体管电路的对应端;例如,在场效应晶体管(fet)的情况下,fet的源极端可以通过这样的后侧触点电耦合到接地。与晶体管的其它端(例如,在fet的情况下为栅极端和漏极端)的接触可以形成为位于在rf功率管芯前侧上的键合垫,并且具体地说,形成在汇集在管芯主体前侧上方的多层系统的外部端表面中。当安装在给定pam内时,可以在前侧键合垫与模块基板的对应电布线特征之间形成引线键合,以完成rf功率管芯的电互连。

技术实现要素:

3.根据本发明的第一方面,提供一种功率放大器模块(pam),包括:

4.模块基板,其具有管芯支撑表面和暴露于所述管芯支撑表面处的多个导电触点;以及

5.第一射频(rf)功率管芯,其以倒置朝向安装到所述模块基板的所述管芯支撑表面,所述第一rf功率管芯包括:

6.管芯主体,其具有前侧和相对的后侧;

7.晶体管,其具有在所述管芯主体中形成的有源区;

8.前侧层系统,其形成在所述管芯主体的所述前侧上方,并且包含图案化金属层,所述图案化金属层限定电耦合到所述晶体管的所述有源区的第一、第二和第三分支电极结构;以及

9.前侧输入/输出(i/o)接口,其形成在所述前侧层系统的外部端部分中,所述前侧i/o接口包含第一、第二和第三键合垫;

10.其中所述第一、第二和第三键合垫分别电耦合到所述第一、第二和第三分支电极结构,而所述第三键合垫另外电耦合到所述模块基板的所述多个导电触点。

11.在一个或多个实施例中,所述第一rf功率管芯包括场效应晶体管(fet);

12.其中所述第一、第二和第三分支电极结构分别包括分支漏极电极结构、分支栅极

电极结构和分支源极电极结构;并且

13.其中所述第一、第二和第三键合垫分别包括漏极键合垫、栅极键合垫和源极键合垫。

14.在一个或多个实施例中,所述分支源极电极结构包括:

15.多个源极流道;以及

16.源极歧管,所述多个源极流道从所述源极歧管延伸,所述源极歧管电耦合在所述多个源极流道与所述源极键合垫之间。

17.在一个或多个实施例中,所述分支漏极电极结构包括:

18.多个漏极流道,其与所述多个源极流道交错;以及

19.漏极歧管,所述多个漏极流道从所述漏极歧管延伸,所述漏极歧管电耦合在所述多个漏极流道与所述漏极键合垫之间。

20.在一个或多个实施例中,所述分支栅极电极结构包括:

21.多个栅极流道,其基本上平行于所述多个源极流道延伸;以及

22.栅极歧管,所述多个栅极流道从所述栅极歧管延伸,所述栅极歧管电耦合在所述多个栅极流道与所述栅极键合垫之间。

23.在一个或多个实施例中,在从所述栅极歧管延伸到覆盖在所述晶体管的所述有源区上的位置时,所述多个栅极流道在所述源极歧管下方或上方通过。

24.在一个或多个实施例中,所述栅极歧管和所述漏极歧管形成在所述前侧层系统中的不同层级处。

25.在一个或多个实施例中,所述前侧层系统包括:

26.第一图案化金属层,所述栅极键合垫、所述源极歧管和所述多个源极流道形成在所述第一图案化金属层中;以及

27.第二图案化金属层,所述栅极歧管和所述多个栅极流道形成在所述第二图案化金属层中。

28.在一个或多个实施例中,所述管芯主体的至少一部分由具有超过520欧姆/厘米的电阻的高电阻率半导体材料构成。

29.在一个或多个实施例中,所述rf功率管芯另外包括形成在所述管芯主体的所述后侧上方的背垫金属结构,所述背垫金属结构与所述晶体管的所述有源区电隔离;并且

30.其中所述管芯主体不具有基板通孔。

31.在一个或多个实施例中,所述rf功率管芯另外包括形成在所述管芯主体的所述后侧上方的背垫金属结构;并且

32.其中所述pam另外包括:

33.包覆模制主体,其键合到所述管芯支撑表面并且至少部分地包封所述第一rf功率管芯;以及

34.热延伸部,其嵌入所述包覆模制主体内,热耦合到所述背垫金属结构,并且从邻近所述背垫金属结构的位置延伸到所述包覆模制主体的外部顶部表面。

35.根据本发明的第二方面,提供一种功率放大器模块(pam),包括:

36.模块基板,其具有管芯支撑表面;以及

37.射频(rf)功率管芯,其以倒置朝向安装到所述模块基板的所述管芯支撑表面,其

中所述rf功率管芯的接触表面面向所述管芯支撑表面,所述rf功率管芯包括:

38.管芯主体,其具有前侧和相对的后侧;

39.前侧层系统,其形成在所述管芯主体的所述前侧上方,并且限定所述rf功率管芯的所述接触表面;

40.场效应晶体管(fet),其形成在所述管芯主体中并且形成在所述前侧层系统中,所述fet包括分支漏极电极结构、分支栅极电极结构和分支源极电极结构;以及

41.前侧输入/输出(i/o)接口,其另外形成在所述前侧层系统的外部端部分中,所述前侧i/o接口包括分别电耦合到所述分支漏极电极结构、所述分支栅极电极结构和所述分支源极电极结构的第一漏极键合垫、第一栅极键合垫和第一源极键合垫。

42.在一个或多个实施例中,所述分支源极电极结构包括:

43.多个源极流道,其基本上平行于第一轴线延伸;以及

44.源极歧管,所述多个源极流道从所述源极歧管延伸,所述源极歧管电耦合在所述多个源极流道与所述第一源极键合垫之间。

45.在一个或多个实施例中,所述源极歧管位于邻近所述第一栅极键合垫的位置,同时通过如沿着所述第一轴线截取的隔离间隙与所述第一栅极键合垫间隔开。

46.在一个或多个实施例中,所述分支栅极电极结构包括:

47.栅极歧管,其位于比所述第一栅极键合垫更靠近所述管芯主体的所述前侧的位置;以及

48.多个栅极流道,其在所述源极歧管下方并且跨越所述fet的有源区从所述栅极歧管延伸。

49.在一个或多个实施例中,所述第一源极键合垫位于邻近所述源极歧管的第一侧的位置;并且

50.其中所述rf功率管芯另外包括第二源极键合垫,所述第二源极键合垫位于邻近与所述源极歧管的所述第一侧相对的所述源极歧管的第二侧的位置,如沿着垂直于所述第一轴线的第二轴线截取的。

51.在一个或多个实施例中,所述rf功率管芯包括多个栅极键合垫,其中所述第一栅极键合垫包括在所述多个栅极键合垫中;并且

52.其中所述rf功率管芯另外包括以下各项中的至少一个:

53.多个源极键合垫,其包括所述第一源极键合垫并且以交替关系与所述多个栅极键合垫交错;以及

54.多个漏极键合垫,其包括所述第一漏极键合垫并且以交替关系与所述多个栅极键合垫交错。

55.在一个或多个实施例中,所述rf功率管芯另外包括形成在所述管芯主体的所述后侧上方的背垫金属结构;并且

56.其中所述pam另外包括:

57.包覆模制主体,其键合到所述管芯支撑表面并且至少部分地包封所述rf功率管芯;以及

58.热延伸部,其嵌入所述包覆模制主体内,热耦合到所述背垫金属结构,并且从邻近所述背垫金属结构的位置延伸到所述包覆模制主体的外部顶部表面。

59.根据本发明的第三方面,提供一种射频(rf)功率管芯,包括:

60.管芯主体,其具有前侧和相对的后侧;

61.前侧层系统,其形成在所述管芯主体的所述前侧上方;

62.场效应晶体管(fet),其形成在所述管芯主体中并且形成在所述前侧层系统中,所述fet包括:

63.分支漏极电极结构;

64.分支栅极电极结构;

65.分支源极电极结构;以及

66.前侧输入/输出(i/o)接口,其另外形成在所述前侧层系统的外部端部分中,所述前侧i/o接口包括:

67.第一漏极键合垫,其电耦合到所述分支漏极电极结构;

68.第一栅极键合垫,其电耦合到所述分支栅极电极结构;以及

69.第一源极键合垫,其电耦合到所述分支源极电极结构。

70.在一个或多个实施例中,所述管芯主体不具有基板通孔,并且部分由具有超过520欧姆/厘米的电阻的高电阻率半导体材料构成。

71.本发明的这些和其它方面将根据下文中所描述的实施例显而易见,且参考这些实施例予以阐明。

附图说明

72.将结合附图在下文描述本发明的至少一个例子,其中相同标号表示相同元件,并且:

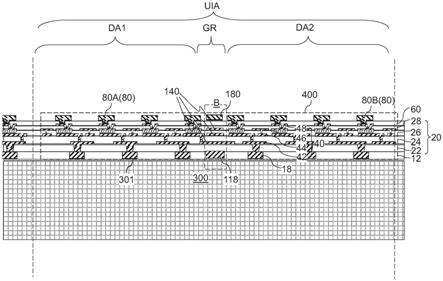

73.图1是如根据本公开的示例实施例示出并且以非倒置朝向描绘的具有倒装芯片架构的射频(rf)功率管芯的简化横截面视图;

74.图2是如根据本公开的示例实施例所示的功率放大模块(pam)的简化横截面视图,所述pam包含图1所示的倒装芯片rf功率管芯、rf功率管芯以倒置朝向安装到其上的模块基板以及沿着pam的顶部表面暴露的热接口;

75.图3和4分别是较大电子组件(部分示出)的简化横截面视图和等距分解视图,图2中所示的示例pam可并入其中,同时热接口热耦合到pam外部的组件级散热器;

76.图5和图6分别是如根据本公开的示例实施例所示的适当集成到图1-4所示的倒装芯片rf功率管芯中的晶体管布局(这里是场效应晶体管结构)的等距视图和平面视图;

77.图7、8和9分别是图5和6所示的示例晶体管布局的前侧层系统(部分示出)中包含的多个图案化金属层的平面视图、第一横截面视图和第二横截面视图;

78.图10和11分别是如根据本公开的另外的示例实施例所示的适当集成到具有倒装芯片架构的rf功率管芯中的晶体管布局(同样是场效应晶体管结构)的第二平面视图和第三平面视图;并且

79.图12是在本公开的额外实施方案本公开的中适当并入包含具有倒装芯片架构的至少一个rf功率管芯的pam中的多级功率放大器集成电路的平面视图。

80.为简单和清晰地说明起见,可以省略众所周知的特征和技术的描述和细节,以避免不必要地使后续具体实施方式中描述的本发明的示例和非限制性实施例混淆。应进一步

理解,除非另有说明,否则附图中出现的特征或元件不一定按比例绘制。例如,图中某些元件或区的尺寸可相对于其它元件或区而放大,以提高对本发明实施例的理解。

具体实施方式

81.本公开的实施例在上文简单描述的图式的附图中示出。在不脱离如所附权利要求书所阐述的本发明的范围的情况下,所属领域的技术人员可以设想对示例实施例的各种修改。

82.概要

83.以下描述了具有倒装芯片架构的射频(rf)功率管芯,所述rf功率管芯使得晶体管电流供应端、电流返回端和信号输入(控制)端能够通过前侧输入/输出(i/o)接口互连。此类倒装芯片rf功率管芯非常适合并入功率放大器模块(pam);如本文所出现的术语“功率放大模块”指包含用于功率或信号放大目的的至少一个rf功率管芯的模块化电子组件。当如此并入时,给定的倒装芯片rf功率管芯可以倒置朝向安装到pam的模块基板,例如印刷电路板(pcb)或陶瓷基板,使得rf功率管芯的前侧i/o接口面向模块基板的管芯支撑表面。包含在管芯的前侧i/o接口中的接触垫与模块基板的对应电布线特征之间的电互连可以使用例如焊球或导电柱之类的接触延伸部形成,以避免在至少一些情况下使用引线键合。这可以使pam操作期间的寄生损耗最小化以提高操作效率,尤其是当rf功率管芯在接近或超过3千兆赫的较高频率下操作时。在pam内倒置安装rf功率管芯(或多个rf功率管芯)也可以利用rf功率管芯的后侧用于优化的冷却或热量提取方案。在这方面,可以形成从倒置rf功率管芯的后侧延伸到热接口的低热阻、体积稳固的热量提取路径,所述热接口沿着与模块基板相对的pam的外部主表面暴露。借助此热接口设计,在pam操作期间在rf功率管芯内产生的相对大量的多余热量可以有效的方式传导性地传递到热接口,其中当pam安装在较大的电子组件内时,热接口可能与散热器(例如,金属底盘或散热片结构)热接触。因此提供了一种高效的热管理解决方案以进一步优化rf功率管芯性能。

84.给定的pam可以包含一个或多个rf功率管芯;并且,在某些实施例中,可以包含布置在多尔蒂(doherty)放大器架构中的至少一个峰化rf功率管芯和至少一个载波rf功率管芯。当给定的pam包含多个rf功率管芯时,rf功率管芯中的至少一个(并且可能全部)可以具有如本文所述的倒装芯片架构;例如,在多尔蒂放大器pam的情况下,至少一个或多个载波rf功率管芯(以及可能的峰化rf功率管芯)可以被赋予如本文所述的倒装芯片架构,倾向考虑到载波晶体管集成电路(ic)在给定的管芯操作期间保持导通状态的累积持续时间,载波rf功率管芯承受更大的热负载。尽管多尔蒂放大器拓扑具有优势,但倒装芯片rf功率管芯可集成到除多尔蒂放大器pam之外的各种其它类型的pam中,包括推挽式放大器模块。此外,虽然上述热接口从热性能的角度来看是非常有利的,但本文所述的pam的实施例不需要在所有实施方案中都包括此热接口,尤其是当一个或多个倒装芯片rf功率管芯内有过多热量集中时包含在pam内是没有问题的。最后,虽然利用除引线键合以外的互连技术有利地集成到pam中,但不排除给定的rf功率管芯可以包括通过引线键合与模块基板的对应布线特征电互连的一个或多个端的可能性。

85.无论将给定rf功率管芯集成到哪个特定的pam或其它微电子装置中,倒装芯片rf功率管芯包括具有前侧和相对的后侧的管芯主体以及在管芯主体的前侧上方形成的前侧

层系统。前侧层系统包含多个图案化金属层,在晶片级处理期间在掺杂有源晶体管区之后,所述多个图案化金属层嵌入在管芯主体的前侧上方依次构建或编译的电介质层中。然而,需要强调的是,任何适当数量和类型的晶体管(包括双极晶体管)可以形成在具有本文所述类型的倒装芯片架构的给定rf功率管芯中。独特的晶体管布局和在前侧层系统中形成的互补的图案化金属布线方案(在本文中,称为“图案化布线结构”)使得能够形成前侧i/o接口,所述前侧i/o接口包含到集成到给定rf功率管芯中的一个或多个晶体管的所有端(在本文中通常称为电流供应端、电流返回端,以及信号输入(控制)端)的触点。例如,当场效应晶体管(fet)形成在给定rf功率管芯中时,可产生前侧i/o接口以包括至少一个漏极键合垫、至少一个源极键合垫和至少一个栅极键合垫。漏极、源极和栅极键合垫与对应的布线结构或“分支电极”结构电互连,所述布线结构或“分支电极”结构形成在包含于前侧层系统内的图案化金属层的额外区中。此类分支电极结构包括歧管,细长的指形件或流道从所述歧管延伸以提供与集成到倒装芯片rf功率管芯中的fet(或其它晶体管)的有源区的期望触点。

86.继续前述在给定倒装芯片rf功率管芯中形成fet ic的例子,分支漏极电极结构、分支栅极电极结构和分支源极电极结构可各自包括歧管,例如条形图案化金属主体,多个细长的指形件或流道从所述歧管延伸。在实施例中,栅极和漏极流道可以交错或相互交叉的关系定位,如沿着与管芯主体的前侧正交的竖直轴线或中心线在前侧层系统上向下观察所见。在实施例中,此相互交叉的指形件或流道布局在某些方面可类似于某些常规rf功率晶体管拓扑。然而,在具有常规晶体管布局的rf功率管芯的情况下,接地或电流返回路径(例如,耦合在给定fet的源极区与接地参考电压之间的导电结构)通常在远离前侧层系统的方向上通过管芯主体,到达以其它方式形成在管芯主体的后侧上方的导电层或多层系统(在本文中,称为“背垫金属结构”)。因此,在此常规rf功率管芯设计的上下文中,rf功率管芯的金属化后侧用作管芯的接地(或另一参考电压)触点,所述接地触点电耦合到fet的源极区。作为推论,此常规非倒置rf功率管芯的前侧i/o接口通常仅具有两种键合垫类型(栅极键合垫和漏极键合垫),用于与pam基板的对应布线特征互连。此外,可以利用高电阻基板来制造非倒置rf功率管芯;即,具有体电阻超过每厘米(cm)520欧姆(ω)并且可能接近或超过每厘米1兆欧的包含半导体材料的基板。当这样制造时,rf功率管芯可以包括多个基板通孔(tsv)以提供从fet ic的源极区到形成在管芯主体后侧上的金属层的电连接。此高电阻基板的使用能够实现相对高的功率密度,如在高功率放大器应用的情形下通常所期望的。此类高电阻基板包括高电阻体硅(si)基板、绝缘体上硅(soi)基板、基于金刚石和基于玻璃的基板、层状氮化镓(gan)结构和层状砷化镓(gaas)结构,仅列举几个例子。

87.在促进使用高电阻率管芯结构的同时,在rf功率管芯内包含tsv也与某些限制相关联。tsv的形成通常会增加相当大的成本和制造过程的持续时间。此外,tsv的形成可能会增加rf功率管芯的管芯开裂或其它结构受损的可能性,这可能会降低良品率并且增加平均每个管芯的制造成本。作为另外的缺点,给定rf功率管芯的总体尺寸通常被放大以适应tsv的提供,这需要tsv与掺杂的晶体管区之间的某些最小横向间距。相比之下,本文所述的倒装芯片rf功率管芯可被制造成没有tsv(或者,也许,具有减少的tsv存在)以克服大多数并非全部的前述限制。可以通过消除与tsv的形成相关联的工艺步骤来实现成本节省。此外,通过消除(或减少)tsv,可以减小管芯大小以提供另外的成本节省,同时由于在ic管芯制造期间降低了管芯开裂的可能性而提高了制造良品率。最终结果是,高度紧凑的倒装芯片rf

功率管芯,相对于具有常规非倒装芯片架构的rf功率管芯,提供了具有成本效益的制造和其它益处,例如增强的结构稳固性和增强的隔离特性(如下所述)。此外,如先前所论述的,此类倒装芯片rf功率管芯容易(尽管非本质上)并入具有热接口和/或无引线键合构造的增强pam设计中。最后,此类倒装芯片rf功率管芯可被制造成包括电惰性背垫金属结构,以例如经由键合到金属块或给定pam中包含的其它热延伸部来增强热传导,如下所述;或者,替代地,可以被制造成缺少背垫金属结构以进一步简化成本效益的制造。

88.现将结合图1-12描述具有倒装芯片架构的rf功率管芯以及包含此类倒装芯片rf功率管芯的pam的示例实施例。为了便于解释,以下首先描述具有相对简单构造的rf功率管芯pam;例如,下文结合图2-4论述的示例pam可以各自包含围封在模制模块主体中的单个rf功率管芯(或两个管芯)。然而,如下文结合图12进一步论述的,pam的实施例可以在复杂性上变化,并且可以包含分布在模块基板上的任何实际数目的rf功率管芯和其它微电子部件,包括例如任何数目的表面安装装置(smd)、嵌入式布线结构,或其它ic轴承半导体管芯。此外,替代实施例可以不包括模制管芯包封主体,或者可以相对于下文所述pam因其它方面不同,前提是每个pam包含具有倒装芯片架构的至少一个rf功率管芯。本文所述的倒装芯片rf功率管芯不必在所有情况下并入pam;并且,替代地,可以在需要功率或信号放大的应用或使用中采用,同时以某种方式受益于下文所述的rf功率管芯的使用。

89.具有倒装芯片架构的示例rf功率管芯和包含所述示例rf功率管芯的功率放大器模块

90.图1是如根据本公开的示例实施例所示的具有倒装芯片架构的rf功率管芯20的横截面视图。rf功率管芯20包括具有前侧24和相对的后侧26的管芯主体22。管芯主体22的前侧24和后侧26沿着rf功率管芯20的中心线或竖直轴线间隔开,所述中心线或竖直轴线大体上正交于前侧24延伸并且对应于出现在图1的左下方中的坐标图例28的z轴。包含多个图案化金属层的前侧层系统30通过在前侧24上方的构建而与管芯主体22一体地形成。前侧层系统30可以包括大于一的任何实际数目个图案化金属层,并且将通常包含在沿着竖直轴线(同样,本文中定义为正交于前侧24并且平行于坐标图例28的z轴延伸的轴线)的不同层级或高度处形成的三至五个图案化金属层。例如“上”和“下”之类的相对定位术语在下文被用来描述形成在前侧层系统30内的各种特征。这些术语是相对于与管芯主体22的前侧24的相对接近度来定义的,使得例如,当第二特征位于比第一特征更靠近管芯主体前侧24的位置时,第一特征或元件可以被描述为位于第二特征或元件“上”的水平。类似地,本文档通篇使用术语“上方”来描述沿竖直轴线截取的两个特征或元件之间的相对位置,这些特征或元件之间具有竖直重叠关系。因此,作为例子,前侧层系统30被描述成形成在管芯主体22的前侧24上方,而不管rf功率管芯20在自由空间中的特定朝向。

91.如先前所指示的,包括在前侧层系统30中的图案化金属层的数目将在实施例之间变化。在所示的实施例中,并且作为非限制性例子,前侧层系统30被示意性地描绘为包含五个图案化金属层。按照通用术语,这些图案化金属层可被称为“m1”到“m5”图案化金属层,其中描述符号“m1”指最初形成的图案化金属层,描述符号“m2”指在m1图案化金属层之后形成的图案化金属层,描述符号“m3”指在m2图案化金属层之后形成的图案化金属层,以此类推。此外,根据前述描述,在本文中,m1图案化金属层可被称为“最内部的”或“内部的”图案化金属层,而m5图案化金属层可被称为“最外部的”或“外部的”图案化金属层。所述图案化金属

层被电介质材料层包围,所述电介质材料共同形成通常由图1中的附图标记“34”标识的电介质主体。此类电介质层34还可以包括至少一个外部端电介质层36,其充当焊料掩模或充当钝化层。前侧i/o接口38进一步沿着前侧层系统30(通常称为rf功率管芯20的“前侧”)的外部端表面被提供,并且包括多个键合垫40,这样提供了与集成到rf功率管芯20中的晶体管ic的不同端的电连接,如下文所述。

92.最内部的(m1)金属层被图案化以限定各种金属特征,所述金属特征提供到包括在rf功率管芯20中形成的至少一个晶体管中的有源区42、44、46的触点。当fet ic集成到rf功率管芯20中时,有源晶体管区将通常包括在邻近管芯主体22的前侧24的位置处形成在管芯主体22中的掺杂源极区42和掺杂漏极区46;或,可能取决于所使用的植入物的性质和所需的晶体管拓扑而在前侧24下方掩埋一定量。如本文所示,术语“有源区”还涵盖位于相邻源极区与漏极区42、46之间的半导体材料的区44,并且当给定fet开始导电时晶体管沟道在所述有源区中形成。在替代实施方案中,当一个或多个双极晶体管集成到rf功率管芯20中时,有源晶体管区可以包括发射极区和集电极区。通常,可以说晶体管集成电路48或“晶体管ic 48”形成在rf功率管芯20中。在本公开的实施例中,术语“晶体管ic”用于指示可以将多于一个的晶体管集成到rf功率管芯20中和/或可在rf功率管芯20中形成额外电路元件(例如,阻抗匹配、谐波终止或偏置电路系统)。在以下描述中,出于解释的目的,论述了包含单个fet的晶体管ic(例如,fet ic 48)。在另外的实施例中,其它类型的晶体管(例如,双极晶体管)可以集成到rf功率管芯20中和/或可以提供更复杂的晶体管ic,例如包含形成在单个rf功率管芯上的多个晶体管的多级晶体管ic。另外,本公开的实施例可以与各种不同的管芯技术、晶体管类型和晶体管拓扑一起使用。例如,当由rf功率管芯20承载的一个或多个晶体管采用fet的形式时,可以使用以下任一种管芯技术来实施fet:基于硅的fet(例如,横向扩散金属氧化物半导体fet或ldmos fet)或iii-v族fet(例如,gan fet、gaas fet、磷化镓(gap)fet、磷化铟(inp)fet或锑化铟(insb)fet或其它类型的iii-v族晶体管)。

93.导电布线或布线特征形成在前侧层系统30的图案化金属层中和之间,以提供从外部暴露的键合垫40到包括在m1图案化金属层和fet ic48的有源区42、44、46中的对应图案化特征的电互连。在图1的示意图中以高度简化的形式示出这些图案化金属特征,并且可以根据需要在几何复杂性上变化,以最佳地符合fet ic 48中包括的晶体管(或多个晶体管)的布局。当前侧层系统30包含三个或更多个图案化金属层时,可以采用相对复杂的布线方案或图案化金属层架构。下文结合图5-9更全面地描述此类布线方案的例子,并且因此在本说明书的此节点上将不作深入讨论。然而,在本说明书中的此节点处,可以大体上注意到,包括在键合垫40中的每种类型的键合垫(例如,信号输入键合垫、电流供应键合垫和电流返回键合垫)可以通过分支电极结构电耦合到fet ic 48的对应有源晶体管区;即,包括至少一个导电歧管的导电结构,多个细长导电指形件或滑道从所述歧管延伸。具体地说,并且再次参考fet的例子,包括在键合垫40中的第一类型的键合垫可以通过第一分支电极结构电耦合到包括在m1图案化金属层(例如,覆盖在晶体管ic 48的沟道形成区上的“栅极端”)中或下的对应金属特征。包括在键合垫40中的第二类型的键合垫(例如,一个或多个源极键合垫)可以通过第二分支电极电耦合到包括在m1图案化金属层(例如,提供到fet ic 48的掺杂源极区的触点的“源极端”或“源极金属”)中的金属特征。最后,包括在键合垫40中的第三类型的键合垫(例如,一个或多个漏极键合垫)可以通过第三分支电极电耦合到包括在m1图

案化金属层(例如,提供到fet的掺杂漏极区的欧姆触点的“漏极端”)中的对应金属特征。

94.以上述方式,在前侧层系统30的外部区中形成前侧i/o接口38,以使得当rf功率管芯20集成到例如下文结合图2-4所述类型的pam之类的更大的装置或模块中时能够电连接到fet ic 48。此外,在某些情况下,额外未示出的键合垫可以包括在前侧i/o接口38中以支持与fet ic 48的操作相关联的其它电连接,例如提供电连接的键合垫提供一个或多个fet的栅极或漏极偏置,如下文结合图5和6进一步论述。借助于此晶体管拓扑和集成布线方案实现了若干益处,在实施例中,所述晶体管拓扑和集成布线方案通过前侧i/o接口38共同提供到所有晶体管端的独占式连接。独特的前侧布线结构或拓扑,结合独特的互补晶体管布局,能够提供包括以下各项的此前侧i/o接口:至少一个信号输入或控制触点(例如,在fet的情况下是一个或多个栅极键合垫)、至少一个电流供应触点(例如,在fet情况下是漏极或源极键合垫,取决于fet是n沟道装置还是p沟道装置)以及至少一个电流返回触点(例如,在fet情况下是漏极或源极键合垫,取决于fet是n沟道装置还是p沟道装置)。下文结合图5-11论述此类独特的晶体管拓扑和前侧布线拓扑的例子。然而,首先,更详细地描述rf功率管芯20以提供非限制性上下文,在所述非限制性上下文中可以更好地理解本公开的实施例。

95.继续参考图1,在rf功率管芯20的至少一些实现中,可以在管芯主体22的后侧26上方或上形成后侧金属层或可能多层系统(在本文中,称为“背垫金属结构32”)。当存在时,背垫金属结构32可以由一个或多个所沉积的包含金属的层构成,其在晶片级处理期间方便地电镀或以其它方式形成在后侧26上方。当rf功率管芯20集成到pam中时,提供背垫金属结构32可以增强与一个或多个导热结构的(例如,冶金的)键合和热传递。如图1中箭头52所示,可以从fet ic 48内容易产生多余热量的位置,例如邻近fet ic沟道形成区的位置,到背垫金属结构32形成高效的热传导或“热量提取”路径。虽然为了看得清楚,箭头52从fet ic 48偏移,但箭头52表示的热量提取路径在与前侧i/o接口38相反的方向上从邻近fet ic 48的位置延伸到管芯主体22的后侧26,并且当存在时,穿过背垫金属结构32。可以通过提供此低热阻热量提取路径来增强rf功率管芯20的热性能,特别是当rf功率管芯20具有相对高的功率密度时,并且在没有提供此热量传导路径的情况下,rf功率管芯20内原本可能会出现大幅增加的热量集中。在替代实施例中,还可以通过管芯主体22来提供此类低热阻热传导路径,而从rf功率管芯20省略背垫金属结构32。然而,当提供背垫金属结构32时,由于形成结构32的一种或多种(例如,金属)材料具有相对高的导热性,因此背垫金属结构32可以增强热量提取路径的有效性。另外,当提供背垫金属结构32时,所述背垫金属结构32可以促进在背垫金属结构32与另外包含在主pam实施例中的一个或多个额外导热结构(例如,金属块或其它热延伸部)之间形成低热阻冶金键合,如下文结合图2-4所论述。

96.在rf功率管芯20的某些实施例中,背垫金属结构32可以是电活性的,并且因此用于功率路由或信号传输目的。在这方面,rf功率管芯20的替代实施例可以包含形成在管芯主体22中以将fet ic 48的电活性掺杂区(例如,fet ic 48的源极区)电连接到背垫金属结构32的一个或多个tsv。在此情况下,背垫金属结构32可以用作rf功率管芯20的端或触点以在管芯20安装在较大系统或电路内时使fet ic 48接地。在此类替代实施例中,管芯主体22可以全部或部分由高电阻半导体材料(例如,高电阻si)构成,或可以具有多层(例如,gan或gaas)结构,所述多层结构具有穿过其厚度的高电阻。在rf功率管芯20的又其它实施例中,管芯主体22可能由低电阻材料,例如低电阻体si晶片的单件构成,以使得fet ic 48的掺杂

(例如,源极)区本身在不存在tsv的情况下通过管芯主体22电耦合到背垫金属结构32。尽管存在这些可能性,但是通过以下操作实现了若干益处:将管芯主体22选择为缺少(“不具有”或“没有”)tsv,同时具有穿过其厚度的高电阻率;也就是说,沿着平行于坐标图例28的z轴延伸的竖直轴线截取的高电阻率。在管芯主体22具有高电阻率、无tsv结构的此类实施例中,背垫金属结构32(当存在时)可以是电惰性的,并且因此不用作rf功率管芯20的导电触点。

97.当使用例如体si晶片之类的体半导体晶片的单件来制造rf功率管芯20时,倒装芯片rf功率管芯20的管芯主体22可以全部由单个半导体材料构成。例如,在此情况下,管芯主体22可以由电阻率超过约520ω/cm并且可能接近或超过1兆ω/cm的高电阻率si材料构成。在其它情况下,rf功率管芯20可以使用能够实现相对高的晶体管功率密度的类型的分层管芯技术来制造。此类功率密集型管芯技术的例子是分层gan结构,其中一层或多层gan材料(即,以重量计包含gan作为其主要成分的半导体材料)在例如碳化硅(sic)之类的另一材料的一个或多个基板层上方形成。适合于制造rf功率管芯20的管芯主体22的分层管芯技术的其它例子包括gaas结构,所述gaas结构同样地支持形成具有相对高的功率密度的晶体管ic(例如,fet ic 48)。如在当管芯主体22由高电阻率si(或其它大块半导体)材料构成时的情况下,此类分层管芯技术通常还具有超过520ω/cm的相对高电阻,所述电阻是穿过分层管芯结构的厚度截取的;也就是说,在管芯主体22的情况下,是沿着中心线或平行于坐标图例28的z轴的竖直轴线截取的。

98.在使用高电阻管芯结构制造的常规rf功率管芯设计中,并且通过背垫金属结构(例如,在fet的情况下,背垫金属结构电连接到源极端)提供电接地(电流返回)路径,tsv通常用于在晶体管的相应掺杂(例如,源极)区与背垫金属结构之间提供电连接。如先前所论述的,tsv的形成往往会增加管芯制造过程的复杂性和成本;并且,在一些情况下,可取决于过程参数(例如,热暴露)和其它因素,由于在某些(例如,更薄的)管芯结构的情况下开裂形成或其它结构受损的可能性增加而降低制造良品率。通过利用前侧层系统30内独特的晶体管布局和集成布线策略,如下面更详细地描述的,倒装芯片rf功率管芯20可以被制造成具有无tsv结构(或者,可能,包含减少数目的tsv),以提高制造效率、降低制造成本并且提高良品率,同时提供下文论述的其它性能益处。此外,tsv移除使得rf功率管芯20的总体尺寸减小,从而在晶片级处理期间,在生产rf功率管芯20以及许多类似或相同的rf功率管芯时进一步降低制造成本。

99.rf功率管芯20非常适合以倒置朝向安装在pam内;即,使得前侧i/o接口38朝向pam的下主表面或“底侧”和pam基板的管芯支撑表面,其中至少一个rf功率管芯被安装到所述管芯支撑表面,可能连同任何数目的附加微电子部件一起。此pam设计或构造提供了若干益处,包括实现高效的热接口方案,如上文所提及的,下文将更详细地论述。此外或可替换的是,rf功率管芯20可以倒置朝向安装到pam基板,使得前侧i/o接口38可以与在pam基板的管芯支撑表面处的对应接触垫或布线特征进行物理互连和电互连,而无需使用引线键合(或,可能,减少了对引线键合的依赖)。具体地说,包括在前侧i/o接口38中的键合垫40可以使用焊球、导电柱或其它此类接触延伸部与pam基板的对应布线特征进行电互连和机械互连。此互连接口可以提供增加的结构耐久性;并且,在某些情况下,可以减少在pam中包含的rf功率管芯(或多个rf功率管芯)的高频操作期间由于存在较长的引线键合而另外发生的寄生

铜)过渡液相系统的热传导管芯附接材料。在某些实施例中,导热键合层106可由烧结金属材料构成;即,由烧结金属颗粒形成且主要由一种或多种按重量计的金属成分构成的材料。当由此烧结材料构成时,导热键合层106可主要由按重量计的铜(cu)、银(ag)、金(au)或其混合物构成。并且,在此类情况下,导热键合层106可包含或可不包含有机材料,例如出于强化目的而添加的环氧树脂。如果需要,可以(例如,经由提供图1所示的背垫金属结构32)金属化rf功率管芯20的后侧表面102以在由烧结金属材料构成时与导热键合层106形成稳固的冶金键合。例如,在实施例中,背垫金属层(例如,相对较厚的cu层)可被电镀或以其它方式沉积在rf功率管芯20的后侧表面102上。类似地,在实施例中,热延伸部78的下部表面104同样可以被电镀、粗糙化或以其它方式处理以促进与导热键合层106的键合。

103.热延伸部78可以通过将导电材料沉积到rf功率管芯20的后侧表面102上来制造,例如通过将一层或多层包含金属的材料电镀到管芯后侧表面102上。可替换的是,并且如图1所指示,热延伸部78可以作为预制件或零件提供,其经由导热键合层106定位在rf功率管芯20上方并键合到所述rf功率管芯20上。在实施例中,热延伸部78可采用金属块的形式,所述金属块主要由例如按重量计的cu、au、ag、铝(al)或镍(ni)及其合金之类的金属材料构成。在其它实施例中,热延伸部78可由具有相对较高导热率的复合材料或非金属材料制造。此类材料包括但不限于金刚石聚碳酸酯材料、金刚石金属复合材料(例如,金刚石au、金刚石ag和金刚石cu)、cu石墨、热解石墨、和包含碳的同素异形体的材料,例如石墨烯和碳纳米管填充材料。无论其具体构成如何,理想地选择热延伸部78以具有相对较高的导热率,特别是在竖直方向(平行于坐标图例28的z轴)上,在pam 70的操作期间,沿着所述竖直方向使热量从rf功率管芯20和模块基板74向上传导。因此,在实施例中,如沿着在远离模块基板74的方向上延伸穿过热延伸部78的主要热量提取路径的截面所示,热延伸部78可具有超过100w/mk的导热率,并且可能具有超过200w/mk的导热率。

104.如沿着竖直轴线或中心线轴线(与坐标图例28的z轴相对应)测量并如图2所指示(未按比例绘制),热延伸部78的厚度可大于实施例中rf功率管芯20的厚度。在其它实施例中,热延伸部78的厚度可以小于或基本上等于rf功率管芯20的厚度。如分别沿着坐标图例28的x轴和y轴测量的,热延伸部78的平面尺寸(长度和宽度)可以基本上等于或大于rf功率管芯20的平面尺寸(长度和宽度)。当两个数量相差小于10%时,如本文件中所示,两个数量被视为“基本上相等”。以此方式确定热延伸部78的尺寸扩大了与rf功率管芯20的后侧表面102接触的下部表面104的区域,以促进热流从rf功率管芯20、穿过键合层106并且流向热延伸部78。如图2中进一步所指示的,在实施例中,如沿着延伸穿过pam 70(同样,平行于坐标图例28的z轴)并与热延伸部78和管芯20相交的竖直轴线或中心线截取的,热延伸部78通常可在rf功率管芯20上方居中。在其它实施例中,热延伸部78可以具有相对于rf功率管芯20的不同定位,前提是热延伸部78与rf功率管芯20的后侧表面102热耦合。在许多情况下,热延伸部78将被定位在rf功率管芯20的正上方;例如,热延伸部78可被定位为至少重叠大部分,如果不是,则如沿着竖直轴线或中心线轴线截取的,整个rf功率管芯20延伸穿过热延伸部78和管芯20,并且与rf功率管芯20的后侧表面102正交。在另外的实施例中,可以将多个热延伸部放置在与rf功率管芯20热接触的位置;或者,给定的热延伸部可以实施为从rf功率管芯20的后侧朝向pam 70的顶部表面86延伸,并且可能延伸到pam 70的顶部表面86的多个热通孔(例如,导热柱或杆)。

105.借助于上文所述结构布置,形成从倒置rf功率管芯20的后侧表面102延伸、穿过导热键合层106、穿过热延伸部78并且到达pam 70的热接口72的高导热率、尺寸稳固的热量提取路径。另外,在实施例中,可以从rf功率管芯20的后侧表面102到热接口72绘制沿着主要散热路径的直线,并且所述直线的任何部分都不延伸穿过具有小于30w/mk或可能小于100w/mk的导热率的材料区。在图1中用箭头52表示此类主要热量提取路径,并且提供一个有效的、直接的(非曲折的)、体积上稳固的热传导路径,用于当最终安装有pam 70的较大电子组件内存在pam 70外部的组件级散热器时,将多余热量从rf功率管芯20转移到此类组件级散热器。这可以通过参考图3来进一步理解,其以简化的横截面示出在实施例中可以安装pam 70的电子组件108的一部分;并且,还可以参考图4,其以分解的等距图示出电子组件108的一部分。在这些图式中可以看出,电子组件108包括pam 70安装到其上的例如主板之类的组件级基板110。可以使用例如导电(例如,铜)柱或焊球阵列112之类的任何合适的互连技术,将pam 70的i/o接口电耦合到组件级基板110的上部表面上的对应互连特征(例如,键合垫和迹线)。

106.如先前所指示,可以沉积导电柱、柱或焊球的阵列112;并且,当由焊料构成或具有焊料面漆时,回流以使pam 70与形成在组件级基板110的支撑表面118上的对应接口电互连。图4描绘此类导电布线特征的简化例子,此处呈金属(例如,cu)迹线120和键合垫122的形式。pam 70安放在键合垫122上以提供机械键合并且完成pam 70的端与组件级基板110的布线特征之间的期望电连接。在其它实施例中,可以使用图案化焊料层、平面栅格阵列(lga)、引脚栅格阵列(pga)或不同的球状栅极阵列(bga)将pam 70安装到组件级基板110并将pam70与组件级基板110电互连。所有此类安装接口使得pam 70能够与组件级基板110的对应布线特征进行机械互连和电互连,而无需引线键合,从而提供上文所提及的益处。另外,为了清楚起见,在图3和4中仅示出了组件级基板110的有限部分,各种其它部件可以分布在组件级基板110的示出部分上,可能包括类似于pam 70的其它pam,以形成期望电路结构。

107.如图3和4所示,组件级散热器114可以直接安装到pam 70的顶部表面84、86上,并且使用例如导热键合层116以及例如将散热器114固定在相对于组件级基板110的固定位置的夹具或螺钉等机械结构键合到热接口72上。导热键合层116可以由任何导热键合材料构成,包括热油脂和/或以上结合导热键合层106论述的那些材料;如本文所呈现的术语“导热性”定义为具有超过10w/mk的导热性。在其它实施例中,组件级散热器114可以不太直接的方式热耦合到热接口72。例如,组件级散热器114可以在空间上与pam 70分离,而(例如金属主体或细长散热管之类的)热导管可在散热器114与热接口72之间热耦合。不管其相对于pam 70的特定位置如何,组件级散热器114可以是适于通过热接口72吸收从pam 70提取的多余热量的任何导热结构或装置。例如,在实施例中,组件级散热器114可以是金属底盘、散热片结构(例如,引脚-散热片阵列)或pam 70外部的另一导热主体。组件级散热器114通常会,但不必具有超过热延伸部78的体积。组件级散热器114可以通过向周围环境释放热量来对流冷却;并且,在某些实施例中,散热片可以引导气流朝向组件级散热器114,以促进对流热传递成冲击气流。在实施例中,还可以使用液体冷却剂对组件级散热器114进行有效冷却。一般来说,然后,组件级散热器114可以取决于电子组件108的特性采用不同的形式和配置。还可能将pam 70安装在较大电子系统或组件内,而如果此类布置在某些应用中实现从

pam 70充分散热,则热接口72保持暴露(并且因此不直接与散热器热耦合)。在又其它实例中,pam 70可以缺少任何此类热接口,前提是pam 70包含具有本文所述类型的倒装芯片架构的至少一个rf功率管芯(例如,rf功率管芯20)。

108.已经结合图2-4描述了倒装芯片rf功率管芯可以并入其中的实施例的示例pam。接下来,将结合图5-9更详细地论述支持前侧i/o接口38的形成的示例晶体管布局和集成布线拓扑(如在示例rf功率管芯20的前侧层系统30中形成的)。最初参考图5和6,在本公开的示例实施例中示意性地示出fet拓扑、结构或布局124。在图5和6以及随后的图式中,包含在前侧层系统30中的一种或多种电介质材料(例如,图1中所示的电介质层34)未示出,并且因此隐藏在视线之外。前侧层系统30的电介质层被隐藏以更好地揭示内部导电布线特征,所述内部导电布线特征由前侧层系统30中包括的金属层的图案化限定。示例fet布局124包括包含在rf功率管芯20的前侧i/o接口38中的源极键合垫、栅极键合垫和漏极键合垫。这些键合垫通过图6-9中的附图标记54、56和58来标识,以区分不同的键合垫类型;同时注意到,为了图式之间的相关性,下文所述的键合垫54、56、58通常对应于上文结合图1-4所述的键合垫40。具体地说,如图5-9所标识的,fet布局124包括细长栅极键合垫56、细长漏极键合垫58和两个源极键合垫54(各自称为源极键合垫“54-1”和“54-2”)。各种其它电路元件还可以形成在前侧层系统30中或以其它方式包括在fet ic 48中,所述fet ic 48包括例如偏置电路系统、阻抗匹配电路系统、静电放电电路系统和奇模电阻器。例如,fet布局124可以另外包括栅极偏置触点126,所述栅极偏置触点126经由互连线128电连接到栅极键合垫56的纵向相对的边缘。在另外的实施方案中,除了栅极偏置触点126之外或代替栅极偏置触点126,漏极偏置触点(未示出)也可以并入fet布局124中。

109.fet拓扑布局124沿着对应于坐标图例28的x轴的第一或纵向轴线伸长。栅极键合垫56和漏极键合垫58同样沿着坐标图例28的x轴伸长,基本上平行于彼此延伸,并且沿着垂直于纵向轴线的第二横向轴线(对应于坐标图例28的y轴)间隔开。在栅极键合垫56与漏极键合垫58之间提供包括相互交叉的晶体管阵列130的功率晶体管,如沿着rf功率管芯20的横向轴线(同样,对应于坐标图例28的y轴)所截取的。换句话说,栅极键合垫56和漏极键合垫58沿着横向轴线(y轴)位于相互交叉的晶体管阵列130的相对侧上,并且沿着fet布局124的纵向轴线(x轴)基本上平行于其延伸。相比而言,在所示出的例子中,源极键合垫54沿着fet布局124的纵向轴线(x-轴)间隔开并且定位在相互交叉的晶体管阵列130和栅极键合垫的相对侧上。因此,源极键合垫54-1位于栅极键合垫56和相互交叉的晶体管阵列130的第一侧上,而源极键合垫54-2位于邻近栅极键合垫56和相互交叉的晶体管阵列130的相对的第二侧。为了适应源极键合垫54的这种定位,在使漏极键合垫58的长度沿着纵向轴线(x轴)最大化的同时,相互交叉的晶体管阵列130和栅极键合垫56被赋予小于漏极键合垫58长度的纵向长度(沿着x轴测量的);例如,如图6所示,相互交叉的晶体管阵列130和栅极键合垫56可以沿着x轴具有基本上相等的长度,其范围可为漏极键合垫58长度的约60%至约90%。另外,在本例子中,漏极键合垫58的表面积超过栅极键合垫56的表面积,所述栅极键合垫56的表面积又超过源极键合垫40的累计的表面积。

110.相互交叉的晶体管阵列130包括从纵向细长的漏极歧管134延伸或突出的多个漏极指形件或流道132(标识在图7-10中)。相互交叉的晶体管阵列130还包括从纵向细长的源极歧管138延伸的多个源极指形件或流道136(同样,标识在图7-10中)。漏极流道132和源极

流道136是“相互交叉”或“交错”的,即流道132、136的中间部分和端部分在彼此之间延伸以形成梳状布置,如沿着与rf功率管芯20的外部主表面(平行于坐标图例28的z轴)正交的轴线在晶体管阵列130上向下观察所见。类似地,fet布局124还包括从纵向细长的栅极歧管142延伸的多个栅极指形件或流道140(标识在图7-10中)。与漏极流道132和源极流道136一样,栅极流道140进一步延伸到相互交叉的晶体管阵列130中,如沿着与前侧层系统30的外部主表面正交的轴线在相互交叉的晶体管阵列130上向下观察所见。然而,与漏极流道132和源极流道136大不相同,栅极流道140至少部分地形成在位于漏极流道132和源极流道136下方的位置处的前侧层系统30中,如图8和9中最清楚地示出并且下文将论述的。本文中漏极流道132和漏极歧管134的组合被视为形成分支漏极电极,源极流道136和源极歧管138的组合被视为形成分支源极电极,栅极流道140和栅极歧管142的组合被视为形成分支栅极电极。

111.前进到图7,从自上而下或以平面视角更详细地示出fet布局124的有限区。如图例144所指示,通过对包括在前侧层系统30中的各种金属层进行图案化而形成的特征由不同的交叉影线图案标识。在图案化金属层之间进一步形成通孔或金属塞以在m1、m4、m5图案化金属层中形成的不同特征之间提供各种竖直延伸的电互连,但这在图7中被隐藏。此类通孔或金属塞在图8和9中进一步示出,以横截面透视图示出fet布局124的区,以更清楚地示出fet布局124的三维布线结构。同样,包含在前侧层系统30中的电介质层34(图1)在图7-9中隐藏在视线之外,以更好地揭示fet布局124的内部结构。图7所示的fet布局124的区包括源极歧管138的一部分,源极流道136从所述一部分延伸。如箭头146所指示,源极歧管138的相对端通过互连线148(图6)连接到源极键合垫54-1和54-2,所述互连线148从源极歧管138的相对侧延伸到纵向相对的源极键合垫54。在示出的例子中,如图例144所指示,源极歧管138、源极键合垫54和互连线148被定义成最外部的(m5)图案化金属层的图案化特征。类似地,漏极键合垫58和漏极歧管134同样可以形成为最外部的(m5)图案化金属层的图案化特征,其中漏极歧管134从漏极键合垫58的内侧纵向边缘朝向相互交叉的流道阵列130延伸,如图6中最清楚地示出的。在示出的例子中,栅极键合垫56同样形成在前侧层系统30的最外部的(m5)图案化金属层中。在另外的实施例中,前述金属特征或结构可以形成在前侧层系统30的不同的图案化金属层中;例如,使得歧管134、138形成在相同或不同的中间或下部图案化金属层(例如,m2至m4图案化金属层)中,而键合垫54、56、58形成在最外部的(例如,m5)图案化金属层中。

112.继续参考图6-10,栅极歧管142和栅极流道140形成在一个或多个下部图案化金属层中;此处,为图案化m4层。栅极键合垫56通过在适当的图案化金属层之间形成的竖直连接件(例如,通孔或金属塞)电互连到栅极歧管142;此处,通过在m4图案化金属层与m5图案化金属层之间形成的一个或多个通孔,通常称为“v4”金属通孔。借助于这种结构布置,并且特别是由于在相对于源极歧管138更靠近管芯主体22的前侧24的一个或多个下部图案化金属层内形成栅极歧管142和栅极流道140,所以促进了栅极流道140在源极歧管138下方的布线。在这方面,栅极流道140可以从栅极歧管142延伸(其一部分还可以在源极歧管138下方延伸),并且在栅极流道140延伸到横向邻近漏极流道132的位置时在源极歧管138下方通过以形成相互交叉的流道阵列130。此外,在沿着fet布局124的横向轴线(对应于坐标图例28的y轴)在源极歧管138下方且跨越源极歧管138延伸时,栅极流道140通过竖直偏移或间隙

(填充有电介质)与源极歧管138竖直地间隔开,以提供所需的电隔离。这实际上形成了交叉结构或拓扑,以实现与fet ic 48的源极区和栅极区的电接触,而没有源极电流和栅极电流的不期望的桥接或交叉耦合。

113.通过参考图9,可以更充分地理解上述交叉拓扑,图9还包括标识横截面中所示的图案化金属层的部分的图例150。在此图式中可以看出,栅极键合垫56(形成在图案化m5层中)通过在m4层与m5层之间延伸的一个或多个(例如,条形)通孔或金属塞153电耦合到栅极歧管142(形成在图案化m4层中)。同时,在栅极键合垫56(在示出的例子中,形成在图案化m5层中)与源极歧管138(也形成在图案化m5层中)之间提供横向隔离间隙154,以在这些结构之间提供所需的电隔离。类似地,如图8和9所示,漏极流道132从漏极歧管134朝向源极歧管138延伸,同时在到达源极歧管138之前终止。因此,如图8中箭头156所指示,在此接口处形成额外的隔离间隙,以在漏极流道132与源极歧管138之间提供适当的电隔离。最后,源极流道136同样从源极歧管138朝向漏极歧管134和漏极键合垫58延伸,同时在到达漏极歧管134之前终止,以在这些结构之间提供期望的电隔离。在另外的实施例中,可以制造前侧层系统30以按另一种方式提供与fet ic 48的期望互连;例如,导电源极结构可以形成在下部图案化金属层(即,更靠近管芯主体22的前侧24的金属层)中以在导电漏极结构下方延伸。因此,在实施例中,可以形成fet布局124,使得栅极流道140在源极歧管138下方或上方穿过,从栅极歧管142延伸到覆盖在晶体管的有源区上的位置。

114.如上所述,在示出的例子中,源极流道136(此处,形成在图案化m5层中)和漏极流道132(同样形成在图案化m5层中)相互交叉或交错以形成相互交叉的晶体管阵列130。在示例拓扑中,如沿着fet布局124的纵向轴线(对应于坐标图例28的x轴)所截取的,每个漏极流道132可以安置在两个邻近的源极流道136之间。然后沿着fet布局124的纵向轴线(x轴)重复此结构图案以形成相互交叉的晶体管阵列130,如先前所述。尽管在示出的例子中形成在下部图案化金属层(此处,为图案化m4层)中,栅极流道140类似地安置在横向邻近的源极流道136对之间,如沿着竖直轴线或rf功率管芯20的中心线(与对应于坐标图例28的z轴的管芯主体22的前侧24正交)在前侧层系统30上向下观察所见。沿着坐标图例28的x轴从左到右前进(栅极键合垫56、栅极歧管142、源极歧管138、漏极键合垫58和漏极歧管134沿着所述x轴平行延伸),遇到第一源极流道136,接着是漏极流道132,接着是第二源极流道136,接着是栅极流道140,然后沿着fet和相互交叉的晶体管阵列130的长度重复此图案。在其它实施方案中,可以提供不同的fet布局,其中本实施例提供一个合适的例子。

115.通过在前侧层系统30的最内部的(m1)图案化金属层中形成的多个图案化金属特征向fet的各个有源区(包括在图1所示的有源晶体管区42、44、46中)提供电接触。例如,如图8和9最佳所示,各种图案化金属区或特征44-1可以接触fet的漏极区和源极区(通常称为“漏极触点”和“源极金属”)。通过导电通孔、金属塞或类似互连结构(在图8和9中通常标记为“158”)在源极金属特征44-1与源极流道136之间提供电互连。此类通孔或塞158形成在中间(m2-m4)图案化金属层之间,并且从源极流道136的底侧竖直地延伸,以提供到形成在图案化m1层中的源极金属特征44-1的各种图案化区的电连接。类似地,导电通孔或竖直塞160在中间(m2-m4)图案化金属层之间形成,以将漏极流道132电连接到图案化m1层的对应图案化区44-2,所述对应图案化区44-2接触fet的掺杂漏极区。最后,如图9所标记的,在图案化金属层之间同样提供导电通孔或竖直塞162,以将栅极流道140电连接到m1金属层的适当图

案化区44-3和覆盖在沟道区上的栅极触点。以此方式,在前侧层系统30中形成的图案化金属特征和导电通孔完成fet结构,所述fet结构提供fet ic的栅极端、源极端和漏极端到对应的键合垫(栅极键合垫56,源极键合垫54,以及漏极键合垫58)之间的电互连,所述对应的键合垫可沿着rf功率管芯20的前侧i/o接口38互连。

116.因此,已经提供了具有倒装芯片架构的rf功率管芯(例如,rf功率管芯20)。rf功率管芯20的倒装芯片架构通过提供前侧i/o接口(例如,前侧i/o接口38)、修改的晶体管布局或拓扑(例如,fet布局124)和独特的前侧层系统布线方案来实现,如先前所论述的。在rf功率管芯20包含fet ic的上述例子中,在前侧层30中形成的布线或布线拓扑包括形成分支源极电极(例如,源极歧管138和源极流道136),从而在至少一个前侧源极键合垫(例如,源极键合垫40)和fet ic的掺杂源极区之间提供前侧电连接。因此,前侧层系统还可以包含至少一个分支漏极电极(例如,漏极歧管134和漏极流道132)和至少一个分支栅极电极(例如,栅极歧管142和栅极流道140)以分别提供栅极键合垫56之间的电互连和漏极键合垫58之间的电互连以及fet的对应有源区。通过经由i/o接口38提供所有晶体管i/o连接,rf功率管芯20可被制造成缺少tsv以允许降低制造成本、缩小管芯尺寸并且降低对管芯开裂的敏感性。此外,由于源极流道136相对于漏极流道132和栅极流道140的定位,可以提供额外的隔离或屏蔽以提高rf功率管芯性能。在另外的实施例中,rf功率管芯20可以实现此类益处,同时并入在不同方面相对于fet布局124不同的其它fet布局。为了进一步强调这一点,现在将结合图10和11描述适合并入具有倒装芯片架构的rf功率管芯中的两种替代fet布局的额外描述。

117.支持倒装芯片架构的额外示例fet布局

118.现在转向图10和11,呈现了fet拓扑、结构或布局164、166的额外示例实施例。fet布局164、166非常适合集成到倒装芯片rf功率管芯(例如,图1中所示的rf功率管芯20)中,并且支持与前侧i/o接口38类似或相同的前侧i/o接口。寻址图10所示的第一fet布局164,所述fet布局164形成在半导体材料170的主体中并且在其上方,所述半导体材料170可以形成具有前侧168(对应于图1所示的管芯主体22的前侧24)的管芯主体的一部分或全部。如先前所述,掺杂半导体材料170的某些区以限定fet布局164的源极区和漏极区;例如,如在其中形成fet布局164的沟道的半导体区的主表面上向下观察所见,每个源极区位于两个漏极区之间,其中两个沟道区(并且覆盖在栅极结构上)位于源极区和两个漏极区之间。以类似于上文结合图5-9所述的fet布局124的方式,fet布局164的i/o接口包括细长漏极键合垫172、细长栅极键合垫174和两个源极键合垫176-1、176-2。此外,在示出的例子中,栅极偏置键合垫178还设置在前侧i/o接口中。漏极键合垫172电耦合到分支漏极电极,所述分支漏极电极包括漏极歧管180,多个细长漏极指形件或流道从所述漏极歧管180延伸。类似地,源极键合垫176电连接到源极歧管182的相对端,所述源极歧管182以类似于先前所述的方式平行于漏极歧管180延伸。多个源极流道从源极歧管182延伸并且与漏极流道协作以形成相互交叉的晶体管阵列184。最后,栅极键合垫174电耦合到底层栅极歧管186,栅极流道从所述底层栅极歧管186延伸,其中栅极流道形成在图案化金属层下方的一个或多个图案化金属层(例如,m3或m4层)中,其中源极歧管182形成在所述图案化金属层(例如,m5层)中,以允许栅极流道以先前所述的方式在源极歧管182下方延伸并进入相互交叉的晶体管阵列184中。

119.类似地,在图11的例子中,呈现了支持与前侧i/o接口38类似或相同的前侧i/o接口的另一可能的fet布局166。同样,fet布局166包括前侧i/o接口,所述前侧i/o接口包含细

长漏极键合垫188、细长漏极歧管190、细长源极歧管192、细长栅极歧管194和栅极偏置键合垫196。漏极流道从漏极歧管190(统称为“分支漏极电极”)延伸,源极流道从源极歧管192(统称为“分支源极电极”)延伸,栅极流道从栅极歧管194(统称为“分支栅极电极”)延伸以产生相互交叉的晶体管阵列198。然而,与fet布局164大不相同,fet布局166包含多个栅极键合垫200(每个栅极键合垫电耦合到栅极歧管194)和多个源极键合垫202(每个源极键合垫电耦合到源极歧管192)。栅极键合垫200和源极键合垫202沿着fet布局166的纵向轴线以交替图案或关系相互交叉或交错。在其它实施方案中,源极键合垫202可以替代地以类似方式与漏极键合垫188交错,其中漏极键合垫188以类似于栅极键合垫200的方式沿着其长度被划分为若干离散部分或区;或者,作为另外的可能性,源极键合垫202可以与多个栅极键合垫和多个漏极键合垫以类似于图11中所示的交替关系交错。因此,集成到此fet布局或拓扑中的rf功率管芯可以被描述为包含以下各项中的至少一个:(i)以交替关系与多个栅极键合垫交错的多个源极键合垫;和/或(ii)同样以交替关系与多个栅极键合垫交错的多个漏极键合垫。

120.上述导电特征或“晶体管布线结构”可以通过对包括在前侧层系统204中的金属层进行图案化来形成,所述前侧层系统204形成在半导体材料208主体的前侧或上部主表面206上。在沉积图案化金属层和电介质层之前,以类似于先前所述的方式掺杂半导体材料主体208的适当区域以限定fet结构166的源极区和漏极区。与fet布局124(图5-9)和fet布局164(图10)进行比较,fet布局166非常适合并入更大的管芯中,并且由于源极键合垫202沿着源极歧管的长度接近源极歧管192,因此可以减少源极电感。由于减少了电感和电阻损耗,fet布局166可有益地用于更高频率的应用中。相反地,相对于fet布局166,fet布局124、164可能非常适合在低频应用中使用,并且由于栅极键合垫的相对较大的尺寸而更容易制造,这也可以增强晶体管的载流能力。在每个示例fet布局中,实现相对紧凑的fet布局,从而支持以先前所述的方式形成前侧i/o接口。

121.包含至少一个倒装芯片rf功率管芯的pam的替代实施例

122.在结合图2-4论述的上述示例实施例中,pam 70采用相对简单的形式并且包含单个所示的rf功率管芯(rf功率管芯20)。在另外的实施例中,根据本发明教示制造的pam可能相当复杂,前提是pam包括至少一个rf功率管芯和热接口,通过所述热接口可以提取由管芯(和pam内的任何数目的其它微电子部件)产生的热量。例如,在某些实施例中,pam 70可以包含在多尔蒂功率放大器ic中使用的峰化放大器管芯和载波放大器管芯两者,所述多尔蒂功率放大器ic附接到放大器模块基板。另外,峰化放大器管芯和载波放大器管芯中的任一者或两者可包含单级放大器,如先前所述,或多级放大器。在又其它的实例中,多晶体管放大器级和各种其它电路系统可以形成在单个rf功率管芯上。进一步强调这一点,图12是双级功率放大器ic 212的俯视图或平面图,所述双级功率放大器ic 212形成在单个rf功率管芯上并且适于集成到本文所述类型的pam中。在此例子中,双级功率放大器ic 212包括初级或预放大器晶体管级214、次级或末级放大器晶体管级216和各种其它电子部件(为了清楚起见,仅标记了其中的一些),例如并联电容器和偏置电路系统。一个或多个热延伸部(在图12中隐藏在视线之外,但通常由虚线222表示)先前已键合到包括晶体管级214、216的双级功率放大器ic 212的后侧。在所示例子中,具体地说,单个热延伸部222被示出为定位在包括在初级晶体管级214上方;例如,此晶体管级214可能特别容易产生和积聚多余热量,因

此,目标是通过热延伸部222增强排热。

123.为了将双级功率放大器ic 212集成到具有前侧热接口的pam中,可以在双级功率放大器ic 212的适当端或触点上方沉积各种触点延伸部226(例如焊料凸点或焊球);仅举几个例子,例如第二级漏极键合垫、第一级和第二级源极键合垫、第一级栅极键合垫、栅极偏置垫和漏极偏置垫,以及并联电容器。关于并联电容器,具体地说,当承载双级功率放大器ic 212的rf功率管芯集成到pam中并且最终安装在较大电子系统或组件中时,最上面的金属端或“顶板”可以经由此类触点延伸部226连接到接地。在组装期间,承载双级功率放大器ic 212的rf功率管芯可以倒置并且与例如pcb之类的模块基板安装(进行物理互连和电互连)。在至少一些实例中,所得组件可以进行包覆成型以形成具有过厚且完全覆盖热延伸部222的模制模块主体。模制模块主体随后可以藉由背面研磨而变薄,以从pam顶部表面露出热延伸部222的上部表面。最后,然后可以根据需要执行任何额外步骤以完成所得pam的制造。

124.结论

125.因此,提供了具有倒装芯片架构的rf功率管芯和包含倒装芯片rf功率管芯的pam。在给定pam中,至少一个rf功率管芯以倒置朝向安装到模块基板,使得rf功率管芯的前侧面向基板的管芯支撑表面。通过rf功率管芯安装到的模块基板以及与任何数目的额外部件可以竖直地将电信号路由到rf功率管芯并且向所述rf功率管芯供电。此外,某些实施例,pam可以通过pam的顶部表面有效地从由pam中包含的至少一个rf功率管芯产生的多余热量中进行提取。更一般地,提供了具有倒装芯片架构和独特的前侧i/o接口的rf功率管芯的实施例。倒装芯片rf功率管芯的实施例有益地(尽管非本质上)被制造成缺少tsv以降低制造成本和复杂性、减小管芯尺寸并提供增加的结构稳固性。

126.在实施例中,pam包括模块基板,所述模块基板具有管芯支撑表面和暴露于所述管芯支撑表面处的多个导电触点。第一rf功率管芯以倒置朝向安装到模块基板的管芯支撑表面。所述第一rf功率管芯又包括具有前侧和相对的后侧的管芯主体、具有形成在所述管芯主体中的有源区的晶体管,以及形成在管芯主体的前侧上方的前侧层系统。所述前侧层系统包含限定电耦合到所述晶体管的所述有源区的第一、第二和第三分支电极结构的图案化金属层。前侧i/o接口形成在所述前侧层系统的外部端部分中,其中所述前侧i/o接口包含第一、第二和第三键合垫。所述第一、第二和第三键合垫分别电耦合到第一、第二和第三分支电极结构,而所述第三键合垫另外电耦合到模块基板的多个导电触点。

127.在另外的实施例中,pam包括具有管芯支撑表面的模块基板,以及以倒置朝向安装到模块基板的管芯支撑表面的rf功率管芯,其中rf功率管芯的接触表面朝向管芯支撑表面。所述rf功率管芯包括具有前侧和相对的后侧的管芯主体。前侧层系统形成在管芯主体的前侧上方,并且限定rf功率管芯的接触表面。形成在管芯主体和前侧层系统中的fet,包括分支漏极电极结构、分支栅极电极结构和分支源极电极结构。前侧i/o接口另外形成在前侧层系统的外部端部分中。前侧i/o接口包括分别电耦合到分支漏极电极结构、分支栅极电极结构和分支源极电极结构的第一漏极键合垫、第一栅极键合垫和第一源极键合垫。

128.如本文进一步公开的,rf功率管芯的实施例包括具有前侧和相对的后侧的管芯主体、形成在管芯主体前侧上方的前侧层系统以及形成在管芯主体和前侧层系统中的fet。fet包括分支漏极电极结构、分支栅极电极结构和分支源极电极结构。另外形成在前侧层系

统的外部端部分中的前侧i/o接口包括电耦合到分支漏极电极结构的第一漏极键合垫、电耦合到分支栅极电极结构的第一栅极键合垫和电耦合到分支源极电极结构的第一源极键合垫。

129.尽管在前述具体实施方式中已经呈现了至少一个示例实施例,但应了解,存在大量变化形式。还应了解,一个或多个示例实施例仅仅是例子,且并不意图以任何方式限制本发明的范围、适用性或配置。实际上,前述具体实施方式将向本领域的技术人员提供用于实施本发明的示例实施例的便利指南,应理解,可在不脱离如所附权利要求书中阐述的本发明的范围的情况下对示例实施例中描述的元件的功能和布置作出各种改变。已经根据在前述实施方式的过程中引入某些元件(例如,封装引线、晶体管和晶体管承载管芯)的次序来使用例如“第一”、“第二”、“第三”等数字标识符。此类数字标识符还可以用于后续权利要求书中以指示权利要求书中的引入次序。因此,此类数字标识符可在具体实施方式与后续权利要求之间变化以反映元件的引入次序的差异。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。