一种抗emi的超结vdmos器件及制备方法

技术领域

1.本发明涉及半导体器件技术领域,特别涉及一种抗emi的超结vdmos器件及制备方法。

背景技术:

2.本部分的陈述仅仅是提供了与本发明相关的背景技术,并不必然构成现有技术。

3.超结mosfet器件广泛应用于开关电源、汽车电子、马达驱动等各种领域。它利用电荷补偿理论,漂移区由一系列交替的高掺杂p柱与n柱组成,利用p柱与n柱横向电场互相耗尽,从而提升漂移区浓度,降低导通电阻。

4.但是,超结mosfet的p柱与n柱的掺杂总量需要相同或相当,若二者失配严重,会造成耐压大幅降低,对加工工艺提出了挑战。此外,超结mosfet由于n柱与p柱互相耗尽,开关速度快,开关过程中会面对很高的漏极和源极之间的电压震荡dv/dt和电流震荡di/dt,一方面高的电压震荡dv/dt叠加在器件上,容易造成寄生三极管开启,导致器件失效;另一方面高的电压震荡dv/dt叠加在开关系统中,造成极大的电磁干扰,从而对周围的元器件和设备产生严重的电磁污染。

技术实现要素:

5.为了解决现有技术的不足,本发明提供了一种抗emi的超结vdmos器件及制备方法,通过引入复合介质层,提高了超结mosfet击穿电压,增强了器件的抗emi(electromagnetic interference,电磁干扰)震荡能力。

6.为了实现上述目的,本发明采用如下技术方案:

7.本发明第一方面提供了一种抗emi的超结vdmos器件。

8.一种抗emi的超结vdmos器件,包括:

9.第一导电类型的衬底;

10.衬底下侧的漏极金属,衬底上方的超结漂移区;

11.位于超结漂移区内且贯穿整个超结漂移区的复合介质层,复合介质层包括:外围氧化层介质、外围氧化层介质内的u型sipos层以及u型sipos内的氧化层介质;

12.u型sipos上侧的源极金属;

13.超结漂移区上侧掺杂形成的左右两处第二导电类型的基区;

14.基区上侧的掺杂形成的第一导电类型的源区和第二导电类型的欧姆接触区;

15.源区和欧姆接触区上侧的源极金属;

16.基区上侧的栅氧化层;

17.栅氧化层上侧的栅极金属,栅极金属与源极金属通过氧化层隔开。

18.进一步的,超结漂移区包括第一导电类型漂移区和第二导电类型漂移区,第一导电类型漂移区的下侧与衬底的上侧连接,第一导电类型漂移区的上侧与栅氧化层的下侧连接;

19.第二导电类型漂移区的下侧与衬底的上侧连接,第二导电类型漂移区的上侧与第二导电类型基区的下侧连接。

20.进一步的,第二导电类型欧姆接触区和第一导电类型源区设置在第二导电类型基区内部。

21.进一步的,外围氧化层介质的厚度范围为0.05μm~2μm。

22.进一步的,u型sipos层的厚度范围为0.1μm~5μm。

23.进一步的,u型sipos层的掺氧比例范围为10%~40%。

24.进一步的,第二导电类型漂移区的杂质总量小于或等于第一导电类型漂移区的杂质总量,第二导电类型漂移区的杂质总量与第一导电类型漂移区的杂质总量的比例范围为0.2~1。

25.进一步的,超结漂移区的n柱与p柱的宽度和掺杂浓度满足电荷平衡条件。

26.进一步的,器件所用半导体材料为体硅、碳化硅、砷化镓、磷化铟或锗硅。

27.本发明第二方面提供了一种抗emi的超结vdmos器件的制备方法,包括以下过程:

28.取第一导电类型的半导体衬底材料;

29.在衬底材料上外延形成超结结构的漂移区;

30.在超结漂移区内刻蚀沟槽,沟槽贯穿整个超结漂移区至第一导电类型衬底;

31.在沟槽侧壁生长氧化层介质;

32.在沟槽内淀积形成u型半绝缘多晶硅层;

33.在u型半绝缘多晶硅层内淀积氧化层介质;

34.在漂移区上方生长栅氧化层;

35.在栅氧化层上方淀积多晶硅栅极;

36.在漂移区上部离子注入并推结形成基区;

37.在基区上掺杂形成第一导电类型的源区和第二导电类型的欧姆接触区;

38.淀积中间氧化层介质;

39.淀积源极金属;

40.减薄衬底,并背金,形成漏极。

41.与现有技术相比,本发明的有益效果是:

42.1、本发明提供的具有复合介质层的抗emi的超结vdmos器件及制备方法,在超结漂移区中引入复合介质层,复合介质层由sio

2-sipos-sio2层组成,u型sipos两端直接连接器件的源极与漏极,在器件阻断状态下,sipos作为体内场板,辅助耗尽超结漂移区,从而提高了器件击穿电压。

43.2、本发明提供的具有复合介质层的抗emi的超结vdmos器件及制备方法,u型sipos连接源极和漏极,直接增大了输出电容coss,有效地降低了器件的开关震荡,提高了dv/dt耐量,降低了开关电路中的emi电磁辐射噪声。

44.3、本发明提供的具有复合介质层的抗emi的超结vdmos器件及制备方法,sipos上方的源极,屏蔽栅极信号,降低了反向传输电容crss,提高了器件开关速度,降低了器件开关损耗。

附图说明

45.构成本发明的一部分的说明书附图用来提供对本发明的进一步理解,本发明的示意性实施例及其说明用于解释本发明,并不构成对本发明的不当限定。

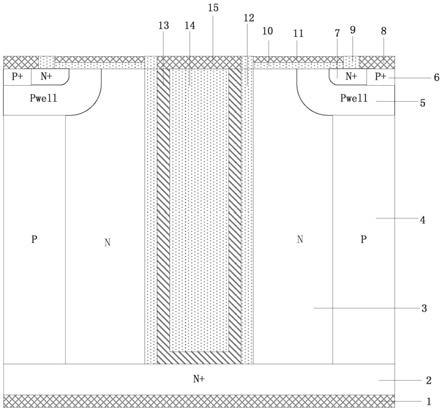

46.图1为本发明实施例1提供的具有复合介质层的抗emi的超结vdmos器件的结构示意图。

47.1、漏极金属;2、第一导电类型的衬底;3、第一导电类型漂移区;4、第二导电类型漂移区;5、第二导电类型的基区;6、第二导电类型的重掺杂欧姆接触区;7、第一导电类型源区;8、源极金属;9、氧化层介质;10、栅氧化层;11、栅极;12、氧化层介质;13、u型sipos;14、氧化层介质;15、源极金属。

具体实施方式

48.下面结合附图与实施例对本发明作进一步说明。

49.应该指出,以下详细说明都是例示性的,旨在对本发明提供进一步的说明。除非另有指明,本文使用的所有技术和科学术语具有与本发明所属技术领域的普通技术人员通常理解的相同含义。

50.需要注意的是,这里所使用的术语仅是为了描述具体实施方式,而非意图限制根据本发明的示例性实施方式。如在这里所使用的,除非上下文另外明确指出,否则单数形式也意图包括复数形式,此外,还应当理解的是,当在本说明书中使用术语“包含”和/或“包括”时,其指明存在特征、步骤、操作、器件、组件和/或它们的组合。

51.在不冲突的情况下,本发明中的实施例及实施例中的特征可以相互组合。

52.实施例1:

53.如图1所示,本发明实施例1提供了一种抗emi的超结vdmos器件,包括:

54.漏极金属1;

55.位于漏极金属1上方的第一导电类型的衬底2;

56.位于第一导电类型衬底2上方的超结漂移区,超结漂移区包括第一导电类型漂移区3和第二导电类型漂移区4;

57.位于超结漂移区上部的第二导电类型基区5;

58.位于第二导电类型基区5内部的第二导电类型欧姆接触区6和第一导电类型源区7;

59.位于第二导电类型基区5上方的栅氧化层10;

60.位于栅氧化层10上方的栅极11;

61.位于第二导电类型欧姆接触区6上方的源极金属8,源极金属8与栅极11被氧化层介质9隔开;

62.位于超结漂移区中间的复合介质层,包括外围的氧化层介质12(可以是sio2层),位于氧化层介质内的u型sipos层13,位于u型sipos层内部的氧化层介质14(可以是sio2层),位于氧化层介质14上方的源极金属15。

63.其中,u型sipos层13底部直接与第一导电类型衬底2相接,顶部直接与源极金属15相接。

64.可选的,本实施例中,复合介质层外围的氧化层介质12厚度为0.05μm~2μm,本领

域技术人员可以根据具体工况在此范围内进行选择,这里不再赘述。

65.可选的,本实施例中,u型sipos层13的厚度为0.1μm~5μm,u型sipos层13的掺氧比例为10%~40%,本领域技术人员可以根据具体工况在上述范围内进行选择,这里不再赘述。

66.可选的,本实施例中,第二导电类型漂移区4杂质总量不大于第一导电类型漂移区3杂质总量,第二导电类型漂移区4杂质总量与第一导电类型漂移区3杂质总量的比例根据器件特性和工艺条件确定,典型范围为1/5~1/1之间,本领域技术人员可以根据具体工况在上述范围内进行选择,这里不再赘述。

67.本实施例所述的抗emi的超结vdmos器件中涉及的半导体可采用体硅、碳化硅、砷化镓、磷化铟或锗硅等半导体材料制作,本领域技术人员可以根据具体工况进行选择,这里不再赘述。

68.实施例2:

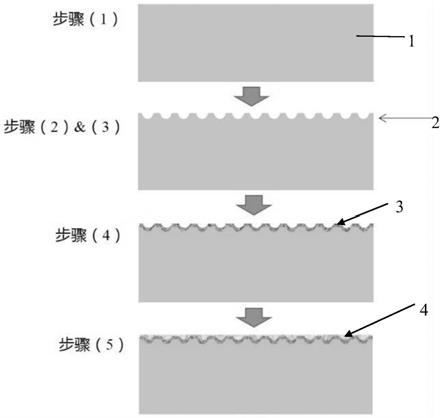

69.本发明实施例2提供了一种抗emi的超结vdmos器件的制备方法,包括以下过程:

70.取第一导电类型的半导体衬底材料;

71.在衬底材料上外延形成超结结构的漂移区;

72.在超结漂移区内刻蚀沟槽,沟槽贯穿整个超结漂移区至第一导电类型衬底;

73.在沟槽侧壁生长氧化层介质;

74.在沟槽内淀积形成u型半绝缘多晶硅层;

75.在u型半绝缘多晶硅层内淀积氧化层介质;

76.在漂移区上方生长栅氧化层;

77.在栅氧化层上方淀积多晶硅栅极;

78.在漂移区上部离子注入并推结形成基区;

79.在基区上掺杂形成第一导电类型的源区和第二导电类型的欧姆接触区;

80.淀积中间氧化层介质;

81.淀积源极金属;

82.减薄衬底,并背金,形成漏极。

83.以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。