半导体装置、otp读出电路以及otp电路

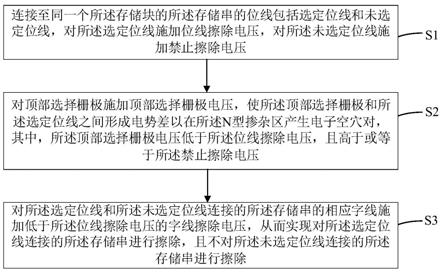

技术领域

1.本发明的实施方式涉及半导体装置、otp读出电路以及otp电路。

背景技术:

2.在具备具有otp(一次可编程)单元(cell)的otp电路的lsi(大规模集成电路)中,当接通电源而电源电压成为基准电压源的基准电压时,用于复位电源接通的复位解除信号被输出到控制电路。控制电路根据复位解除信号进行动作,otp电路也根据复位解除信号进行动作。控制电路将数据编程到otp单元中,并从otp单元读出数据,将读出的数据作为修整信息来输出。

3.现有技术文献

4.专利文献

5.专利文献1:日本特开2005-195746号公报

技术实现要素:

6.发明要解决的课题

7.但是,由于基准电压源的基准电压有偏差,例如,如果不成为上限值2.1v,则复位解除信号就不会输出到控制电路和otp电路。因此,即使otp单元的读出电压例如为1.8v,复位也不会被解除,因此无法从otp单元读出数据。

8.本实施方式提供一种能够自行(self)地读出存储元件的数据的半导体装置、otp读出电路以及otp电路。

9.用于解决课题的手段

10.根据本实施方式的一方式,半导体装置具备:第1存储元件,存储数据;以及可读出信号输出部,具备由与所述第1存储元件相同的结构构成的第2存储元件,该可读出信号输出部基于所述第2存储元件的状态判断为可读出所述第1存储元件的所述数据,并输出可读出信号。

11.根据本实施方式的一方式,具备将数据仅能够编程一次的第1otp单元;以及流过恒定电流的恒流源,所述第1otp单元具有:第1晶体管,第1栅极上从所述恒流源被供给电流,第1源极经由第1电阻被接地;以及存储晶体管,第2栅极上从所述恒流源被供给电流,第2源极被接地,所述第1晶体管和所述存储晶体管构成电流镜电路,通过所述恒流源而使电流流过,并使所述存储晶体管的栅极-源极间电压vth1和所述第1晶体管的栅极-源极间电压vth2逐渐上升,在表示数据编程前后的电流量的变动率的编程倍率成为最大的电压下,读出在使用vth1和vth2的差分在所述第1晶体管中流过电流后被编程在所述存储晶体管中的数据。

12.发明效果

13.根据本实施方式,能够自行地读出存储元件的数据。

附图说明

14.图1是表示具备实施方式的otp电路的lsi的基本结构的图。

15.图2是表示具备第1实施方式的otp读出电路的lsi的图。

16.图3是第1实施方式的otp读出电路所具有的otp电路的概略结构图。

17.图4是第1实施方式的otp读出电路所具有的读出完成电压输出部的概略结构图。

18.图5是图3所示的otp电路的具体的电路结构图。

19.图6是图4所示的读出完成电压输出部的具体的电路结构图。

20.图7是说明图3所示的otp电路的具体的电路的数据读出时的动作的图。

21.图8是说明图3所示的otp电路的具体的电路的对数据进行编程时的动作的图。

22.图9是表示在第2实施方式的otp读出电路中,在图5所示的otp电路内设置了偏置电路的情况下能够精确地设定读取条件的情形的图。

23.图10是表示在图5所示的otp电路内不设置偏置电路的情况下读取条件扩大的情形的图。

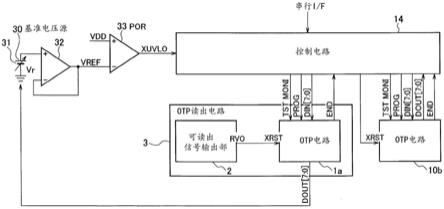

具体实施方式

24.以下,一边参照附图,一边详细地说明实施方式的半导体装置、otp读出电路。另外,所参照的附图是示意图。在以下的说明中,对具有相同功能及结构的要素标注共同的参照标号。

25.(第1实施方式)

26.实施方式的半导体装置具备:存储数据的第1存储元件;以及可读出信号输出部,具备由与第1存储元件相同的结构构成的第2存储元件,该可读出信号输出部基于第2存储元件的状态判断为可读出第1存储元件的数据,并输出可读出信号。第1存储元件以及第2存储元件分别是非易失性存储器,例如是由存储单元构成的otp单元、prom(可编程rom(programmable rom))、eprom(可擦除可编程rom(erasable programmable rom))、eeprom(电可擦除可编程rom(electrically erasable programmable rom))、闪存等。

27.根据实施方式的半导体装置,可读出信号输出部基于第2存储元件的状态而判断为可读出第1存储元件的数据,并输出可读出信号。因此,能够自行地读出第1存储元件的数据。

28.以下,针对在半导体装置的第1存储元件以及第2存储元件为otp单元的情况下,具备otp单元的otp电路及读出被存储在otp单元中的数据的otp读出电路进行说明。图1表示具有实施方式的otp电路的lsi的基本结构。该lsi具备由可变电源31和运算放大器32构成的基准电压源30、上电复位(power on reset)电路(por电路)33、控制电路14、与控制电路14连接的otp电路10a、10b。

29.otp电路10a、10b分别具有多个otp单元,各个otp单元能够将1比特(bit)的数据进行编程(写入),并能够读出数据。otp电路10a、10b例如由8比特数据构成。

30.基准电压源30将基准电压输出到por电路33的反相输入端子(-)。por电路33由比较器构成,对被输入到同相输入端子(开关)的电压vdd和被输入到反相输入端子的基准电压vref进行比较,在电压vdd成为基准电压时,将复位解除信号xuvlo输出到控制电路14。

31.控制电路14由数字电路构成,通过复位解除信号启动,并且将复位解除信号输出

到otp电路10a、10b。otp电路10a、10b根据复位解除信号而动作。控制电路14能够将数据编程(prog)到otp电路10a、10b内的otp单元中,并且,将输入信号(din)作为输入,能够从otp电路10a、10b内的otp单元一比特一比特地读出数据和end信号。

32.另外,控制电路14还能够将从otp电路10a内的otp单元读出的数字数据转换为模拟数据,并将该模拟数据作为用于使基准电压源30的电压可变的修整信息而输出。

33.图2是表示具备第1实施方式的otp读出电路的lsi的图。在图1所示的lsi中,otp电路10a根据来自控制电路14的复位解除信号而读出被编程在otp单元中的数据,但图2所示的第1实施方式的otp读出电路3的特征在于,不输入来自控制电路14的复位解除信号,即使基准电压源30的基准电压有偏差,也能自行地从otp单元读出数据。

34.图2所示的lsi相对于图1所示的lsi,不同之处在于otp读出电路3,因此在此主要说明otp读出电路3。otp读出电路3具备与控制电路14连接的otp电路1a和与otp电路1a连接的可读出信号输出部2。

35.otp电路1a具有多个otp单元,各个otp单元能够将1比特的数据进行编程,并能够读出数据。otp电路1a例如由8比特数据构成。

36.控制电路14将数据编程(prog)到otp电路1a、10b内的otp单元中,并且,将输入信号(din)作为输入,从otp电路1a、10b一比特一比特地读出数据和end信号。

37.另外,控制电路14还能够将从otp电路1a读出的数字数据转换为模拟数据,并将该模拟数据作为修整信息向基准电压源30输出。

38.otp电路1a具有将数据仅能编程一次的otp单元。可读出信号输出部2生成用于读出被编程在otp电路1a内的otp单元的数据的可读出电压,并将所生成的可读出电压输出至otp电路1a。otp电路1a通过来自可读出信号输出部2的可读出电压来读出被编程于otp单元的数据。

39.otp电路1a示意性地如图3所示,具备:恒流源11、具有otp单元的存储单元信息取得部12、和读出放大器(sense amp)13。恒流源11通过使存储单元信息取得部12中流过恒定电流,使被施加在otp单元上的电压上升,使otp单元中流过固定电流。当在otp单元中流过固定电流时,读出放大器13读出被编程在otp单元中的数据并输出。

40.可读出信号输出部2具备:恒流源21、具有otp单元的存储单元信息取得部22和比较器23。恒流源21由与otp电路1a所具有的恒流源11相同的结构构成。存储单元信息取得部22所具有的otp单元由与otp电路1a内的存储单元信息取得部12所具有的otp单元相同的结构构成。

41.恒流源21通过使存储单元信息取得部22中流过恒定电流,使施加在otp单元上的电压上升,在otp单元中流过固定电流。比较器23在存储单元信息取得部22的输出电压为基准电压e1(例如1v)以上的情况下,将用于读出被编程在存储单元信息取得部12所具有的otp单元中的数据的可读出电压rvo,输出到otp电路1a的xrst端子。

42.根据这样构成的第1实施方式的otp读出电路3,在可读出信号输出部2内的存储单元信息取得部22中流过恒定电流,被施加在otp单元上的电压上升,在otp单元中流过固定电流。于是,从比较器23向otp电路1a的xrst端子输出用于读出在存储单元信息取得部12所具有的otp单元的数据的可读出电压rvo。

43.在otp电路1a中,若向xrst端子输入读出完成电压rvo,则恒流源11动作,在存储单

元信息取得部12中流过恒定电流,在otp单元中流过固定电流。即,存储单元信息取得部12所具有的otp单元和存储单元信息取得部22所具有的otp单元由相同结构的otp单元构成,因此存储单元信息取得部12所具有的otp单元的可读出电压和存储单元信息取得部22所具有的otp单元的可读出电压相同。因此,能够通过来自可读出信号输出部2的可读出电压来读出otp单元的数据。

44.因此,即使不输入来自控制电路14等的外部的复位解除信号,并且,基准电压源30的基准电压有偏差,otp读出电路3也能够自行地从otp电路1a内的otp单元读出数据。因此,即使没有达到其他电路进行动作所需的电源电压,也能够以比该电压低的电压读出otp单元的数据,能够在lsi的电源接通(立

ち

上

げ

)后立即进行修整。

45.(otp读出电路3的具体结构例)

46.接着,说明otp读出电路3的具体结构例。图5是图3所示的otp电路1a的具体电路结构图。在图5中,恒流源11具有:mosfetq1~q7、开关s1~s6、电阻r1~r2。mosfetq1、q2、q5、q6、q7由p沟道构成,源极与电源vdd连接。mosfetq3、q4由n沟道构成,源极经由电阻r1与接地vss连接。mosfetq3的栅极连接到接地vss,并且mosfetq4的栅极经由电阻r2连接到接地vss。mosfetq3的结构与mosfetq4的结构不同。

47.存储单元信息取得部12具有mosfetq8~q10、晶体管ms、晶体管mr、电阻r3、r4、otp存储晶体管m0(相当于otp单元、存储晶体管)。mosfetq8、晶体管ms和电阻r3的串联电路连接在mosfetq6的漏极和接地vss之间。mosfetq9、晶体管mr(相当于第1晶体管)和电阻r4的串联电路连接在mosfetq7的漏极和接地vss之间。

48.晶体管mr的栅极和otp存储晶体管m0(相当于otp单元、存储晶体管)的栅极,与mosfetq7的漏极连接。晶体管mr的源极经由电阻r4被接地,otp存储晶体管m0的源极被接地。

49.晶体管mr的漏极与mosfetq9的源极连接,otp存储晶体管m0的漏极与mosfetq10的源极连接。即,晶体管mr和otp存储晶体管m0构成电流镜电路。

50.读出放大器13具有mosfetq11~q13、otp存储晶体管m1、开关s7~s12、电阻r5、电容器c1、c2、反相器in1~in5。在电源vdd和接地vss之间连接有mosfetq11、mosfetq10和otp存储晶体管m0。在电源vdd和接地vss之间连接有mosfetq12、mosfetq13和otp存储晶体管m1。

51.mosfetq11和mosfetq12构成触发器电路。从mosfetq12的漏极经由反相器in1~in3从otp存储晶体管m0被读出的数据,从dout端子被输出。

52.图6是图3所示的可读出信号输出部2的具体的电路结构图。在图6中,恒流源21具有mosfetq21~q27、开关s21~s26、电阻r11~r12。mosfetq21、q22、q25、q26、q27由p沟道构成,源极与电源vdd连接。mosfetq23、q24由n沟道构成,源极经由电阻r11与接地vss连接。mosfetq23的栅极连接到接地vss,并且mosfetq24的栅极经由电阻r12连接到接地vss。mosfetq23的结构与mosfetq24的结构不同。

53.存储单元信息取得部22具有mosfetq28~q30、晶体管ms、晶体管mr、otp存储晶体管m0(对应于otp单元)、以及电阻r13~r15。mosfetq28、晶体管ms和电阻r13的串联电路连接在mosfetq26的漏极和接地vss之间。mosfetq29、晶体管mr和电阻r14的串联电路连接在mosfetq27的漏极和接地vss之间。

54.另外,示出了如下情况:图6所示的存储单元信息取得部22内的晶体管ms、晶体管mr和otp存储晶体管m0,与图5所示的存储单元信息取得部12内的晶体管ms、晶体管mr和otp存储晶体管m0为相同结构。

55.比较器23具有mosfetq31~q37、开关s27~s31、电阻r16~r18、电容器c3、反相器in7~in8。mosfetq31的源极、mosfetq32的源极、mosfetq33的源极、mosfetq34的源极和mosfetq37的源极连接到电源vdd。

56.在mosfetq31的漏极和接地vss之间连接有mosfetq30、otp存储晶体管m0和电阻r15的串联电路。在mosfetq32的漏极和接地vss之间连接有电阻r16和电阻r17的串联电路。mosfetq37的栅极连接到mosfetq31的栅极和mosfetq32的栅极。mosfetq37的漏极与开关s29的一端连接,开关s29的另一端连接在电阻r16和电阻r17之间。能够以电阻r16和电阻r17之比来检测电源vdd的电压,即使在电源vdd的电压很低的情况下也能够进行检测。

57.mosfetq33的漏极上连接mosfetq35的漏极,mosfetq34的漏极上连接mosfetq36的漏极,mosfetq35的源极和mosfetq36的源极经由电阻r18与接地vss连接。

58.mosfetq36的栅极连接到接地vss,并且mosfetq35的栅极经由电阻r17连接到接地vss。mosfetq35的结构与mosfetq36的结构不同。可读出电压rvo从与mosfetq36的漏极连接的反相器in7被输出。

59.接着,参照图5以及图6,说明可读出信号输出部2的动作以及otp电路1a的数据的读出。

60.首先,在可读出信号输出部2的恒流源21中,当开关s22、s23导通时,mosfetq21、q22、q23、q24、q25、q26、q27导通。mosfetq23的栅极被接地,mosfetq24的栅极上连接着电阻r12,因此mosfetq23的栅极与mosfetq24的栅极之间产生电位差vth。该电位差vth成为恒压源,通过恒压源,电流流过mosfetq25、q26、q27。

61.通过流过mosfetq26的电流,mosfetq28、q29、q30的栅极电位上升。因此,电流以mosfetq26

→

mosfetq28

→

晶体管ms

→

电阻r13的路径流动。另外,电流以mosfetq27

→

mosfetq29

→

晶体管mr

→

电阻r14的路径流动。

62.mosfetq30的栅极电位与otp存储晶体管m0的栅极电位上升,电流以mosfetq31

→

mosfetq30

→

otp存储晶体管m0

→

电阻r15的路径流动。于是,电流从mosfetq32流向电阻r16和电阻r17。在mosfetq35的栅极上施加由流过电阻r17的电流和电阻r17产生的电压,由于mosfetq36的栅极被接地,所以在mosfetq35的栅极和mosfetq36的栅极上产生电位差vth。

63.电位差vth成为比较器23的基准电压e1,在晶体管ms、晶体管mr、otp存储晶体管m0中流过固定电流时的电压、即可读出电压(比电压vdd低的电压)和作为基准电压e1(例如1v)的电位差vth被进行比较。在可读出电压小于电位差vth的情况下,可读出电压不从反相器in7向rvo端子输出,但在可读出电压为电位差vth以上时,从反相器in7向rvo端子输出可读出电压。

64.接着,说明图5以及图7所示的otp电路1a的数据的读出。当向otp电路1a输入可读出电压时,开关s2、s3导通,mosfetq1、q2、q3、q4、q5、q6、q7导通。mosfetq3的栅极被接地,mosfetq4的栅极上连接着电阻r1,因此mosfetq3的栅极与mosfetq4的栅极上产生电位差vth。该电位差vth成为恒压源,通过恒压源在mosfetq5、q6、q7中流过电流。

65.通过流过mosfetq6的电流,mosfetq8、q9、q10的栅极电位上升。因此,电流igate以

mosfetq6

→

mosfetq8

→

晶体管ms

→

电阻r3的路径流动。另外,电流以mosfetq7

→

mosfetq9

→

晶体管mr

→

电阻r4的路径流动。

66.在此,由于将电阻r4的一端与晶体管mr的源极连接,将otp存储晶体管m0的源极与接地vss连接,所以在otp存储晶体管m0中流过大的电流,在晶体管mr中几乎不流过电流。通过在otp存储晶体管m0中流过大的电流,能够从otp存储晶体管m0将数据“1”读出至dout端子。

67.图8是说明图3所示的otp电路1a的具体电路将数据编程时的动作的图。图8的数据编程时的结构相对于图7的数据读出时的结构,追加了开关s13~s16。开关s13连接在写入电压与mosfetq9的漏极之间,开关s14连接在写入电压与otp存储晶体管m0的源极之间。开关s15的一端与otp存储晶体管m0的源极连接,另一端接地。开关s16的一端与otp存储晶体管m0的漏极连接,另一端接地。写入电压例如为7v,从控制电路14供给。

68.在将数据编程在otp存储晶体管m0时,使开关s13、s14、s16导通。于是,在otp存储晶体管m0的栅极和源极上被施加7v,在otp存储晶体管m0的漏极上被施加0v,因此otp存储晶体管m0导通,大电流流入otp存储晶体管m0。因此,数据被编程在otp存储晶体管m0中。

69.另外,被编程在otp单元中的数据也可以是用于校正基准电压源30的基准电压的修整信息。通过从otp单元读出该修整信息来校正可变电源31的电压,能够校正基准电压。

70.此外,被编程在otp单元中的数据不限于修整信息。被编程在otp单元中的数据例如也可以在otp单元中对显示面板或照相机等外部设备的校正信息进行编程,otp读出电路读出被编程得到的校正信息,使用校正信息来校正显示面板或照相机的参数等。

71.另外,被编程在otp单元中的数据也可以是:用于校正(修整)传感器的制作偏差的信息(气压传感器、陀螺仪等);用于校正led的制作偏差的信息;与功率晶体管相匹配地来校正用于驱动功率晶体管的驱动器的信息;校正ic自身的偏差并提高输出精度的信息;以及通过设置(set)来变更启动时序的信息;根据部件的温度来校正特性的信息;晶片的批号(wa.lot.no.)或组装批号(lot.no.)等制造时可进行跟踪的信息;检测设置(set)的异常并进行怎样的保护来切断系统的信息;校正电动机驱动中的初始位置的信息。也可以将这些信息编程到otp单元,从otp单元读出信息。

72.(第2实施方式)

73.接着,说明第2实施方式的otp电路。在图5所示的otp电路1a中,相对于将数据编程到otp存储晶体管m0之前的电流量,将数据编程后的电流量会大幅变动。这里,将数据编程前和编程后的电流量的变动率称为编程倍率。

74.将数据编程后的otp存储晶体管m0的栅极-源极间的电位差vth,从编程前到编程后,例如从0.8v转变(shift)为2v。该电位差vth在程序倍率成为最大的电压下饱和。

75.因此,为了在程序倍率为最大的电压下容易读出数据,使用电位差vth的差分来读出数据。因此,采用由图6所示的晶体管mr和otp存储晶体管m0构成的电流镜电路。

76.另外,在读出被编程在otp存储晶体管m0中的数据时,通过由偏置电路构成的恒流源11,使恒定电流流过晶体管mr和otp存储晶体管m0,使晶体管mr和otp存储晶体管m0的栅极-源极间电压vgs=漏极-源极间电压vds逐渐上升。

77.此时,在具有低电位差vth1(第1阈值电压)的晶体管mr中先流过电流,在具有高电位差vth2(第2阈值电压)的被编程后的otp存储晶体管m0中,之后流过电流。因此,在晶体管

mr中流过电流后,能够在编程倍率大致为最大的电压下读出被编程在otp存储晶体管m0中的数据。

78.图9表示在otp电路1a内设置了偏置电路的情况下,能够精确地设定数据的读取条件的情形。图9示出了电压vgs与编程倍率之间的关系。当使栅极-源极间电压vgs上升,成为规定电压时,程序倍率成为最大。

79.因此,在读出被编程在otp存储晶体管m0的数据时,通过在编程倍率成为大致最大的电压下读出数据,可谋求数据读出的稳定化。另外,由于在程序倍率大致最大的电压下读出数据,所以能够缩短程序时间。

80.另外,图10表示在otp电路1a内不设置偏置电路的情况下,数据的读取条件扩大的情形。

81.如以上那样,说明了几个实施方式,但这些实施方式是作为例子而提示的,并不意图限定发明的范围。这些新的实施方式能够以其他各种方式实施,在不脱离发明的主旨的范围内,能够进行各种省略、置换、变更。这些实施方式及其变形包含在发明的范围及主旨内,并且包含在权利要求书所记载的发明及其均等的范围内。

82.1a、10a、10b otp电路

83.2 可读出信号输出部

84.3 otp读出电路

85.11、21 恒流源

86.12、22 存储单元信息取得部

87.13 读出放大器

88.23 比较器

89.14 控制电路

90.30 基准电压源

91.31 可变电源

92.32 运算放大器

93.33 上电复位电路(por电路)

94.q1~q13、q21~q36 mosfet

95.ms、mr 晶体管

96.m0、m1 otp存储晶体管

97.s1~s12、s21~s31 开关

98.r1~r5、r11~r18 电阻

99.in1~in8 反相器

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。