半导体器件以及包括半导体器件的电子系统

1.相关申请的交叉引用

2.本技术基于以下申请并要求以下申请的优先权:2020年8月12日向韩国知识产权局递交的韩国专利申请no.10-2020-0101398,其全部公开内容通过引用合并于此。

技术领域

3.本公开的方面涉及一种半导体器件和一种包括该半导体器件的电子系统,更具体地,涉及一种包括非易失性竖直型存储元件的半导体器件和一种包括该半导体器件的电子系统。

背景技术:

4.可以在电子系统中存储大量数据的半导体器件日益受到人们的青睐。已经研究了用于增大半导体器件的数据存储容量的方法和技术。例如,已经提出了一种用于增大半导体器件的数据存储容量的技术在于包括竖直存储元件,该竖直存储元件包括三维布置的存储单元而不是二维布置的存储单元。

技术实现要素:

5.本公开的一些方面提供了一种半导体器件,该半导体器件包括三维布置的存储单元,并且即使用于集成改进的字线的层数增加并且连接到字线的接触部的数量和布线的数量增加,该半导体器件也可以维持期望的电特性。

6.本公开的一些方面提供了一种电子系统,该电子系统包括半导体器件,该半导体器件包括三维布置的存储单元,并且即使用于集成改进的字线的层数增加并且连接到字线的接触部的数量和布线的数量增加,该半导体器件也可以维持期望的电特性。

7.根据本发明构思的一些方面,提供了一种半导体器件,包括:衬底,包括存储单元区域和连接区域;多个栅极线,在衬底的存储单元区域中彼此竖直地重叠,每个栅极线包括第一金属;阶梯状连接单元,该阶梯状连接单元包括多个导电焊盘区域,每个导电焊盘区域一体地连接到多个栅极线中的相应栅极线并且包括第一金属;多个接触结构,与阶梯状连接单元竖直地重叠,每个接触结构连接到多个导电焊盘区域中的分别对应的导电焊盘区域并且包括第二金属;以及至少一个金属硅化物层,在至少一个接触结构与分别对应的导电焊盘区域之间。

8.根据本发明构思的一些方面,提供了一种半导体器件,包括:衬底,包括存储单元区域和连接区域;栅极堆叠,包括与第一导电焊盘区域一体地连接的第一栅极线,该第一栅极线在存储单元区域中在与衬底的主表面平行的水平方向上延伸,并且该第一导电焊盘区域在连接区域中在水平方向上延伸,并且该第一栅极线和导电焊盘区域均包括第一金属;接触结构,在连接区域中在竖直方向上延伸,该接触结构包括第二金属;以及金属硅化物层,在第一导电焊盘区域与接触结构之间,该金属硅化物层接触第一导电焊盘区域和接触结构。

9.根据本发明构思的一方面,一种电子系统包括:主衬底;半导体器件,在主衬底上;以及控制器,电连接到主衬底上的半导体器件,其中,该半导体器件包括:器件衬底,包括存储单元区域和连接区域;栅极堆叠,包括与导电焊盘区域一体地连接的栅极线,该栅极线在衬底的存储单元区域中在与衬底的主表面平行的水平方向上延伸,并且该导电焊盘区域在连接区域中在水平方向上延伸,并且该栅极线和该导电焊盘区域均包括第一金属;接触结构,在连接区域中竖直地延伸,并且包括第二金属;金属硅化物层,在所述导电焊盘区域与所述接触结构之间;外围电路区域,与栅极堆叠间隔开;以及输入/输出焊盘,在器件衬底上。

附图说明

10.根据以下结合附图的详细描述中,将更清楚地理解本发明构思的一些示例实施例,在附图中:

11.图1是示出了根据本发明构思的一些实施例的半导体器件的框图;

12.图2是根据本发明构思的一些实施例的半导体器件的示意性透视图;

13.图3示出了根据本发明构思的一些实施例的半导体器件的存储单元阵列的等效电路图;

14.图4是根据本发明构思的一些实施例的半导体器件的主要组件的平面图;

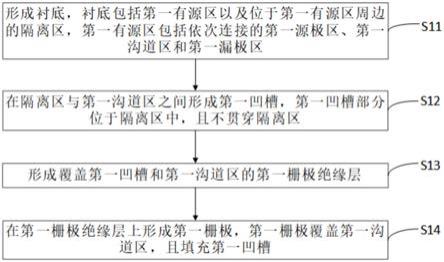

15.图5a示出了沿图4中的线a1-a1’和线a2-a2’截取的截面图以及外围电路区域的某一区域的截面图,图5b是沿图4中的线b-b’截取的截面图,并且图5c是图5a中的局部区域ex1的放大截面图;

16.图6a是如图5b中的bx指示的区域的截面图;

17.图6b至图6d均是栅极介电层的示例结构的截面图;

18.图7a至图7c均是根据本发明构思的一些实施例的半导体器件的修改示例的截面图;

19.图8a示出了根据本发明构思的其他实施例的半导体器件的修改示例的截面图,图8b中的(a)是图8a中的局部区域ex31的放大截面图,并且图8b中的(b)是图8a中的局部区域ex32的放大截面图;

20.图9是根据本发明构思的一些实施例的半导体器件的截面图;

21.图10是根据本发明构思的一些实施例的半导体器件的截面图;

22.图11是根据本发明构思的一些实施例的半导体器件的截面图;

23.图12是根据本发明构思的一些实施例的半导体器件的截面图;

24.图13是根据本发明构思的一些实施例的包括半导体器件的电子系统的示意图;

25.图14是根据本发明构思的一些实施例的包括半导体器件的电子系统的示意性透视图;

26.图15是根据本发明构思的一些实施例的半导体封装的示意性截面图;

27.图16是根据本发明构思的一些实施例的半导体封装的示意性截面图;

28.图17a至图17e是示出了根据本发明构思的一些实施例的根据工艺顺序的半导体器件的制造方法的截面图;以及

29.图18a至图18e是示出了根据本发明构思的一些实施例的依据根据工艺顺序的半

导体器件的制造方法形成金属硅化物层和接触结构的过程的截面图。

具体实施方式

30.在下文中,将参考附图详细描述本发明构思的一些示例实施例。在附图中,相同的附图标记用于相同的组件,并且将省略其重复描述。

31.图1是根据本发明构思的一些实施例的半导体器件10的框图。

32.参照图1,半导体器件10可以包括存储单元阵列20和外围电路30。存储单元阵列20可以包括第一存储单元块blk1至第n存储单元块blkn。第一存储单元块blk1至第n存储单元块blkn均可以包括多个存储单元(图1中未示出)。第一存储单元块blk1至第n存储单元块blkn中的每一个可以经由至少一个位线bl、至少一个字线wl、至少一个串选择线ssl、至少一个地选择线gsl和公共源极线csl连接到外围电路30。如关于图4和图5a至图5c更详细地讨论的,至少一个字线wl、至少一个串选择线ssl和至少一个地选择线gsl可以被称为栅极堆叠gs。

33.外围电路30可以包括行解码器32、页缓冲器34、数据输入输出(i/o)电路36、控制逻辑器件38和csl驱动器39。尽管在图1中未示出,但是外围电路30还可以包括各种电路,例如用于生成存储器件10的操作所需的各种电压的电压生成电路、用于校正从存储单元阵列20读取的数据的错误的错误校正电路、和i/o接口。

34.存储单元阵列20可以经由位线bl连接到页缓冲器电路34,并且可以经由至少一个字线wl、至少一个串选择线ssl和至少一个地选择线gsl连接到行解码器32。在存储单元阵列20中,包括在第一存储单元块blk1至第n存储单元块blkn中的多个存储单元中的每一个存储单元可以包括闪存单元。存储单元阵列20可以包括三维存储单元阵列。三维存储单元阵列可以包括多个nand串,并且多个nand串可以包括分别与栅极堆叠gs连接的多个竖直堆叠的存储单元。

35.外围电路30可以从存储器件10的外部接收地址addr、命令cmd和控制信号ctrl,并且可以向存储器件10外部的设备发送数据data/从存储器件10外部的设备接收数据data。

36.行解码器32可以响应于来自存储器件10的外部的地址addr而选择第一存储单元块blk1至第n存储单元块blkn中的至少一个,并且可以选择选定的存储单元块blk1至blkn的栅极堆叠gs(例如,至少一个字线wl、至少一个串选择线ssl和至少一个地选择线gsl)。行解码器32可以将用于执行存储操作的电压发送到选定的存储单元块blk1至blkn的栅极堆叠gs。

37.页缓冲器34可以经由位线bl连接到存储单元阵列20。页缓冲器34可以在编程操作期间充当输入驱动器,并且可以将根据要存储在存储单元阵列20中的数据data的电压施加到位线bl。页缓冲器34可以在读操作期间充当读出放大器,并且检测存储在存储单元阵列20中的数据data。页缓冲器34可以根据由控制逻辑器件38提供的控制信号pctl进行操作。

38.数据i/o电路36可以经由多个数据线dl连接到页缓冲器34。数据i/o电路36可以在编程操作期间从存储控制器(未示出)接收数据data,并且基于由控制逻辑器件38提供的列地址c_addr将编程数据data提供给页缓冲器34。数据i/o电路36可以基于在读操作期间由控制逻辑器件38提供的列地址c_addr,向存储控制器提供已存储在页缓冲器34中的读数据data。

39.数据i/0电路36可以发送要输入到控制逻辑器件38或行解码器32的地址或命令。外围电路30还可以包括静电放电(esd)电路和上拉/下拉驱动器。

40.控制逻辑器件38可以从存储控制器接收命令cmd和控制信号ctrl。控制逻辑器件38可以将行地址r_addr提供给行解码器32,并且将列地址c_addr提供给数据i/o电路36。控制逻辑器件38可以响应于控制信号ctrl而生成在半导体器件10中使用的各种内部控制信号。例如,当执行诸如编程操作和擦除操作之类的存储操作时,控制逻辑器件38可以控制要提供给栅极堆叠gs和位线bl的电压电平。

41.csl驱动器39可以经由公共源极线csl连接到存储单元阵列20。csl驱动器39可以基于控制逻辑器件38的控制来将公共源极电压(例如,电源电压)或地电压施加到公共源极线csl。在示例实施例中,csl驱动器39可以在存储单元阵列20的底部。csl驱动器39可以与存储单元阵列20的至少一部分处竖直地重叠。

42.图2是根据本发明构思的一些实施例的半导体器件10的示意性透视图。

43.参照图2,半导体器件10可以包括单元阵列结构cas和外围电路结构pcs,单元阵列结构cas和外围电路结构pcs可以在竖直方向(例如,z方向)上重叠。单元阵列结构cas可以包括以上参考图1描述的存储单元阵列20。外围电路结构pcs可以包括以上参考图1描述的外围电路30。

44.单元阵列结构cas可以包括多个片状结构24。多个片状结构24均可以包括第一存储单元块blk1至第n存储单元块blkn。第一存储单元块blk1至第n存储单元块blkn均可以包括以三维阵列布置的存储单元。

45.在一些示例实施例中,两个片状结构24可以构成一个垫,但是本公开不限于此。上面参考图1描述的存储单元阵列20可以包括多个垫,例如四个垫,但是本公开不限于此。

46.图3是根据本发明构思的一些实施例的半导体器件的存储单元阵列mca的等效电路图。图3示出了具有竖直沟道结构的竖直nand闪存元件的等效电路图。图2所示的第一存储单元块blk1至第n存储单元块blkn均可以包括具有图3所示的等效电路配置的存储单元阵列mca。

47.参照图3,存储单元阵列mca可以包括多个存储单元串ms。存储单元阵列mca可以包括多个位线bl或第一位线bl1至第m位线blm、多个字线wl或第一字线wl1至第n字线wln、至少一个串选择线ssl、至少一个地选择线gsl和公共源极线csl。多个存储单元串ms可以形成在多个位线bl和公共源极线csl之间。图3示出了多个存储单元串ms中的每一个包括两个串选择线ssl的情况,但是本公开不限于此。例如,多个存储单元串ms中的每一个可以包括一个串选择线ssl。

48.多个存储单元串ms中的每一个可以包括串选择晶体管sst、地选择晶体管gst以及第一存储单元晶体管mc1至第n存储单元晶体管mcn。串选择晶体管sst的漏极区可以连接到位线bl之一,并且地选择晶体管gst的源极区可以连接到公共源极线csl。公共源极线csl可以是多个地选择晶体管gst的源极区彼此共同地连接的区域。

49.串选择晶体管sst可以连接到串选择线ssl,并且地选择晶体管gst可以连接到地选择线gsl。第一存储单元晶体管mc1至第n存储单元晶体管mcn可以分别连接到多个字线wl。

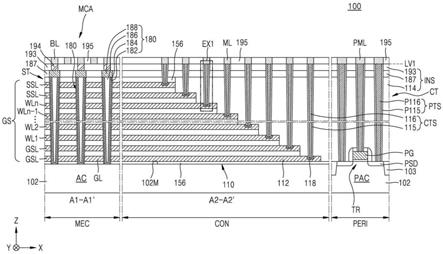

50.图4是根据本发明构思的一些实施例的半导体器件100的主要组件的平面图。图5a

示出了沿图4中的线a1-a1’和a2-a2’截取的截面图,并且还示出了半导体器件100的在图4的平面图中未示出的外围电路区域peri的截面图。图5b是沿图4中的线b-b’截取的截面图。图5c是图5a中的局部区域ex1的放大截面图。

51.参照图4和图5a至图5c,半导体器件100可以包括具有存储单元区域mec、连接区域con和外围电路区域peri在内的衬底102。衬底102可以具有沿x-y平面在水平方向上延伸的主表面102m。衬底102可以包括硅(si)、锗(ge)或硅锗(sige)。存储单元阵列mca可以形成在存储单元区域mec的有源区ac中。

52.连接区域con可以与存储单元区域mec的边缘侧相邻。存储单元区域mec可以与外围电路区域peri间隔开,其中在存储单元区域mec与外围电路区域peri之间具有连接区域con。在图5a中,仅示出了在存储单元区域mec的一侧的连接区域con,但是在一些实施例中,连接区域con可以在第一水平方向(x方向)上在存储单元区域mec的两侧中的每一侧。

53.栅极堆叠gs可以在衬底102的存储单元区域mec和连接区域con中。栅极堆叠gs可以包括多个栅极线gl、以及一体地连接到多个栅极线gl的多个导电焊盘区域112。存储单元区域mec中的栅极堆叠gs的一部分可以构成存储堆叠st。存储堆叠st可以包括在竖直方向(z方向)上堆叠的48、64、96或128个栅极线gl,但是本公开不限于此。包括在栅极堆叠gs中的多个栅极线gl可以在存储单元区域mec中,而存储单元区域mec中的多个栅极线gl在与衬底102的主表面102m平行的水平方向上延伸,并且在竖直方向(z方向)上彼此重叠。多个栅极线gl可以包括多个字线wl(即,第一字线wl1至第n字线wln)、至少一个地选择线gsl和至少一个串选择线ssl。在图5a和图5b中,示出了多个栅极线gl包括两个地选择线gsl和两个串选择线ssl的情况,但是本公开不限于此。

54.栅极堆叠gs中包括的多个导电焊盘区域112可以在连接区域con中并构成阶梯状连接单元110。如图4所示,在连接区域con中,与第二导电焊盘区域112相比,在竖直方向上更靠近衬底102的第一导电焊盘区域112可以在第一水平方向(x方向)上延伸得更远,其中与第一导电焊盘区域112相比,该第二导电焊盘区域112距衬底102更远。多个导电焊盘区域112中的每一个可以一体地连接到多个栅极线gl中的一个栅极线gl。

55.如图4和图5b所示,多个字线切割区域wlc可以在与衬底102的主表面102m平行的第一水平方向(x方向)上延伸。多个字线切割区域wlc可以限制栅极堆叠gs在与第一水平方向(x方向)垂直的第二水平方向(y方向)上的宽度。栅极堆叠gs可以通过多个字线切割区域wlc以均匀的间隔彼此重复地间隔开。

56.如图5b所示,多个公共源极区106可以在衬底102中在第一水平方向(x方向)上延伸。在一些示例实施例中,多个公共源极区106可以包括在其上重掺杂有n型杂质的杂质区。多个公共源极线csl可以在多个公共源极区106上在第一水平方向(x方向)上延伸。多个公共源极线csl可以填充在栅极堆叠gs的每一侧的字线切割区域wlc的一部分。公共源极线csl可以在字线切割区域wlc中被绝缘间隔物192围绕。公共源极线csl和绝缘间隔物192可以构成穿透存储堆叠st的字线切割结构wcs。

57.另外,如图5b所示,在第二水平方向(y方向)上彼此相邻的两个串选择线ssl可以彼此间隔开,并且在所述相邻的两个串选择线ssl之间具有串选择线切割区域sslc。串选择线切割区域sslc可以填充有绝缘层174。绝缘层174可以包括氧化物层、氮化物层或其组合。在一些示例实施例中,串选择线切割区域sslc中的至少一些可以填充有气隙。

58.多个栅极线gl和多个导电焊盘区域112均可以包括金属、导电金属硝酸盐或其组合。例如,多个栅极线gl和导电焊盘区域112均可以包括钨、镍、钴、钽、硝酸钨、硝酸钛、硝酸钽或其组合,但是本公开不限于此。

59.如图5a和图5b所示,可以将与多个导电焊盘区域112组合的多个栅极线gl与多个绝缘层156交替地堆叠。换句话说,绝缘层156可以在衬底102和地选择线gsl之间,并且绝缘层156可以在地选择线gsl、多个字线wl(即,第一字线wl1至第n字线wln)中的每一个和每个串选择线ssl的上方和下方。绝缘层156可以在一对相邻的栅极线gl与一对相邻的导电焊盘区域112之间,并且每个栅极线gl/导电焊盘区域112可以包括在多于一对相邻的栅极线gl/导电焊盘区域1112中。衬底102上的多个绝缘层156中与衬底102最靠近的绝缘层156可以具有比其他绝缘层156小的厚度。作为示例,多个绝缘层156可以包括氧化硅、氮化硅或sion。

60.在存储单元区域mec中,多个沟道结构180可以穿透多个栅极线gl和多个绝缘层156,并且可以在竖直方向(z方向)上延伸。多个沟道结构180可以在第一水平方向(x方向)和第二水平方向(y方向)上以一定间隔彼此间隔开。

61.多个沟道结构180均可以包括栅极介电层182、沟道区184、掩埋绝缘层186和漏极区188。沟道区184可以包括掺杂的多晶硅和/或未掺杂的多晶硅。沟道区184可以具有圆柱形形状或管状形状。沟道区184的内部空间可以填充有掩埋绝缘层186。掩埋绝缘层186可以包括绝缘材料。例如,掩埋绝缘层186可以包括氧化硅、氮化硅、sion或其组合。在一些示例实施例中,可以省略掩埋绝缘层186,并且沟道区184可以具有不具有内部空间的柱状结构。漏极区188可以包括掺杂有杂质的多晶硅、金属或导电金属氮化物、或者其组合。构成漏极区188的金属可以包括例如钨、镍、钴、钽等。

62.多个漏极区188可以通过中间绝缘层187彼此绝缘。中间绝缘层187可以包括氧化物层、氮化物层或其组合。

63.在图5a和图5b中,沟道结构180被示为包括栅极介电层182,并且栅极介电层182具有在竖直方向(z方向)上沿沟道区184延伸的形状,但是本公开不限于此,并且可以对其进行各种修改和改变。

64.图6a是图5a和图5b所示的栅极介电层182的详细截面图,并且是图5b中的区域bx的放大图。

65.参照图6a,栅极介电层182可以具有包括从沟道区184顺序地形成的隧穿介电层td、电荷存储层cs和阻挡介电层bd在内的结构。隧穿介电层td、电荷存储层cs和阻挡介电层bd的相对厚度不限于图6a所示的厚度,并且可以对其进行各种修改。

66.隧穿介电层td可以包括氧化硅、氧化铪、氧化铝、氧化锆、氧化钽等。电荷存储层cs可以是其中存储了已从沟道区184穿过隧穿介电层td的电子的区域,并且可以包括氮化硅、氮化硼、氮化硅硼或掺杂有杂质的多晶硅。阻挡介电层bd可以包括氧化硅、氮化硅或介电常数比氧化硅高的金属氧化物。金属氧化物可以包括氧化铪、氧化铝、氧化锆、氧化钽或其组合。

67.图6b至图6d是栅极介电层182a、182b和182c的示例结构的截面图,其可以代替图6a所示的栅极介电层182而采用。

68.在一些示例实施例中,半导体器件100可以包括图6b所示的栅极介电层182a,而不是栅极介电层182。栅极介电层182a可以包括与图6a所示的栅极介电层182基本相同的配

置。然而,栅极介电层182a可以包括第一阻挡介电层bd1和第二阻挡介电层bd2,而不是阻挡介电层bd。第一阻挡介电层bd1可以与沟道区184平行地延伸,并且第二阻挡介电层bd2可以围绕栅极线gl。第一阻挡介电层bd1和第二阻挡介电层bd2均可以包括氧化硅、氮化硅或金属氧化物。例如,第一阻挡介电层bd1可以包括氧化硅层,并且第二阻挡介电层bd2可以包括介电常数比氧化硅层大的金属氧化物层。

69.在其他示例实施例中,半导体器件100可以包括图6c所示的栅极介电层182b,而不是栅极介电层182。栅极介电层182b可以覆盖面向沟道区184的表面、以及面向栅极线gl的绝缘层156的表面。栅极介电层182b可以包括从沟道区184顺序地形成的隧穿介电层td、电荷存储层cs和阻挡介电层bd。

70.另外,在其他示例实施例中,半导体器件100可以包括图6d所示的栅极介电层182c,而不是栅极介电层182。栅极介电层182c可以在栅极线gl和沟道区184之间,并且覆盖栅极线gl的侧壁,但是可以不覆盖栅极线gl的底表面和顶表面。栅极介电层182c可以包括从沟道区184顺序地形成的隧穿介电层td、电荷存储层cs和阻挡介电层bd。

71.可以包括在根据本发明构思的实施例的半导体器件中的栅极介电层的配置和形状不限于图6a至图6d所示的栅极介电层182、182a、182b和182c,并且可以在本发明构思的范围内对其进行各种修改和改变。

72.再次参照图4和图5a至图5c,在连接区域con中构成阶梯状连接单元110的多个导电焊盘区域112中的每一个在水平方向上的宽度可以随着距衬底102的距离的增大而逐渐减小。

73.在一些示例实施例中,穿透阶梯状连接单元110的多个虚设沟道结构(未示出)可以在连接区域con中。通过支撑栅极堆叠gs和多个导电焊盘区域112中的每一个的边缘部分,多个虚设沟道结构可以防止发生不希望的结构变形,例如其弯曲或断裂。

74.在存储单元区域mec中,多个位线bl可以在存储堆叠st上方。多个位线接触焊盘194可以在多个沟道结构180和多个位线bl之间。多个沟道结构180中的每一个的漏极区188可以经由相应的位线接触焊盘194连接到多个位线bl中的一个位线bl。多个位线接触焊盘194可以通过上绝缘层193彼此绝缘。多个位线bl可以通过层间绝缘层195彼此绝缘。多个位线接触焊盘194和多个位线bl均可以包括金属、金属氮化物或其组合。例如,多个位线接触焊盘194和多个位线bl均可以包括钨、钛、钽、铜、铝、氮化钛、氮化钽、氮化钨或其组合。上绝缘层193和层间绝缘层195均可以包括氧化物层、氮化物层或其组合。

75.在连接区域con中,覆盖阶梯状连接单元110的绝缘层114可以在衬底102和中间绝缘层187之间。绝缘层114可以覆盖多个导电焊盘区域112。绝缘层114、中间绝缘层187和上绝缘层193可以构成绝缘结构ins。绝缘结构ins也可以存在于外围电路区域peri中。

76.在连接区域con中,在竖直方向(z方向)上延伸的多个接触结构cts可以在阶梯状连接单元110的多个导电焊盘区域112上。多个金属硅化物层118可以位于多个接触结构cts和多个导电焊盘区域112之间的多个连接部分处。

77.多个接触结构cts中的每一个可以包括在竖直方向(z方向)上延伸的接触插塞116、以及围绕接触插塞116的绝缘插塞115。多个接触结构cts中的每一个的接触插塞116可以经由多个金属硅化物层118连接到阶梯状连接单元110的导电焊盘区域112。

78.如在图5c中更详细地示出的,金属硅化物层118和接触结构cts可以延伸到导电焊

盘区域112中,直到比导电焊盘区域112的上表面的竖直水平高度低的竖直水平高度,并且金属硅化物层118的最下表面可以与导电焊盘区域112的下表面间隔开。在本说明书中使用的术语“竖直水平高度”可以指示在竖直方向(z方向或-z方向)上距衬底102的上表面的距离。金属硅化物层118的最上表面的竖直水平高度可以与导电焊盘区域112的上表面的竖直水平高度基本相同。金属硅化物层118可以在等于或低于导电焊盘区域112的上表面的竖直水平高度的竖直水平高度处围绕接触结构cts的下端。金属硅化物层118可以在低于导电焊盘区域112的上表面的竖直水平高度的竖直水平高度处接触接触结构cts的接触插塞116。绝缘插塞115可以包括接触插塞116的下端与金属硅化物层118之间的部分。

79.如图5a所示,多个接触结构cts中的每一个可以在竖直方向上从与导电焊盘区域112接触的金属硅化物层118延伸到高于存储堆叠st的水平高度的第一竖直水平高度lv1。多个接触结构cts中的至少一些可以穿透包括绝缘层114、中间绝缘层187和上绝缘层193在内的绝缘层ins。多个接触结构cts中的一些可以穿透绝缘层ins的一些组件,并且可以不延伸穿过整个绝缘层ins。例如,与多个导电焊盘区域112中的距衬底102最远的导电焊盘区域112连接的接触结构cts可以从导电焊盘区域112穿透绝缘层156、中间绝缘层187和上绝缘层193,并延伸至第一竖直水平高度lv1。

80.在连接区域con中,多个布线层ml可以在多个接触结构cts上。多个布线层ml可以形成在与存储单元区域mec中的多个位线bl相同的水平高度处。多个布线层ml中的每一个可以在第一竖直水平高度lv1处连接到接触结构cts的接触插塞116。多个布线层ml中的每一个可以经由多个接触插塞116中的一个接触插塞116电连接到多个导电焊盘区域112中的一个导电焊盘区域112。多个布线层ml可以不包括与存储堆叠st竖直地重叠的部分。在连接区域con中,多个布线层ml可以通过层间绝缘层195彼此绝缘。

81.多个位线接触焊盘194和多个位线bl均可以包括钨、钛、钽、铜、铝、氮化钛、氮化钽、氮化钨或其组合。多个绝缘插塞115可以包括氮化硅层、氧化硅层或其组合。

82.在一些实施例中,包括在多个金属硅化物层118中的第一金属可以与包括在多个接触插塞116中的第二金属相同。在其他一些实施例中,包括在多个金属硅化物层118中的第一金属和包括在多个接触插塞116中的第二金属可以彼此不同。

83.在一些示例实施例中,金属硅化物层118还可以包括氮(n)和氧(o)中的至少一种元素。例如,金属硅化物层118可以包括wsi、wsin、wsio或其组合。本说明书中使用的术语“wsi”、“wsin”和“wsio”可以表示包括每个术语中包括的元素的材料,并且可以不表示化学计量关系。

84.可以在外围电路区域peri上形成多个电路ct。多个电路ct可以形成在等于或高于衬底102的竖直水平高度的竖直水平高度处。多个电路ct可以包括参考图1进行描述的外围电路30中包括的行解码器32、页缓冲器34、数据i/o电路36、控制逻辑器件38和公共源极线驱动器39中的至少一些。

85.可以在衬底102的外围电路区域peri中形成限定外围有源区pac的元件隔离层103。外围晶体管tr可以形成在外围有源区pac中。外围晶体管tr可以构成形成在外围电路区域peri上的多个电路ct的一部分。外围晶体管tr可以经由连接区域com中的布线结构而电连接到存储单元区域mec。外围晶体管tr可以包括外围栅极pg、以及在外围有源区pac中形成在外围栅极pg的两侧的外围源/漏区psd。在示例实施例中,诸如电阻器和电容器的单

元元件还可以布置在外围电路区域peri中。

86.多个外围接触结构pts可以在外围电路区域peri中。多个外围接触结构pts可以从外围晶体管tr穿透绝缘层114,并且可以在竖直方向(z方向)上延伸到第一竖直水平高度lv1。

87.多个接触结构cts中的每一个可以包括在竖直方向(z方向)上延伸的外围接触插塞p116、以及围绕外围接触插塞p116的外围绝缘插塞p115。

88.多个外围布线层pml可以在多个外围接触插塞p116上。多个外围布线层pml可以在第一竖直水平高度lv1(即,与形成在连接区域con中的多个布线层ml的水平高度相同的水平高度)处在水平方向上延伸。多个外围布线层pml中的每一个可以经由多个外围接触插塞p116中的任一个而连接到外围栅极pg和外围源/漏区psd中的任一个。多个外围布线层pml中的至少一些可以连接到外围电路区域peri中的其他电路或布线。多个外围布线层pml可以通过层间绝缘层195彼此绝缘。

89.多个外围接触插塞p116和多个外围布线层pml均可以包括钨、钛、钽、铜、铝、氮化钛、氮化钽、氮化钨或其组合。多个外围绝缘插塞p115可以包括氮化硅层、氧化硅层或其组合。

90.图7a至图7c是根据本发明构思的不同实施例的半导体器件的修改示例的截面图。图7a至图7c中的每一个示出了与图5a中的局部区域ex1相对应的部分的放大截面配置。在图7a和图7c中,与图4和图5a至图5c中的附图标记相同的附图标记可以表示相同的构件,并且省略其重复描述。

91.参照图7a,半导体器件200a可以具有与参照图4和图5a至图5c描述的半导体器件100的配置基本相同的配置。然而,半导体器件200a可以包括在导电焊盘区域112上在竖直方向(z方向)上延伸的接触结构ctsa、以及形成在接触结构ctsa与导电焊盘区域112之间的连接部分中的金属硅化物层118a。

92.接触结构ctsa可以包括在竖直方向(z方向)上延伸的接触插塞116a、以及围绕接触插塞116a的绝缘插塞115a。接触插塞116a可以经由金属硅化物层118a连接到导电焊盘区域112。

93.接触结构ctsa可以延伸到导电焊盘区域112中,直到比导电焊盘区域112的上表面的竖直水平高度低的竖直水平高度,并且金属硅化物层118a可以与导电焊盘区域112的上表面和下表面间隔开。因此,金属硅化物层118a的最下表面可以与导电焊盘区域112的下表面间隔开。金属硅化物层118a的最上表面的竖直水平高度可以低于导电焊盘区域112的上表面的竖直水平高度,并且金属硅化物层118a的最下表面的竖直水平高度可以高于导电焊盘区域112的下表面的竖直水平高度。金属硅化物层118a可以在比导电焊盘区域112的上表面的竖直水平高度低的竖直水平高度处接触接触插塞116a的底表面。在一些示例实施例中,如图7a所示,绝缘插塞115a可以不接触金属硅化物层118a。

94.金属硅化物层118a在水平方向(例如,x方向)上的宽度w2可以小于接触结构ctsa的宽度w1。金属硅化物层118a在竖直方向(z方向)上的高度可以小于导电焊盘区域112的高度。

95.参照图7b,半导体器件200b可以具有与参照图4和图5a至图5c描述的半导体器件100的配置基本相同的配置。然而,半导体器件200b可以包括在导电焊盘区域112上在竖直

方向(z方向)上延伸的接触结构ctsb、以及形成在接触结构ctsb与导电焊盘区域112之间的连接部分中的金属硅化物层118b。

96.接触结构ctsb可以包括在竖直方向(z方向)上延伸的接触插塞116b、以及围绕接触插塞116b的绝缘插塞115b。接触插塞116b可以经由金属硅化物层118b连接到导电焊盘区域112。

97.接触结构ctsb和金属硅化物层118b可以延伸到导电焊盘区域112中,直到比导电焊盘区域112的上表面的竖直水平高度低的竖直水平高度。从导电焊盘区域112的上表面到接触结构ctsb的最下表面的竖直距离dr2可以小于导电焊盘区域112在竖直方向(z方向)上的厚度。金属硅化物层118b可以接触导电焊盘区域112的上表面和下表面。金属硅化物层118b的最上表面的竖直水平高度可以与导电焊盘区域112的上表面的竖直水平高度大致相同或相似,并且金属硅化物层118b的最下表面的竖直水平高度可以与导电焊盘区域112的下表面的竖直水平高度大致相同或相似。因此,金属硅化物层118b在竖直方向(z方向)上的高度可以与导电焊盘区域112的高度大致相同或相似。金属硅化物层118b可以接触导电焊盘区域112的上表面和下表面。

98.金属硅化物层118b可以在比导电焊盘区域112的上表面的竖直水平高度低的竖直水平高度处接触接触插塞116b的底表面。绝缘插塞115b可以包括接触插塞116b的下端与金属硅化物层118b之间的部分。

99.参照图7c,半导体器件200c可以具有与参照图4和图5a至图5c描述的半导体器件100的配置基本相同的配置。然而,半导体器件200c可以包括在导电焊盘区域112上在竖直方向(z方向)上延伸的接触结构ctsb、以及形成在接触结构ctsc与导电焊盘区域112之间的连接部分中的金属硅化物层118c。

100.接触结构ctsc可以包括在竖直方向(z方向)上延伸的接触插塞116c、以及围绕接触插塞116c的绝缘插塞115c。接触插塞116c可以经由金属硅化物层118c连接到导电焊盘区域112。

101.金属硅化物层118c可以延伸到导电焊盘区域112中,直到比导电焊盘区域112的上表面的竖直水平高度低的竖直水平高度。接触结构ctsc可以在竖直方向(z方向)上与导电焊盘区域112间隔开。导电焊盘区域112的上表面的竖直水平高度lv21可以低于构成接触结构ctsc的接触插塞116c的下表面的竖直水平高度lv22。

102.在竖直方向(z方向)上,金属硅化物层118c的最下表面可以处于比导电焊盘区域112的最上表面低的水平高度,并且金属硅化物层118c的最上表面可以处于比导电焊盘区域112的最上表面高的水平高度。金属硅化物层118c的最下表面的竖直水平高度可以高于导电焊盘区域112的下表面的竖直水平高度。金属硅化物层118c可以在比导电焊盘区域112的上表面的竖直水平高度高的竖直水平高度处接触接触插塞116c的底表面。金属硅化物层118c可以接触导电焊盘区域112的上表面。

103.图8a示出了根据本发明构思的一些实施例的半导体器件300的修改示例的截面图,图8b中的(a)是图8a中的局部区域ex31的放大截面图,并且图8b中的(b)是图8a中的局部区域ex32的放大截面图。在图8a和图8b中,与图4和图5a至图5c中的附图标记相同的附图标记可以表示相同的构件,并且省略其重复描述。

104.参照图8a和图8b,半导体器件300可以具有与参照图4和图5a至图5c描述的半导体

器件100的配置基本相同的配置。然而,在半导体器件300中,金属硅化物层118可以不在至少一个导电焊盘区域112与连接到该至少一个导电焊盘区域112的至少一个接触结构cts之间。例如,在最上导电焊盘区域112(即,多个导电焊盘区域112中的最远离衬底102的导电焊盘区域112)与连接到最上导电焊盘区域112的至少一个接触结构cts之间可以不存在金属硅化物层118。

105.换句话说,在一些示例实施例中,如图8a和图8b所示,多个导电焊盘区域112中的至少一个导电焊盘区域112可以直接接触与该至少一个导电焊盘区域112连接的接触结构cts的接触插塞116,而无需中间金属硅化物层118。

106.在半导体器件300中,多个导电焊盘区域112中的面向接触结构cts的导电焊盘区域112(其中,在导电焊盘区域112与接触结构cts之间存在金属硅化物层118)可以处于比最上导电焊盘区域112低的竖直水平高度。因此,从面向接触结构cts的导电焊盘区域112(其中,在导电焊盘区域112与接触结构cts之间存在金属硅化物层118)到衬底102的竖直距离(即,z方向距离)可以小于从最上导电焊盘区域112到衬底102的竖直距离。

107.图9是根据本发明构思的一些实施例的半导体器件400的截面图。在图9中,与图4和图5a至图5c中的附图标记相同的附图标记可以表示相同的构件,并且省略其重复描述。

108.参照图9,半导体器件400可以包括形成在存储单元区域mec的有源区ac上的存储单元阵列mca4。存储单元阵列mca4可以包括下存储堆叠sta和上存储堆叠stb,该下存储堆叠sta和该上存储堆叠stb可以在竖直方向(z方向)上与衬底102重叠。上存储堆叠stb可以与衬底102间隔开,其中下存储堆叠sta在上存储堆叠stb与衬底102之间。

109.下栅极堆叠gsa可以在衬底102的存储单元区域mec和连接区域con中。下栅极堆叠gsa可以包括多个下栅极线gl1和一体地连接到多个下栅极线gl1的多个导电焊盘区域112。下栅极堆叠gsa在存储单元区域mec中的部分可以构成下存储堆叠sta。多个导电焊盘区域112可以在连接区域con中并且可以构成阶梯状连接单元110。

110.上栅极堆叠gsb可以在下栅极堆叠gsa上方。上栅极堆叠gsb可以包括多个上栅极线gl2和一体地连接到多个上栅极线gl2的多个导电焊盘区域122。上栅极堆叠gsb在存储单元区域mec中的部分可以构成上存储堆叠stb。多个导电焊盘区域122可以在连接区域con中并且可以构成阶梯状连接单元120。

111.下存储堆叠sta可以包括被堆叠以在竖直方向(z方向)上彼此重叠的48、64或96个下栅极线gl1,并且上存储堆叠stb可以包括被堆叠以在竖直方向(z方向)上彼此重叠的48、64或96个上栅极线gl2,但是本公开不限于此。在一些示例实施例中,下栅极线gl1的数量和上栅极线gl2的数量之和可以至少是128。

112.多个下栅极线gl1和多个上栅极线gl2可以包括第一字线wl1至第n字线wln、至少一个地选择线gsl和至少一个串选择线ssl。图9示出了在多个下栅极线gl1和多个上栅极线gl2中包括两个地选择线gsl和两个串选择线ssl的情况,然而本公开不限于此。多个下栅极线gl1和多个上栅极线gl2的更详细的配置可以与参照图5a和图5b针对栅极线gl所描述的配置相同。

113.多个绝缘层156a和156b可以与衬底102、地选择线gsl、第一字线wl1至第n字线wln以及串选择线ssl交替地堆叠。换句话说,绝缘层156a、156b可以在每个地选择线gsl、每个字线wl1至wln以及每个串选择线ssl的上方和下方。绝缘层156可以在多个下栅极线gl1和

多个上栅极线gl2中的多对相邻的栅极线gl之间。衬底102上的多个绝缘层156a和156b可以包括构成下存储堆叠sta的多个绝缘层156a和构成上存储堆叠stb的多个绝缘层156b。构成下存储堆叠sta的多个绝缘层156a中的距衬底102最接近的绝缘层156a的厚度可以小于其他绝缘层156a的厚度。构成上存储堆叠stb的多个绝缘层156b中的距衬底102最远的绝缘层156b可以覆盖距衬底102最远的串选择线ssl的上表面。作为示例,多个绝缘层156a和156b可以包括氧化硅、氮化硅或sion。

114.层间绝缘层130和隔离绝缘层140可以在下存储堆叠sta和上存储堆叠stb之间。层间绝缘层130和隔离绝缘层140均可以包括氧化硅层。

115.在存储单元区域mec中,多个沟道结构180a和180b可以穿透多个下栅极线gl1、多个绝缘层156a、层间绝缘层130、隔离绝缘层140、多个上栅极线gl2和多个绝缘层156b并且在竖直方向(z方向)上延伸。多个沟道结构180a和180b可以在x方向和y方向上彼此间隔开一定间隔。一定间隔在不同方向上可以不同。

116.多个沟道结构180a和180b中的每一个可以包括穿透多个下栅极线gl1的下沟道结构180a、以及穿透多个上栅极线gl2的上沟道结构180b。下沟道结构180a和上沟道结构180b均可以包括栅极介电层182、沟道区184、掩埋绝缘层186和漏极区188。

117.构成多个下沟道结构180a的多个漏极区188可以通过下中间绝缘层187a彼此绝缘,并且构成多个上沟道结构180b的多个漏极区188可以通过上中间绝缘层187b彼此绝缘。下中间绝缘层187a和上中间绝缘层187b均可以包括氧化物层、氮化物层或其组合。上沟道结构180b的下表面可以接触下沟道结构180a的上表面。例如,上沟道表面180b可以接触下沟道结构180a的漏极区188。在水平方向上,上沟道结构180b的下表面的宽度可以小于下沟道结构180a的上表面的宽度。多个下沟道结构180a中的每一个和多个上沟道结构180b中的每一个的更详细的配置可以与参照图4以及图5a和图5b针对多个沟道结构180所描述的配置基本相同。

118.在连接区域con中,构成阶梯状连接单元110的多个导电焊盘区域112中的每一个和构成阶梯状连接单元120的多个导电焊盘区域122中的每一个在第一水平方向(x方向)上的长度可以随着距衬底102的距离增大而逐渐减小。换句话说,(距衬底102最远的)最上导电焊盘区域112和(距衬底102最近的)最下导电焊盘区域112之间的第一导电焊盘区域112可以长于在竖直方向(z方向)上在第一导电焊盘区域112上方的第二导电焊盘区域112。

119.在示例实施例中,穿透阶梯状连接单元110和阶梯状连接单元120的多个虚设沟道结构(未示出)可以在连接区域con中。多个虚设沟道结构可以支撑多个下栅极线gl1和多个上栅极线gl2以及多个导电焊盘区域112和多个导电焊盘区域122中的每一个的边缘部分,因此可以防止发生不希望的结构变形,例如弯曲或折断。

120.在存储单元区域mec中,多个位线bl可以在存储堆叠st上方。多个位线接触焊盘194可以在多个上沟道结构180b和多个位线bl之间。多个沟道结构180中的每一个的漏极区188(更具体地,上沟道结构180b的漏极区188)可以经由位线接触焊盘194连接到多个位线bl中的相应位线bl。

121.在连接区域con中,覆盖阶梯状连接单元110的绝缘层114可以在衬底102和下中间绝缘层187a之间。绝缘层114可以覆盖多个导电焊盘区域112和绝缘层156a。覆盖阶梯状上连接部分120的上绝缘层124可以在隔离绝缘层140和上中间绝缘层187b之间。上绝缘层124

可以覆盖多个导电焊盘区域122和绝缘层156b。

122.在连接区域con中,在竖直方向(z方向)上延伸的多个接触结构cts可以在构成阶梯状连接单元110的多个导电焊盘区域112上,并且可以在构成阶梯状连接单元120的多个导电焊盘区域122上。金属硅化物层118可以在多个接触结构cts和多个导电焊盘区域112之间,以及在多个接触结构cts和多个导电焊盘区域122之间。多个接触结构cts中的每一个可以包括在竖直方向(z方向)上延伸的接触插塞116、以及围绕接触插塞116的绝缘插塞115。多个接触结构cts中的每一个的接触插塞116可以经由多个金属硅化物层118连接到导电焊盘区域112和122。多个导电焊盘区域112和122、多个金属硅化物层118和多个接触结构cts之间的连接部分的更详细的配置和各种修改可以与参照图5a至图5c以及图7a至图7c描述的金属硅化物层118、118a、118b和118c、导电焊盘区域112以及接触结构cts、ctsa、ctsb和ctsc之间的连接部分的配置和各种修改基本相同。

123.在一些示例实施例中,与参照图8a和图8b的半导体器件400给出的描述类似,金属硅化物层118可以不在至少一个导电焊盘区域112、122与连接到该至少一个导电焊盘区域112、122的接触结构cts之间的连接部分处。例如,金属硅化物层118可以不在距衬底102最远的最上导电焊盘区域122与连接到最上导电焊盘区域122的接触结构cts之间。

124.连接到阶梯状连接单元110的多个导电焊盘区域112中的相应导电焊盘区域112的多个接触结构cts中的每一个接触结构cts可以在竖直方向上从相应导电焊盘区域112延伸至第一竖直水平高度lv41,该第一竖直水平高度lv41高于下存储堆叠sta且低于上存储堆叠stb。多个接触结构cts中的至少一些可以从导电焊盘区域112穿透绝缘层114和下中间绝缘层187a。连接到距衬底102最远的最上导电焊盘区域112的接触结构cts可以从导电焊盘区域112穿透绝缘层156a和下中间绝缘层187a,并且可以延伸到第一竖直水平高度lv41而不穿透绝缘层114。

125.多个下布线层ma可以在多个下接触插塞116上。多个下布线层ma可以连接到多个接触结构cts,并且在第一竖直水平高度lv41处在水平方向上延伸。多个下布线层ma可以经由多个接触结构cts电连接到多个下栅极线gl1中的至少一个下栅极线gl1。在连接区域con中,多个下布线层ma可以通过层间绝缘层130彼此绝缘。

126.连接到阶梯状连接单元120的多个导电焊盘区域122中的相应导电焊盘区域122的多个接触结构cts中的每一个接触结构cts可以在竖直方向上从相应导电焊盘区域122延伸到第二竖直水平高度lv42,该第二竖直水平高度lv42高于上存储堆叠stb。多个接触结构cts中的至少一些可以从导电焊盘区域122穿透上绝缘层124、上中间绝缘层187b和绝缘层193。连接到距衬底102最远的最上导电焊盘区域122的接触结构cts可以从导电焊盘区域122穿透绝缘层156b、上中间绝缘层187b和绝缘层193,并且可以延伸到第二竖直水平高度lv42,而不穿透上绝缘层124。第二竖直水平高度lv42可以高于穿透上存储堆叠stb的多个上沟道结构180b的最上表面的水平高度。

127.多个上布线层mb可以在连接到多个导电焊盘区域122的多个接触结构cts上。多个上布线层mb可以连接到多个接触结构cts,并且沿第二竖直水平高度lv42在水平方向上延伸。多个上布线层mb可以经由多个接触结构cts和金属硅化物层118电连接到多个上栅极线gl2中的至少一个上栅极线gl2。连接区域con中的多个上布线层mb可以形成在与存储单元区域mec中的多个位线bl相同的水平高度处。连接区域con中的多个上布线层mb可以通过上

层间绝缘层195彼此绝缘。

128.在一些示例实施例中,不同于图9所示,与阶梯状连接单元110的多个导电焊盘区域112连接的多个接触结构cts中的每个接触结构cts可以穿透绝缘层114、下中间绝缘层187a、中间绝缘层130、分离绝缘层140、上绝缘层124、上中间绝缘层187b和绝缘层193,并且可以从相应导电焊盘区域112延伸到第二竖直水平高度lv42。在这种情况下,多个上布线层mb中的一些可以经由多个接触结构cts和金属硅化物层118电连接到多个下栅极线gl1中的至少一个下栅极线gl1,并且可以省略多个下布线层ma。

129.多个接触结构cts、多个下布线层ma和多个上布线层mb均可以包括钨、钛、钽、铜、铝、氮化钛、氮化钽、氮化钨或其组合。

130.可以在外围电路区域pert中形成多个电路ct4。多个电路ct4可以形成在等于或高于衬底102的竖直水平高度的竖直水平高度处。多个电路ct4的更详细的配置可以与参照图5a至图5c针对多个电路ct给出的描述基本相同。

131.多个下外围接触结构pts1可以在外围电路区域peri中。多个下外围接触结构pts1可以从外围晶体管tr穿透绝缘层114,并且在竖直方向(z方向)上延伸到第一竖直水平高度lv41。多个下外围接触结构pts1中的每一个可以包括在竖直方向(z方向)上延伸的外围接触插塞p116、以及围绕外围接触插塞p116的外围绝缘插塞p115。

132.连接到多个下外围接触结构pts1的多个下外围布线层pma可以在多个下外围接触结构pts1上。多个下外围布线层pma可以在第一竖直水平高度lv41处在水平方向上延伸。多个下外围布线层pma中的每一个可以经由多个下外围接触结构pts1中的相应一个下外围接触结构pts1连接到外围栅极pg或外围源/漏区psd中的一个。多个下外围布线层pma中的至少一些可以连接到外围电路区域peri中的其他电路或布线。多个下外围布线层pma可以通过层间绝缘层130彼此绝缘。

133.连接到多个下外围布线层pma的多个上外围接触结构pts2可以在多个下外围布线层pma上。多个上外围接触结构pts2可以从多个下外围布线层pma穿透隔离绝缘层140和上绝缘层124,并且可以延伸到第二竖直水平高度lv42。多个上外围接触结构pts2中的每一个可以包括在竖直方向(z方向)上延伸的外围接触插塞p116、以及围绕外围接触插塞p116的外围绝缘插塞p115。

134.连接到多个上外围接触结构pts2的多个上外围布线层pmb可以在多个上外围接触结构pts2上。多个上外围布线层pmb可以在第二竖直水平高度lv2(即,与形成在连接区域con中的多个上布线层mb的水平高度相同的水平高度)处在水平方向上延伸。多个上外围布线层pmb中的每一个可以连接到外围电路区域peri中的其他电路或布线。多个上外围布线层pmb可以通过层间绝缘层195彼此绝缘。

135.多个下外围布线层pma和多个上外围布线层pmb均可以包括钨、钛、钽、铜、铝、氮化钛、氮化钽、氮化钨或其组合。

136.图10是根据本发明构思的一些实施例的半导体器件500a的截面图。

137.参照图10,半导体器件500a可以具有与参照图4和图5a至图5c描述的半导体器件100的配置基本相同的配置。然而,半导体器件500a可以包括在比衬底102的水平高度低的水平高度处形成的外围电路区域peri5。

138.存储单元区域mec和连接区域con可以与外围电路区域peri5竖直地重叠。在连接

区域con中,在竖直方向(z方向)上延伸的多个接触结构cts可以在阶梯状连接单元110的多个导电焊盘区域112上。多个金属硅化物层118可以位于多个接触结构cts和多个导电焊盘区域112之间的多个连接部分处。

139.外围电路区域peri5可以包括衬底102下方的外围电路板502、以及外围电路板502与衬底102之间的多个电路ct5。存储单元区域mec和连接区域con可以在衬底102的第一表面上,并且外围电路区域peri5可以在衬底102的与第一表面相对的第二表面上。外围电路板502和电路ct5的更详细的配置可以与参考图5a和图5b针对衬底102和多个电路ct给出的描述基本相同。

140.外围电路有源区pac5可以通过元件隔离层504限定在外围电路板502上。可以在外围电路有源区pac5上形成多个晶体管tr5。多个晶体管tr5中的每一个可以包括外围栅极pg5、以及在外围有源区pac5中形成在外围栅极pg5的两侧的外围源/漏区psd5。在一些示例实施例中,诸如电阻器和电容器的单元元件还可以布置在外围电路区域peri5中。可以在多个晶体管tr5上形成外围层间绝缘层510。外围层间绝缘层510可以包括氧化硅、sion、siocn等。

141.外围电路区域peri5可以包括多个外围电路布线层508和多个外围电路接触部509。多个外围电路布线层508中的一些可以电连接到多个晶体管tr5。多个外围电路接触部509可以将多个外围电路布线层508中的一些外围电路布线层508彼此连接。多个外围电路布线层508和多个外围电路接触部509可以被外围层间绝缘层510覆盖。多个外围电路布线层508中的一些外围电路布线层508可以面向存储堆叠st,其中衬底102在所述一些外围电路布线层508与存储堆叠st之间。

142.多个外围电路布线层508和多个外围电路接触部509均可以包括金属、导电金属氮化物、金属硅化物或其组合。例如,多个外围电路布线层508和多个外围电路接触部509可以包括导电材料,诸如钨、钼、钛、钴、钽、镍、硅化钨、硅化钛、硅化钴、硅化钽和硅化镍。在图10中,示出了多个外围电路布线层508具有竖直方向(z方向)上的三层布线结构,但是本公开不限于此。例如,多个外围电路布线层508可以具有多层布线结构,该多层布线结构包括两个层或四个层或更多个层。

143.在半导体器件500a中,可以在衬底102中形成通孔102h。通孔102h可以填充有衬底掩埋绝缘层512。衬底掩埋绝缘层512可以包括氧化硅层。

144.在半导体器件500a中,连接区域con中的布线结构可以经由在竖直方向(z方向)上延伸的外围接触结构pts5与外围电路区域peri5中的多个外围电路布线层508电连接。外围接触结构pts5可以包括在竖直方向(z方向)上延伸的外围接触插塞p116、以及围绕外围接触插塞p116的外围绝缘插塞p115。连接区域con和外围布线层pml中的多个布线层ml中的至少一些布线层ml可以经由外围接触结构pts5电连接到外围电路区域peri5中的多个外围电路布线层508。

145.外围接触结构pts5可以从多个外围电路布线层508中的一个外围电路布线层508穿透外围层间绝缘层510和衬底掩埋绝缘层512,并且可以在竖直方向(z方向)上延伸到外围布线层pml。外围接触结构pts5可以经由通孔102h穿透衬底102,并且可以被通孔102h中的衬底掩埋绝缘层512围绕。

146.图11是根据本发明构思的一些实施例的半导体器件500b的截面图。在图11中,与

图5a、图5b和图10中的附图标记相同的附图标记可以表示相同的构件,并且省略其重复描述。

147.参照图11,半导体器件500b可以具有与参照图10针对半导体器件500a所描述的配置基本相同的配置。然而,半导体器件500b还可以包括金属硅化物层p118,金属硅化物层p118形成在外围接触结构pts5和与外围接触结构pts5连接的外围电路布线层508之间的连接部分处。外围接触结构pts5可以经由金属硅化物层p118连接到外围电路布线层508。金属硅化物层p118可以具有与参照图5a至图5c针对金属硅化物层118给出的描述基本相同的配置。

148.在一些实施例中,包括在金属硅化物层p118中的金属可以与包括在外围接触结构pts5中的金属相同。在其他一些实施例中,包括在金属硅化物层p118中的金属和包括在外围接触结构pts5中的金属可以是彼此不同的金属。

149.金属硅化物层p118、与金属硅化物层p118接触的外围电路布线层508以及外围接触结构pts5之间的连接部分的更详细的配置和各种修改可以与参照图5a至图5c以及图7a至图7c针对金属硅化物层118、118a、118b和118c、导电焊盘区域112以及接触结构cts、ctsa、ctsb和ctsc之间的连接部分给出的描述基本相同。

150.图12是根据本发明构思的一些实施例的半导体器件600的截面图。在图12中,与图5a、图5b和图10中的附图标记相同的附图标记可以表示相同的构件,并且省略其重复描述。

151.参照图12,半导体器件600可以具有芯片对芯片(c2c)结构。c2c结构可以表示这样的结构,其中,在包括单元区域cell的上芯片被制造在第一晶片上并且包括外围电路区域peri的下芯片被制造在不同于第一晶片的第二晶片上之后,上芯片和下芯片通过使用接合方法彼此连接。例如,接合方法可以包括:将在包括单元区域cell在内的上芯片的最上金属层上形成的接合金属与在包括外围电路区域peri在内的下芯片的最上金属层上形成的接合金属电接合的方法。在一些示例实施例中,当接合金属包括铜(cu)时,接合方法可以包括cu-cu接合方法。在其他示例实施例中,接合金属可以包括铝或钨。

152.在半导体器件600中,外围电路区域peri和单元区域cell均可以包括焊盘接合区域pa。单元区域cell还可以包括连接区域con和存储单元区域mec。

153.外围电路区域peri可以包括第一衬底610、层间绝缘层615、形成在第一衬底610上的多个电路元件620a、620b和620c、分别与多个电路元件620a、620b和620c连接的第一金属层630a、630b和630c、以及分别形成在第一金属层630a、630b和630c上的第二金属层640a、640b和640c。在一些示例实施例中,第一金属层630a、630b和630c可以包括钨,并且第二金属层640a、640b和640c可以包括cu。

154.在一些示例实施例中,还可以在第二金属层640a、640b和640c上形成至少一个金属层。形成在第二金属层640a、640b和640c上的至少一个金属层中的至少一些可以包括铝。

155.层间绝缘层615可以覆盖多个电路元件620a、620b和620c、第一金属层630a、630b和630c以及第二金属层640a、640b和640c。层间绝缘层615可以包括氧化硅、氮化硅或其组合。

156.下接合金属671b和672b可以在以下区域中的第二金属层640b上,即,下接合金属671b和672b在竖直方向(z方向)上与外围电路区域peri中的连接区域con重叠的区域。在连接区域con中,可以通过使用接合方法将外围电路区域peri的下接合金属671b和672b电连

接到单元区域cell的上接合金属371b和372b。下接合金属671b和672b以及上接合金属371b和372b可以包括铝、cu或钨。

157.单元区域cell可以包括第二衬底310和公共源极线320。包括多个栅极线gl和连接到多个栅极线gl的多个导电焊盘区域112在内的栅极堆叠gs可以在第二衬底310上。在单元区域cell中,连接区域con和存储单元区域mec中的结构的详细配置可以与参考图5a至图5c给出的描述相同。

158.在存储单元区域mec中,沟道结构180可以经由位线接触焊盘194和位线bl连接到上接合金属371c和372c。位线bl可以经由上接合金属371c和372c电连接到包括在外围电路区域peri中的电路元件,例如,提供页缓冲器393的电路元件620c。上接合金属371c和372c可以连接到下接合金属671c和672c,该下接合金属671c和672c连接到页缓冲器393的电路元件620c。

159.在连接区域con中,多个导电焊盘区域112中的每一个可以在与第二衬底310的上表面平行的方向上延伸,并且可以经由金属硅化物层118连接到接触结构cts。在多个接触结构cts中的每一个中,与连接到金属硅化物层118的第一端相对的第二端可以连接到上接合金属371b和372b。多个接触结构cts可以经由单元区域cell的上接合金属371b和372b以及外围电路区域peri的下接合金属671b和672b连接到外围电路区域peri。

160.接触结构cts中的每一个可以电连接到外围电路区域peri中的提供行解码器394的电路元件620b。在示例实施例中,提供行解码器394的电路元件620b的工作电压可以不同于提供页缓冲器393的电路元件620c的工作电压。例如,提供页缓冲器393的电路元件620c的工作电压可以大于提供行解码器394的电路元件620b的工作电压。

161.多个公共源极线接触插塞380可以在焊盘接合区域pa中。多个公共源极线接触插塞380中的每一个可以电连接到公共源极线320。多个公共源极线接触插塞380中的每一个可以包括金属、金属化合物、多晶硅或其组合。金属层350a可以连接到公共源极线接触插塞380的与连接到公共源极线320的一端相对的另一端。金属层350a可以连接到上金属图案371a和372a。上金属图案371a和372a中的每一个可以连接到外围电路区域peri的下金属图案671a、672a和673a中的对应一个。

162.多个i/o焊盘305和605可以在焊盘接合区域pa中。可以在第一衬底610下方形成覆盖第一衬底610的下表面的下绝缘层601,并且可以在下绝缘层601上形成第一i/o焊盘605。第一i/o焊盘605可以经由穿透下绝缘层201和第一衬底610的第一i/o接触插塞603连接到外围电路区域peri中的多个电路元件620a、620b和620c中的至少一个电路元件。绝缘层612可以在第一i/o接触插塞603和第一衬底610之间,并且可以将第一i/o接触插塞603与第一衬底610电分离。

163.覆盖第二衬底310的上表面的上绝缘层301可以在第二衬底310上。第二i/o焊盘305可以在上绝缘层301上。第二i/o 305可以经由第二i/o接触插塞303连接到外围电路区域peri中的多个电路元件620a、620b和620c中的至少一个。

164.第二i/o接触插塞303可以与第二衬底310和公共源极线320间隔开。第二输入/输出焊盘305可以在竖直方向(z方向)上不与多个导电焊盘区域112重叠。第二i/o接触插塞303可以穿透层间绝缘层315和上绝缘层301,并且可以连接到第二i/o焊盘305。

165.在一些示例实施例中,可以省略第一i/o焊盘605和第二i/o焊盘305中的任一个。

166.在焊盘接合区域pa中,形成在单元区域cell的最上金属层上的上金属图案371a和372a可以连接到形成在外围电路区域peri的最上金属层上的对应下金属图案671a、672a和673a。形成在外围电路区域peri的最上金属层上的下金属图案673a可以不连接到外围电路区域peri中的单独的接触部。在一些实施例中,响应于形成在焊盘接合区域pa中的外围电路区域peri的最上金属层上的下金属图案,具有与外围电路区域peri的下金属图案的形状相同的形状的上金属图案可以形成在单元区域cell的上金属层上。

167.下接合金属671b和672b可以形成在连接区域con的第二金属层640b上。下接合金属671b和672b可以通过使用接合方法而电连接到单元区域cell的上接合金属371b和372b。

168.在存储单元区域mec中,与形成在外围电路区域peri的最上金属层上的下接合金属651和652相对应地,上金属图案392可以在单元区域cell的最上金属层上。

169.根据参考图4至图12的半导体器件100、200a、200b、200c、300、400、500a、500b和600,可以通过在导电焊盘区域与连接到导电焊盘区域的接触插塞之间的连接部分处形成金属硅化物层来减小导电焊盘区域与接触插塞之间的接触电阻,即使在包括三维布置的存储单元在内的半导体器件中,为了提高集成度,字线的层数增大,并且连接到字线的接触部的数量和布线的数量增大。因此,可以在半导体器件中保持良好的电特性,并提高半导体器件的可靠性。

170.图13是根据本发明构思的一些实施例的包括半导体器件1100的电子系统1000的示意图。

171.参照图13,根据本发明构思的一些示例实施例的电子系统1000可以包括半导体器件1100和电连接到半导体器件1100的控制器1200。电子系统1000可以包括包含一个或多个半导体器件1100的存储器件、或者包含该存储器件的电子设备。例如,电子系统1000可以包括包含至少一个半导体器件1100的固态驱动设备(ssd)、通用串行总线(usb)、计算系统、医疗设备或通信设备。

172.半导体器件1100可以包括非易失性存储器件。例如,半导体器件1100可以包括nand闪存器件,其包括以上参照图4至图12针对半导体器件100、200a、200b、200c、300、400、500a、500b和600所描述的结构中的至少一种。半导体器件1100可以包括第一结构1100f和在第一结构1100f上的第二结构1100s。在示例实施例中,第一结构1100f可以紧接第二结构1100s。第一结构1100f可以包括外围电路结构,该外围电路结构包括解码器电路1110、页缓冲器1120和逻辑电路1130。第二结构1100s可以包括存储单元结构,该存储单元结构包括位线bl、公共源极线csl、多个字线wl、第一上栅极线ul1和第二上栅极线ul2、第一下栅极线ll1和第二下栅极线ll2、以及位线bl与公共源极线csl之间的多个存储单元串cstr。

173.在第二结构1100s中,多个存储单元串cstr中的每一个可以包括与公共源极线csl相邻的下晶体管lt1和lt2、与位线bl相邻的上晶体管ut1和ut2、以及下晶体管lt1和lt2与上晶体管ut1和ut2之间的多个存储单元晶体管mct。根据示例实施例,下晶体管lt1和lt2的数量以及上晶体管ut1和ut2的数量可以被不同地修改。

174.在一些示例实施例中,上晶体管ut1和ut2可以包括串选择晶体管sst,并且下晶体管lt1和lt2可以包括地选择晶体管gst。多个下栅极线ll1和ll2中的每一个可以分别包括下晶体管lt1和lt2的栅电极。字线wl可以包括存储单元晶体管mct的栅电极,并且上栅极线ul1和ul2可以分别是上晶体管ut1和ut2的栅电极。

175.公共源极线csl、多个下栅极线ll1和ll2、多个字线wl以及多个上栅极线ul1和ul2可以经由延伸到第一结构1100f中的第二结构的多个第一连接布线1115而电连接到解码器1110。多个位线bl可以经由延伸到第一结构1100f中的第二结构1100s的多个第二连接线1125而电连接到页缓冲器1120。

176.在第一结构1100f中,解码器电路1110和页缓冲器1120可以对多个存储单元晶体管mct中的至少一个执行控制操作。解码器电路1110和页缓冲器1120可以由逻辑电路1130控制。

177.半导体器件1100可以经由电连接到逻辑电路1130的i/o焊盘1101与控制器1200通信。i/o焊盘1101可以经由从第一结构1100f延伸到和/或延伸穿过第二结构1100s的i/o连接线1135而电连接到逻辑电路1130。

178.控制器1200可以包括处理器1210、nand控制器1220和主机接口1230。根据一些实施例,电子系统1000可以包括多个半导体器件1100,并且在这种情况下,控制器1200可以控制多个半导体器件1100。

179.处理器1210可以控制包括控制器1200的电子系统1000的整体操作。处理器1210可以根据特定固件进行操作,并且可以通过控制nand控制器1220来访问半导体器件1100。nand控制器1220可以包括处理与半导体器件1100的通信的nand接口1221。经由nand接口1221,可以发送用于控制半导体器件1100的控制命令、将被写入半导体器件1100的多个存储单元晶体管mct的数据、将从半导体器件1100的多个存储单元晶体管mct读取的数据等。主机接口1230可以提供电子系统1000和外部主机(未示出)之间的通信功能。当经由主机接口1230从外部主机接收到控制命令时,处理器1210可以响应于该控制命令来控制半导体器件1100。

180.图14是根据本发明构思的一些实施例的包括半导体器件的电子系统2000的示意性透视图。

181.参照图14,根据本发明构思的一些示例实施例的电子系统2000可以包括主衬底2001、安装在主衬底2001上的控制器2002、一个或多个半导体封装2003以及dram 2004。半导体封装2003和dram 2004可以通过形成在主衬底2001上的多个布线图案2005连接到控制器2002。

182.主衬底2001可以包括连接器2006,该连接器2006包括耦合到外部主机(未示出)的多个引脚。连接器2006中的多个引脚的数量和布置可以根据电子系统2000与外部主机之间的通信接口而变化。在示例实施例中,电子系统2000可以根据诸如usb接口、外围组件互连(pci)快速(pci-e)接口、串行高级技术附件(sata)接口、以及用于通用闪存(ufs)接口的m-phy中的任一个与外部主机通信。在示例实施例中,电子系统2000可以通过经由连接器2006从外部主机供应的电力来操作。电子系统2000还可以包括电力管理集成电路pmic,该电力管理集成电路pmic将从外部主机供应的电力分配给控制器2002和半导体封装2003。

183.控制器2002可以将数据写入半导体封装2003,或者从半导体封装2003读取数据,并且可以提高电子系统2000的操作速度。

184.dram 2004可以包括用于减小作为数据存储空间的半导体封装2003与外部主机之间的速度差的缓冲存储器。电子系统2000中包括的dram 2004还可以用作高速缓冲存储器,并且可以在对半导体封装2003的控制操作中提供用于临时存储数据的空间。当dram 2004

包括在电子系统2000中时,除了用于控制半导体封装2003的nand控制器之外,控制器2002还可以包括用于控制dram 2004的dram控制器。

185.半导体封装2003可以包括彼此间隔开的第一半导体封装2003a和第二半导体封装2003b。第一半导体封装2003a和第二半导体封装2003b中的每一个可以包括:包含多个半导体芯片2200的半导体封装。第一半导体封装2003a和第二半导体封装2003b中的每一个可以包括封装衬底2100、封装衬底2100上的多个半导体芯片2200、多个半导体芯片2200中的每一个半导体芯片的下表面上的粘合层2300、将多个半导体芯片2200电连接到封装衬底2100的连接结构2400、以及覆盖多个半导体芯片2200和连接结构2400的模制层2500。

186.封装衬底2100可以包括印刷电路板,该印刷电路板包括多个封装上焊盘2130。多个半导体芯片2200中的每一个可以包括i/o焊盘2210。i/o焊盘2210可以对应于图13中的i/o焊盘1101。多个半导体芯片2200中的每一个可以包括多个栅极堆叠3210和多个沟道结构3220。多个半导体芯片2200中的每一个可以包括参照图4至图12的半导体器件100、200a、200b、200c、300、400、500a、500b和600中的至少一个。

187.在一些示例实施例中,连接结构2400可以包括将i/0焊盘2210电连接到封装上焊盘2130的接合线。因此,在第一半导体封装2003a和第二半导体封装2003b中,多个半导体芯片2200可以通过接合线方法彼此电连接,并且可以与封装衬底2100的封装上焊盘2130电连接。根据一些实施例,在第一半导体封装2003a和第二半导体封装2003b中,多个半导体芯片2200可以通过包括硅通孔tsv的连接结构而非接合线式的连接结构2400彼此电连接。

188.在一些示例实施例中,控制器2002和多个半导体芯片2200可以被包括在一个封装中。在一些示例实施例中,控制器2002和多个半导体芯片2200可以安装在与主衬底2001不同的单独的插入衬底上,并且控制器2002和多个半导体芯片2200可以通过形成在插入衬底上的布线而彼此连接。

189.图15是根据本发明构思的一些实施例的半导体封装2003的示意性截面图。在图15中,更详细地示出了沿图14中的线ii-ii’截取的截面图中的配置。

190.参照图15,在半导体封装2003中,封装衬底2100可以包括印刷电路板。封装衬底2100可以包括封装衬底本体单元2120、封装衬底本体单元2120的上表面上的多个封装上焊盘2130(参照图14)、布置在封装衬底本体单元2120的下表面上或通过封装衬底本体单元2120的下表面暴露的多个下焊盘2125、以及多个内部布线2135,所述多个内部布线2135将多个上焊盘2130与封装衬底本体单元2120中的多个下焊盘2125电连接。多个上焊盘2130可以电连接到多个连接结构2400。多个下焊盘2125可以经由多个导电连接单元2800连接到图14所示的电子系统2000的主衬底2001上的多个布线图案2005。

191.多个半导体芯片2200中的每一个可以包括半导体衬底3010、以及顺序地堆叠在半导体衬底3010上的第一结构3100和第二结构3200。第一结构3100可以包括外围电路区域,该外围电路区域包括多个外围布线3110。第二结构3200可以包括公共源极线3205、公共源极线3205上的栅极堆叠3210、穿透栅极堆叠3210的沟道结构3220、电连接到沟道结构3220的位线3240以及栅极堆叠3210。栅极堆叠3210可以包括多个字线(图13中的wl)以及一体地连接到多个字线wl的多个导电焊盘区域112。另外,多个半导体芯片2200中的每一个可以包括与栅极堆叠3210的多个导电焊盘区域112电连接的多个接触结构cts、多个导电焊盘区域112、以及多个导电焊盘区域112与多个接触结构cts之间的多个金属硅化物层118。多个导

电焊盘区域112中的每一个可以经由金属硅化物层118连接到接触结构cts。多个导电焊盘区域112、多个金属硅化物层118和多个接触结构cts之间的连接部分的更详细的配置和各种修改可以分别与参照图5a至图5c以及图7a至图7c描述的金属硅化物层118、118a、118b和118c、导电焊盘区域112以及接触结构cts、ctsa、ctsb和ctsc之间的连接部分的配置和各种修改基本相同。

192.多个半导体芯片2200中的每一个可以包括贯通布线3245,该贯通布线3245与第一结构3100的多个外围布线3110电连接并延伸到第二结构3200中。贯通布线3245可以在栅极堆叠3210的外部。在一些示例实施例中,半导体封装2003还可以包括穿透栅极堆叠3210的贯通布线。多个半导体芯片2200中的每一个还可以包括与第一结构3100的多个外围布线3110电连接的i/o焊盘(图14中的2210)。

193.图16是根据本发明构思的一些实施例的半导体封装2003a的示意性截面图。图16示出了与沿图14中的线ii-ii’截取的截面相对应的部分的配置。

194.参照图16,半导体封装2003a可以具有与参照图15描述的半导体封装2003基本相同的配置。然而,半导体封装2003a可以包括多个半导体芯片2200a。多个半导体芯片2200a中的每一个可以包括半导体衬底4010、半导体衬底4010上的第一结构4100、以及第一结构4100上的通过晶片接合方法接合到第一结构的第二结构4200。

195.第一结构4100可以包括外围电路区域,该外围电路区域包括外围布线4110和多个第一接合结构4150。第二结构4200可以包括公共源极线4205、公共源极线4205和第一结构4100之间的栅极堆叠4210、以及穿透栅极堆叠4210的沟道结构4220。栅极堆叠4210可以包括多个字线(图13中的wl)以及一体地连接到多个字线的多个导电焊盘区域112。另外,多个半导体芯片2200a中的每一个可以包括与栅极堆叠3210的多个导电焊盘区域112电连接的多个接触结构cts、以及多个导电焊盘区域112与多个接触结构cts之间的多个金属硅化物层118。多个导电焊盘区域112中的每一个可以经由金属硅化物层118连接到接触结构cts。多个导电焊盘区域112、多个金属硅化物层118和多个接触结构cts之间的连接部分的更详细的配置和各种修改可以与参照图5a至图5c以及图7a至图7c描述的金属硅化物层118、118a、118b和118c、导电焊盘区域112以及接触结构cts、ctsa、ctsb和ctsc之间的连接部分的配置和各种修改基本相同。

196.另外,多个半导体芯片2200a中的每一个可以包括多个第二接合结构4250,所述多个第二接合结构4250中的每一个电连接到栅极堆叠4210的多个字线(图13中的wl)。例如,多个第二接合结构4250中的每一个可以经由与沟道结构4220电连接的位线4240和与字线(图13中的wl)电连接的接触结构cts而连接到沟道结构4220和字线(图1中的wl)。

197.第一结构4100的多个第一接合结构4150和第二结构4200的多个第二接合结构4250可以彼此接触并接合。多个第一接合结构4150和多个第二接合结构4250彼此接合的部分可以包括例如cu。

198.图15所示的多个半导体芯片2200和图16所示的多个半导体芯片2200a可以通过多个连接结构2400(参照图14)以接合线的形式彼此电连接。在一些示例实施例中,图15所示的多个半导体芯片2200和图16所示的多个半导体芯片2200a可以经由包括贯通电极tsv在内的连接结构而彼此电连接。

199.图17a至图17e是示出了根据本发明构思的一些实施例的根据工艺顺序的半导体

器件100的制造方法的截面图。在本示例中,描述了图4和图5a至图5c所示的半导体器件100的制造方法。

200.参照图17a,可以在衬底102的存储单元区域mec中限定有源区ac,并且可以在外围电路区域peri中限定外围有源区pac。外围有源区pac可以由元件隔离层103限定。

201.多个绝缘层156和多个牺牲层pl可以在衬底102的存储单元区域mec和连接区域con中逐个交替地堆叠,并且可以在外围电路区域peri中形成外围晶体管tr。作为示例,多个牺牲层pl可以包括氮化硅、碳化硅或多晶硅。多个牺牲层pl中的每一个可以确保用于在后续工艺中形成栅极堆叠gs的空间(参考图17c)。

202.参照图17b,在去除了多个绝缘层156和多个牺牲层pl中的每一个的一部分使得多个绝缘层156和多个牺牲层pl形成阶梯状结构stp之后,可以在衬底102上形成覆盖阶梯状结构stp和外围晶体管tr的绝缘层114。

203.接下来,可以在存储单元区域mec中形成穿透多个绝缘层156和多个牺牲层pl且在竖直方向(z方向)上延伸的多个下沟道孔180h,并且可以通过在多个下沟道孔180h中的每一个中形成栅极介电层182、沟道区184和掩埋绝缘层186来形成多个下沟道孔掩埋结构。

204.接下来,可以形成中间绝缘层187,该中间绝缘层187覆盖存储单元区域mec、连接区域con和外围电路区域peri中的多个下沟道孔掩埋结构、阶梯状结构stp和绝缘层114,可以通过在中间绝缘层187中形成多个接触孔187h来暴露多个下沟道孔掩埋结构的上表面,并且可以通过在多个接触孔187h中形成多个漏极区188来形成沟道结构180。中间绝缘层187可以具有存储单元区域mec、连接区域con和外围电路区域peri上方的平坦化的上表面。

205.参照图17c,在形成了穿透多个绝缘层156和多个牺牲层pl(参照图17b)且暴露衬底102(参照图4和图5b)的多个字线切割区域wlc之后,通过经由多个字线切割区域wlc将杂质离子注入到衬底102中来形成多个公共源极区106(参考图5b),然后可以用多个栅极线gl和多个导电焊盘区域112代替多个牺牲层pl(参考图17b)。在连接区域con中,多个导电焊盘区域112可以构成阶梯状连接单元110。

206.在一些示例实施例中,在通过选择性地去除通过多个字线切割区域wlc暴露的多个牺牲层pl(参考图17b)以用多个下字线wla替代多个牺牲层pl(参照图17b)以在多个绝缘层156之间制备空的空间之后,通过在空的空间中掩埋导电材料,可以形成多个栅极线gl和多个导电焊盘区域112。

207.此后,如图5b所示,在多个字线切割区域wlc中的每一个中,可以通过形成绝缘间隔物192和公共源极线csl来形成字线切割结构wcs。绝缘间隔物192可以包括氧化硅、氮化硅、sion、siocn、sicn或其组合。公共源极线csl可以包括诸如钨、铜和铝的金属、诸如氮化钛和氮化钽的导电金属氮化物、诸如钛和钽的过渡金属、或其组合。在一些实施例中,用于减小接触电阻的金属硅化物层(未示出)可以在公共源极区106和公共源极线csl之间。金属硅化物层可以包括硅化钴,但是本公开不限于此。在一些实施例中,当公共源极线(未示出)被掩埋在衬底102中时,多个字线切割区域wlc可以仅填充有绝缘材料,并且可以省略公共源极线csl的形成过程。

208.参照图17d,当在图17c的结果上形成上绝缘层193之后,可以形成多个位线接触焊盘194,该多个位线接触焊盘194穿透上绝缘层193并且连接到存储单元区域mec中的多个沟道结构180。绝缘层114、中间绝缘层187和上绝缘层193可以构成绝缘结构ins。

209.可以通过使用掩模图案(未示出)作为蚀刻掩模,各向异性地蚀刻连接区域con和外围电路区域peri中的绝缘结构ins来形成暴露连接区域con中的多个导电焊盘区域112的多个第一接触孔h11,并且可以形成多个第二接触孔h12,从而暴露外围电路区域peri中的外围栅极pg和外围源/漏区psd。可以同时形成多个第一接触孔h11和多个第二接触孔h12。

210.参照图17e,可以在通过连接区域con中的多个第一接触孔h11中的每一个第一接触孔h11暴露的导电焊盘区域112的表面上形成金属硅化物层118,并且可以在多个第一接触孔h11中的每一个中的金属硅化物层118上形成接触结构cts。另外,通过在外围电路区域peri中的多个第二下接触孔h12中顺序地形成外围绝缘插塞p115和外围接触插塞p116,可以形成外围接触结构pts。

211.图18a至图18e是根据工艺顺序示出的截面图,以根据图17e中的工艺的更详细地描述以下工艺:在导电焊盘区域112的表面上形成金属硅化物层118,并且在连接区域con中的金属硅化物层118上形成接触结构cts。在图18a至图18e中,根据工艺顺序示出了与图17d中表示为ex2的局部区域相对应的部分的放大截面配置。

212.参照图18a,可以如参照图17d所描述的那样形成多个第一接触孔h11。硬掩模hm可以用作蚀刻掩模以形成多个第一接触孔h11。硬掩模hm可以包括能够在蚀刻绝缘结构ins时提供蚀刻选择性的材料。例如,硬掩模hm可以包括氮化硅层、多晶硅层、旋涂硬掩模(soh)或其组合,但是不限于此。

213.接下来,通过预处理已经在包括o2或氧等离子体的气氛trt中形成第一接触孔h11的结果,可以在通过第一接触孔h11暴露的导电焊盘区域112的表面上形成包括金属的层117。

214.例如,当导电焊盘区域112包括钨层时,在形成第一接触孔h11之前,导电焊盘区域112可以处于诸如wf6基气体、wc16基气体之类的含钨气体从构成导电焊盘区域112的钨层中脱气的状态。在该状态下,如参照图17d所述,当在形成使多个导电焊盘区域112暴露的多个第一接触孔h11之后在包括o2或氧等离子体在内的气氛trt中进行预处理时,包括氧化钨(wo

x

,0<x≤3)在内的含金属层117可以形成在通过第一接触孔h11暴露的导电焊盘区域112的表面上。

215.参照图18b,在通过剥离工艺清洁图18a的结果之后,可以形成绝缘衬层115l,绝缘衬层115l符合且覆盖第一接触孔h11的内表面。

216.在示例实施例中,绝缘衬层115l可以包括氮化硅层、氧化硅层或其组合。为了形成绝缘衬层115l,可以使用一氯硅烷(sih3cl)、二氯硅烷(sih2cl2)、三氯硅烷(sihcl3)、四氯化硅(sicl4)、六氯乙硅烷(si2cl6)或其组合作为硅(si)前驱体,但是本公开不限于此。当绝缘衬层115l包括氮化硅层时,可以将nh3气体用作氮化物气体以形成绝缘衬层115l,但是本发明构思不限于此。当绝缘衬层115l包括氧化硅层时,o2、o3、o2等离子体、h2o等可以用作氧化气体,但是本公开不限于此。

217.虽然在图18a的结果上形成绝缘衬层115l,但是金属硅化物层118可以由图18a所示的含金属层117形成。例如,当在图18a的结果上形成绝缘衬垫115l时,构成图18a所示的含金属层117的氧化钨以及由于脱气而保留在导电焊盘区域112中的诸如wf6基气体、wc16基气体之类的含钨气体可以与在形成绝缘衬层115l的过程中使用的si前驱体反应,并且可以形成包括硅化钨层的金属硅化物层118。

218.在示例实施例中,金属硅化物层118可以包括氮元素(n)和氧(o)中的至少一种元素。例如,金属硅化物层118可以包括wsi、wsin、wsio或其组合。本说明书中使用的术语“wsi”、“wsin”和“wsio”可以表示包括每个术语中包括的元素的材料,并且可以不表示化学计量关系。

219.在形成金属硅化物层118时,根据导电焊盘区域112的厚度、体积和/或平面面积、形成绝缘衬层115l时的工艺温度和工艺压力、形成绝缘衬层115l时使用的si前驱体和硝化气体的类型、第一接触孔h11延伸到导电焊盘区域112中的深度等,金属硅化物层118可以具有图5c所示的配置、图7a至图7c所示的金属硅化物层118a、118b和118c的配置、以及据此修改和改变的各种配置。

220.参照图18c,可以回蚀绝缘衬层115l,使得在图18b的结果中通过第一接触孔h11暴露金属硅化物层118。结果,绝缘插塞115可以保留在第一接触孔h11中。可以通过第一接触孔h11中的绝缘插塞115暴露金属硅化物层118。

221.参照图18d,当在图18c的结果中填充第一接触孔h11时,可以形成覆盖硬掩模hm的上表面的导电层116l。导电层116l可以包括钨、钛、钽、铜、铝、氮化钛、氮化钽、氮化钨或其组合。

222.参照图18e,可以将图18d的结果平坦化,使得绝缘结构ins的上表面被暴露,并且可以在第一接触孔h11中形成接触插塞116。接触插塞116可以包括保留在导电层116l的第一接触孔h11中的部分。

223.返回参照图17e,当在存储单元区域mec中形成覆盖图17e的结果的层间绝缘层195之后,通过形成穿透层间绝缘层195的一些区域的多个位线bl、多个布线层ml和多个外围布线层pml,可以制造参照图4和图5a至图5c描述的半导体器件100。

224.已经参考图17a到图17e和图18a到图18e描述了参考图4和图5a到图5c描述的半导体器件100的制造方法。然而,本领域技术人员将认识到,通过在本发明构思的技术范围内对以上描述应用各种修改和改变,可以参考图7a至图12来制造半导体器件200a、200b、200c、300、400、500a、500b和600,并且可以通过在本发明构思的技术范围内对其应用各种修改和改变来制造具有各种结构的半导体器件。

225.尽管已参考本发明构思的一些示例实施例详细示出和描述了本发明构思,但是将理解的是,在不脱离所附权利要求的范围的情况下,可以在形式和细节上进行各种改变。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。