技术特征:

1.一种半导体结构的形成方法,其特征在于,包括:提供衬底、以及凸出于所述衬底的半导体叠层柱,所述半导体叠层柱包括由下而上依次堆叠的第一掺杂层、初始沟道柱以及用于形成第二掺杂层的半导体层;形成包围所述初始沟道柱侧壁且暴露出半导体层的伪栅;在所述衬底上形成填充于相邻所述半导体叠层柱之间、包围所述伪栅露出的半导体叠层柱侧壁且覆盖所述伪栅顶面的底部介质层,所述底部介质层暴露出所述伪栅远离相邻半导体叠层柱的侧壁;去除所述伪栅,暴露出所述初始沟道柱的侧壁,在所述底部介质层中形成栅极开口;对所述栅极开口露出的初始沟道柱侧壁进行减薄,剩余的所述初始沟道柱用于作为沟道柱;对所述栅极开口进行填充,形成包围所述沟道柱侧壁的栅极。2.如权利要求1所述的半导体结构的形成方法,其特征在于,形成所述伪栅的步骤中,位于相邻所述半导体叠层柱侧壁上的伪栅之间具有间隔,所述伪栅与相邻半导体叠层柱相对的侧壁为第一侧壁,所述伪栅远离相邻半导体叠层柱的侧壁为第二侧壁;形成所述底部介质层的步骤中,所述底部介质层覆盖所述伪栅的第一侧壁且暴露出所述伪栅的第二侧壁。3.如权利要求1所述的半导体结构的形成方法,其特征在于,提供衬底和半导体叠层柱的步骤中,所述第一掺杂层的侧壁、与所述初始沟道柱的侧壁以及所述半导体层的侧壁相齐平。4.如权利要求1所述的半导体结构的形成方法,其特征在于,对所述初始沟道柱侧壁进行减薄的工艺包括湿法刻蚀工艺。5.如权利要求4所述的半导体结构的形成方法,其特征在于,所述湿法刻蚀工艺的刻蚀溶液包括tmah溶液。6.如权利要求1所述的半导体结构的形成方法,其特征在于,对所述初始沟道柱侧壁进行减薄的步骤中,所述初始沟道柱和所述第一掺杂层的刻蚀选择比至少为5:1,所述初始沟道柱和所述半导体层的刻蚀选择比至少为5:1。7.如权利要求1所述的半导体结构的形成方法,其特征在于,沿垂直于所述半导体叠层柱侧壁的方向,所述沟道柱具有目标宽度;提供衬底和半导体叠层柱的步骤中,沿垂直于所述半导体叠层柱侧壁的方向,所述初始沟道柱的宽度是所述目标宽度的1.2倍至1.6倍。8.如权利要求1所述的半导体结构的形成方法,其特征在于,在提供衬底和半导体叠层柱之后,且在形成所述伪栅之前,所述半导体结构的形成方法还包括:在所述衬底上形成隔离结构,包围所述第一掺杂层的部分侧壁。9.如权利要求2所述的半导体结构的形成方法,其特征在于,位于相邻所述半导体叠层柱侧壁上的伪栅之间的间隔,是相邻半导体叠层柱之间间隔的30%至70%。10.如权利要求1或2所述的半导体结构的形成方法,其特征在于,形成所述伪栅的步骤包括:在所述衬底上形成覆盖所述半导体叠层柱的初始伪栅;去除部分厚度的初始伪栅,使剩余的初始伪栅暴露出所述半导体层;图形化剩余的初始伪栅,保留包围所述初始沟道柱侧壁的部分初始伪栅用于作为所述

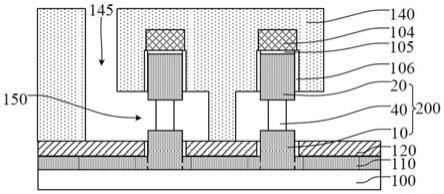

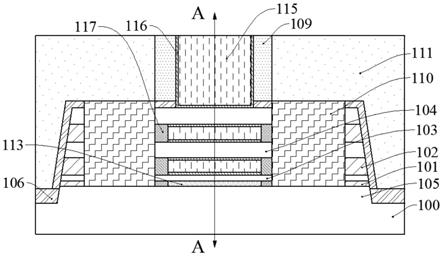

伪栅。11.如权利要求1或2所述的半导体结构的形成方法,其特征在于,形成所述底部介质层的步骤中,所述底部介质层覆盖所述半导体叠层柱的顶面;形成所述底部介质层的步骤包括:在所述衬底上形成覆盖所述半导体叠层柱和伪栅的介质材料层;图形化所述介质材料层,保留位于相邻半导体叠层柱之间、包围所述伪栅露出的半导体叠层柱侧壁且覆盖伪栅顶面的介质材料层作为底部介质层。12.如权利要求1所述的半导体结构的形成方法,其特征在于,形成所述栅极的工艺包括原子层沉积、物理气相沉积、化学气相沉积和电镀中的一种或多种工艺。13.如权利要求1所述的半导体结构的形成方法,其特征在于,提供衬底和半导体叠层柱的步骤中,还形成与所述第一掺杂层的底部相连、位于所述衬底上且沿平行于衬底方向延伸的掺杂层侧部;在形成所述栅极后,所述半导体结构的形成方法还包括:形成与所述掺杂层侧部相接触的第一源漏插塞。14.如权利要求13所述的半导体结构的形成方法,其特征在于,提供衬底和半导体叠层柱的步骤包括:提供衬底、由下而上依次堆叠于所述衬底上的第一初始掺杂层、沟道材料层以及初始半导体层;图形化所述初始半导体层、沟道材料层以及部分厚度的第一初始掺杂层,形成所述掺杂层侧部、第一掺杂层、初始沟道柱以及所述半导体层。15.如权利要求1所述的半导体结构的形成方法,其特征在于,所述初始沟道柱用于作为初始底部沟道柱;所述半导体层用于作为第二掺杂层;所述伪栅用于作为底部伪栅;所述栅极开口用于作为底部栅极开口;所述沟道柱用于作为底部沟道柱;所述栅极用于作为底部栅极;在提供半导体叠层柱的步骤中,所述半导体叠层柱还包括由下而上依次堆叠于所述第二掺杂层上的缓冲层、第三掺杂层、初始顶部沟道柱以及用于形成第四掺杂层的顶部半导体层;在形成所述底部栅极后,所述半导体结构的形成方法还包括:去除部分厚度的所述底部介质层,暴露出所述初始顶部沟道柱;形成包围初始顶部沟道柱的顶部伪栅;在所述底部介质层上形成填充于相邻所述半导体叠层柱之间、包围所述顶部伪栅露出的半导体叠层柱侧壁且覆盖顶部伪栅顶面的顶部介质层,所述顶部介质层暴露出所述顶部伪栅远离相邻半导体叠层柱的侧壁;去除所述顶部伪栅,形成顶部栅极开口;对所述顶部栅极开口露出的初始顶部沟道柱侧壁进行减薄,形成顶部沟道柱;在所述顶部栅极开口中形成包围所述顶部沟道柱的顶部栅极。16.一种半导体结构,其特征在于,包括:衬底;半导体叠层柱,凸出于所述衬底,所述半导体叠层柱包括由下而上依次堆叠的第一掺杂层、沟道柱以及第二掺杂层,沿垂直于所述沟道柱侧壁的方向,所述沟道柱的侧壁相对于所述第一掺杂层和第二掺杂层的侧壁缩进;栅极,包围所述沟道柱的侧壁,位于相邻所述半导体叠层柱侧壁上的栅极之间具有间

隔;介质层,填充于位于相邻半导体叠层柱侧壁的栅极之间且覆盖所述栅极的顶面。17.如权利要求16所述的半导体结构,其特征在于,所述沟道柱的材料包括si;所述第一掺杂层和第二掺杂层的材料包括sige、sip或sic。18.如权利要求16所述的半导体结构,其特征在于,沿垂直于所述沟道柱侧壁的方向,所述沟道柱具有目标宽度;所述沟道柱单侧侧壁相对于所述第一掺杂层侧壁缩进的尺寸为缩进宽度,所述缩进宽度是所述目标宽度的10%至30%。19.如权利要求16所述的半导体结构,其特征在于,所述沟道柱用于作为底部沟道柱;所述栅极用于作为底部栅极;所述半导体叠层柱还包括:由下而上依次堆叠于所述第二掺杂层上的缓冲层、第三掺杂层、顶部沟道柱以及第四掺杂层,所述顶部沟道柱的侧壁相对于第三掺杂层或第四掺杂层的侧壁缩进;所述半导体结构还包括:包围所述顶部沟道柱侧壁的顶部栅极。20.如权利要求19所述的半导体结构,其特征在于,所述第一掺杂层和第二掺杂层中掺杂有第一型离子;所述第三掺杂层和第四掺杂层中掺杂有第二型离子,所述第二型与第一型的掺杂类型不同。

技术总结

一种半导体结构及其形成方法,形成方法包括:提供衬底、以及凸出于衬底的半导体叠层柱,半导体叠层柱包括由下而上依次堆叠的第一掺杂层、初始沟道柱以及半导体层;形成包围初始沟道柱侧壁且暴露出半导体层的伪栅;在衬底上形成填充于相邻半导体叠层柱之间、包围伪栅露出的半导体叠层柱侧壁且覆盖伪栅顶面的底部介质层,底部介质层暴露出伪栅远离相邻半导体叠层柱的侧壁;去除伪栅,形成暴露出初始沟道柱的侧壁的栅极开口;对暴露出的初始沟道柱侧壁进行减薄,形成沟道柱;在栅极开口中形成包围沟道柱侧壁的栅极。本发明实施例有利于提升VGAA晶体管的性能。VGAA晶体管的性能。VGAA晶体管的性能。

技术研发人员:王楠

受保护的技术使用者:中芯国际集成电路制造(北京)有限公司

技术研发日:2020.08.14

技术公布日:2022/2/23

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。