恒压电路

1.本技术享受以日本专利申请2020-136142号(申请日:2020年8月12日)为基础申请的优先权。本技术通过参照该基础申请而包含基础申请的全部内容。

技术领域

2.本发明的实施方式涉及一种恒压电路。

背景技术:

3.作为恒压电路之一,已知有一种线性稳压器。

技术实现要素:

4.实施方式提供一种能够提高测试的可靠性的恒压电路。

5.实施方式所涉及的恒压电路包括:第1增益级,输出第1电压,该第1电压是将分割输出电压而得到的分电压与参照电压之间的差分进行放大而得到的;第2增益级,包括第1晶体管,从第1节点输出将第1电压放大而得到的第2电压,第1晶体管的栅极被施加第1电压,一端与输入电压端子连接,另一端与第1节点连接;第2晶体管,一端与输入电压端子连接,另一端与输出电压端子连接,根据对栅极施加的第2电压而将输出电压控制为恒定;以及第1电路,选择第1动作模式或者第2动作模式。在选择第1动作模式的情况下,在第2增益级的上述第1节点流动第1电流,在选择第2动作模式的情况下,在第2增益级的第1节点流动比第1电流大的第2电流。

附图说明

6.图1是第1实施方式所涉及的恒压电路的电路图。

7.图2是第1实施方式所涉及的恒压电路中的动作模式的选择动作的流程图。

8.图3是表示对恒压电路进行测试时的测试电路的一例的示意图。

9.图4是表示在第1实施方式所涉及的恒压电路中,测试模式以及通常模式中的增益与相位之间的频率依存性的曲线图。

10.图5是第2实施方式的第1例所涉及的恒压电路的电路图。

11.图6是第2实施方式的第2例所涉及的恒压电路的电路图。

12.图7是搭载有第3实施方式的第1例所涉及的恒压电路的封装的立体图。

13.图8是第3实施方式的第1例所涉及的恒压电路的半导体芯片的立体图。

14.图9是第4实施方式的第1例所涉及的恒压电路所具备的模式选择电路的框图。

15.图10是表示第4实施方式的第1例所涉及的恒压电路所具备的模式选择电路的输入信号与动作模式之间的关系的一例的表。

16.图11是表示第4实施方式的第1例所涉及的恒压电路所具备的模式选择电路的输入信号与动作模式之间的关系的一例的表。

17.图12是第4实施方式的第2例所涉及的恒压电路所具备的模式选择电路的框图。

18.图13是第4实施方式的第2例所涉及的恒压电路所具备的模式选择电路中的输入信号的时序图。

具体实施方式

19.以下,参照附图对实施方式进行说明。在以下的说明中,有时对具有大致相同的功能以及构成的构成要素标注相同符号、并省略重复的说明。另外,只要不是明确地或者显而易见地被排除,则关于某个实施方式的说明也适用于其他实施方式的说明。

20.各功能块不是必须如以下的例子那样进行区别。例如,一部分功能也可以通过与例示的功能块不同的功能块来执行。并且,例示的功能块也可以分割为更精细的功能子块。不通过由哪个功能块确定来限定实施方式。

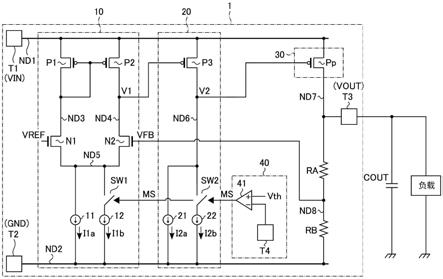

21.在本说明书以及专利请求范围中,某个第1要素与其他的第2要素“连接”,包括第1要素直接与第2要素连接,或者第1要素常时或选择性地经由导电性的要素而与第2要素连接。

22.1.第1实施方式

23.对第1实施方式所涉及的恒压电路进行说明。在本实施方式中,作为恒压电路以线性稳压器为例来进行说明。

24.本实施方式的恒压电路作为动作模式而具有测试模式和通常模式。在量产测试(出厂检查)等的恒压电路1的测试时,选择测试模式。在作为恒压电路而通常使用时,选择通常模式。例如,与测试模式相比,通常模式在电源纹波抑制比(psrr:power supply ripple rejection)、或者负载(load)剧烈变动时的输出瞬态响应性(以下,也表述为“响应”)这些方面较优良。另一方面,与通常模式相比,测试模式针对寄生电感等的影响的稳定性、即耐振荡性较优良。

25.1.1构成

26.首先,使用图1对恒压电路的电路构成进行说明。图1是表示恒压电路的电路构成的一例的电路图。此外,在以下的说明中,在不限定晶体管的源极以及漏极的情况下,将晶体管的源极和漏极中的某一方表述为“晶体管的一端”,将晶体管的源极和漏极中的另一方表述为“晶体管的另一端”。

27.如图1所示,恒压电路1包括输入电压端子t1、基准电压端子t2、输出电压端子t3、信号端子t4、第1增益级10、第2增益级20、输出级30、模式选择电路40、以及电阻元件ra和rb。

28.恒压电路1作为具有第1增益级10、第2增益级20以及输出级30的放大器发挥功能。

29.输入电压端子t1与节点nd1(以下,也表述为“电源电压布线”)连接,被从外部施加输入电压vin。

30.基准电压端子t2与节点nd2(以下,也表述为“接地电压布线”)连接。基准电压端子t2例如可以被接地,也可以被施加接地电压(vss)。

31.输出电压端子t3与节点nd7连接。输出电压vout被从输出电压端子t3输出。例如,在使用恒压电路1时,在输出电压端子t3与连接在恒压电路1的外部的负载(load)之间连接电容元件cout。电容元件cout作为输出电容器发挥功能。电容元件cout例如抑制与输出电压端子t3连接的负载(load)的变动、由于在恒压电路1与负载之间产生的寄生电感等的影

响而产生的输出电压vout的波动、振荡等。例如,电容元件cout的一方的电极与输出电压端子t3连接,另一方的电极被接地(与接地电压布线连接)。

32.信号端子t4作为从外部接收的测试模式选择信号的信号端子而发挥功能。例如,在测试模式选择信号是高(“h”)电平的情况下,即,在信号端子t4被施加有“h”电平的电压的情况下,恒压电路1选择测试模式。另外,在测试模式选择信号是低(“l”)电平的情况下,即,在信号端子t4被施加有“l”电平的电压的情况下,恒压电路1选择通常模式。

33.电阻元件ra及rb作为输出电压vout的分压电路发挥功能。电阻元件ra的一端与节点nd7连接,另一端与节点nd8连接。电阻元件rb的一端与节点nd8连接,另一端与节点nd2连接。将对节点nd8施加的电压设为vfb,将电阻元件ra的电阻值设为ra,将电阻元件rb的电阻值设为rb。于是,输出电压vout与电压vfb处于vout=vfb

×

(1 ra/rb)的关系。即,电压vfb是对输出电压vout进行分割而得到的分电压。

34.第1增益级10是差动放大电路。第1增益级10将参照电压vref与电压vfb进行比较,并将与其差分对应(放大后)的电压输出到第2增益级20。第1增益级10包括p沟道mosfet(metal oxide semiconductor field effect transistor:金属氧化物半导体场效应晶体管)(以下,也表述为“pmos晶体管”)p1及p2、n沟道mosfet(以下,也表述为“nmos晶体管”)n1及n2、电流源11及12、以及开关电路sw1。

35.pmos晶体管p1的一端与节点nd1连接,另一端以及栅极与节点nd3连接。

36.pmos晶体管p2的一端与节点nd1连接,另一端与节点nd4连接,栅极与节点nd3连接。即,pmos晶体管p1以及p2构成电流反射镜。

37.nmos晶体管n1的一端与节点nd3连接,另一端与节点nd5连接。nmos晶体管n1的栅极被施加参照电压vref。参照电压vref是不依存于温度或者输入电压vin的、恒定的基准电压。

38.nmos晶体管n2的一端与节点nd4连接,另一端与节点nd5连接。nmos晶体管n2的栅极被施加电压vfb。

39.电流源11的一端与节点nd5连接,另一端与节点nd2连接。从电流源11向节点nd2流动电流i1a。

40.开关电路sw1的一端与节点nd5连接,另一端与电流源12的一端连接。开关电路sw1根据从模式选择电路40接收的模式信号ms来进行动作。例如,模式信号ms在通常模式的情况下被设为“h”电平,在测试模式的情况下被设为“l”电平。例如,开关电路sw1在模式信号ms是“h”电平的情况下被设为接通状态(连接状态),在模式信号ms是“l”电平的情况下被设为断开状态(非连接状态)。

41.电流源12的另一端与节点nd2连接。从电流源12向节点nd2流动电流i1b。因此,在测试模式的情况下,在第1增益级10(差动放大电路)流动动作电流i1a,在通常模式的情况下,在第1增益级10流动动作电流(i1a i1b)。动作电流(i1a i1b)大于动作电流i1a。因此,与测试模式相比,在通常模式下能够使下一级的第2增益级20高速地驱动。

42.第2增益级20将第1增益级10的输出电压放大而输出到输出级30。第2增益级20包括pmos晶体管p3、电流源21和22、以及开关电路sw2。

43.pmos晶体管p3的一端与节点nd1连接,另一端与节点nd6连接。pmos晶体管p3的栅极与节点nd4连接。换言之,pmos晶体管p3的栅极被施加第1增益级10的输出电压v1。

44.电流源21的一端与节点nd6连接,另一端与节点nd2连接。从电流源21向节点nd2流动电流i2a。

45.开关电路sw2的一端与节点nd6连接,另一端与电流源22的一端连接。开关电路sw2根据从模式选择电路40接收的模式信号ms来进行动作。例如,开关电路sw2在模式信号ms是“h”电平的情况下被设为接通状态,在模式信号ms是“l”电平的情况下被设为断开状态。

46.电流源22的另一端与节点nd2连接。从电流源22向节点nd2流动电流i2b。因此,在测试模式的情况下,在第2增益级20流动动作电流i2a,在通常模式的情况下,在第2增益级20流动动作电流(i2a i2b)。动作电流(i2a i2b)大于动作电流i2a。因此,与测试模式相比,通常模式能够使下一级的输出级30高速地驱动。

47.输出级30对恒压电路1的输出电压vout进行控制。输出级30包括pmos晶体管pp。

48.pmos晶体管pp的一端与节点nd1连接,另一端与节点nd7连接。pmos晶体管pp的栅极与节点nd6连接。换言之,pmos晶体管pp的栅极被施加第2增益级20的输出电压v2。pmos晶体管pp作为恒压电路1的输出驱动器发挥功能。为了使输出电压vout恒定,pmos晶体管pp的栅极电压根据输出电压vout的变动而变动,pmos晶体管pp的接通电阻被调整。

49.例如,在参照电压vref与电压vfb之间没有电压差的情况下,即,在vfb=vref的情况下,输出电压vout为vout=vref

×

(1 ra/rb)。在表示输出电压vout的公式中,不包含输入电压vin或者在负载中流动的负载电流的项。因此,即使输入电压vin以及负载发生变动,输出电压vout也能够维持恒定电压。

50.模式选择电路40包括比较器41。

51.比较器41的反相输入端子与信号端子t4连接。对比较器41的非反相输入端子输入阈值电压vth。阈值电压vth是为了用于辨别信号端子t4的电压(测试模式选择信号)是“h”电平还是“l”电平而设定的电压。例如,阈值电压vth被设定为“l”电平电压与“h”电平电压的中间电压。从比较器41的输出端子输出模式信号ms。例如,在信号端子t4的电压是“h”电平的情况下,即,在选择测试模式的情况下,比较器41输出“l”电平的模式信号ms。另外,在信号端子t4的电压是“l”电平的情况下,即,在选择通常模式的情况下,比较器41输出“h”电平的模式信号ms。

52.1.2模式选择动作

53.接着,使用图2对模式选择动作进行说明。图2是表示模式选择动作的流程图。

54.如图2所示,模式选择电路40为,在信号端子t4的电压(测试模式选择信号)是“h”电平的情况下(步骤s1_是),将模式信号ms设为“l”电平(步骤s2)。换言之,在比较器41中,在反相输入端子的电压为非反相输入端子的阈值电压vth以上的情况下,比较器41输出“l”电平的电压。

55.开关电路sw1及sw2为,当接收到“l”电平的模式信号ms时,被设为断开状态(步骤s3),其结果,在恒压电路1中执行测试模式(步骤s4)。

56.另一方面,模式选择电路40为,在信号端子t4的电压是“l”电平的情况下(步骤s1_否),将模式信号ms设为“h”电平(步骤s5)。换言之,在比较器41中,在反相输入端子的电压小于非反相输入端子的阈值电压vth的情况下,比较器41输出“h”电平的电压。

57.开关电路sw1及sw2为,当接收到“h”电平的模式信号ms时,被设为接通状态(步骤s6),其结果,在恒压电路1中执行通常模式(步骤s7)。

58.1.3测试环境下的寄生电感的影响

59.接着,使用图3来说明恒压电路1的测试环境下的寄生电感的影响。图3是表示对恒压电路1进行测试时的测试电路的一例的示意图。例如,在量产测试(出厂检查)中,一个或多个恒压电路1被搭载于夹具(测试板)。然后,该夹具被设置于测试仪,而被执行测试。

60.如图3所示,在夹具上例如搭载恒压电路1、电容元件cin和cout、负载(load)、以及多个继电器电路201~203。

61.测试仪电源的vin端子与节点nd101连接。测试仪电源的gnd端子与节点nd102连接。

62.恒压电路1的输入电压端子t1与节点nd101连接。恒压电路1的基准电压端子t2与节点nd102连接。恒压电路1的输出电压端子t3与节点nd103连接。在测试时,恒压电路1的信号端子t4被施加“h”电平的电压。

63.电容元件cin和cout具有如下的作用,并抑制恒压电路1的反馈动作的不稳定:降低输入电压vin与基准电压(gnd)之间的阻抗而使输出电压vout稳定,或者在较低的频率范围内产生极点(pole)而使反馈路径稳定化。

64.电容元件cin的一方的电极经由继电器电路201而与节点nd101连接。电容元件cin的另一方的电极与节点nd102连接。

65.电容元件cout的一方的电极与节点nd103连接。电容元件cout的另一方的电极经由继电器电路202而与节点nd102连接。

66.负载的一端与节点nd103连接,另一端经由继电器电路203而与节点nd102连接。

67.继电器电路201~203分别切换电容元件cin、电容元件cout以及负载的连接。根据测试的项目的不同,有时将电容元件cin、电容元件cout以及负载从恒压电路1切离。例如,在测定恒压电路1的消耗电流的情况下,为了抑制由于电容元件cin及cout的充放电而产生的测试时间的延迟,以及为了将消耗电流与充放电的电流区分开,而将电容元件cin及cout的继电器电路201及202断开来进行测定。

68.例如,在量产测试中,为了缩短测试时间,有时对多个恒压电路1一并进行处理(测定)。在这种情况下,在夹具上搭载多个恒压电路1以及与它们对应的多个电容元件cin及cout。于是,根据布局的情况,有时无法在恒压电路1的附近配置所对应的电容元件cin及cout。另外,在测试中,也有时将电容元件cin及cout或者负载切离而进行测定。因此,有时在恒压电路1与各元件之间设置有继电器电路。其结果,有时连接恒压电路1与各元件的布线变得比较长。有时连接恒压电路1与测试仪电源或者负载的布线长度也同样变长。因此,在各布线(节点)中可能产生比较大的寄生电感(以下,还表述为“寄生l”)。例如,在测试仪电源的vin端子与恒压电路1的输入电压端子t1之间、恒压电路1的基准电压端子t2与测试仪电源的gnd端子之间、电容元件cin与测试仪电源的gnd端子之间、恒压电路1的输出电压端子t3与电容元件cout之间、以及恒压电路1的输出电压端子t3与负载(load)之间可能产生寄生电感。当连接恒压电路1与各元件的布线长度变长时,寄生电感与其对应地变大。

69.1.4相位特性

70.接着,使用图4对恒压电路1的相位特性进行说明。图4是表示测试模式以及通常模式中的增益与相位之间的频率依存性的曲线图(伯德图)。

71.如图4所示,在测试模式中,在根据图1说明过的第1增益级10以及第2增益级20中

不流动加法电流、即电流i1b及i2b。因此,与通常模式相比较,测试模式的第1极点(pole)位于较低频率一侧。其结果,在测试模式的情况下,增益以比通常模式低的频率开始下降。因此,与通常模式相比,在测试模式下,增益成为0db(1倍)的频率(单位增益)变低。当将测试模式与通常模式的相位余量(在增益成为0db的频率下离相位180

°

的剩余相位)进行比较时,与通常模式相比,测试模式下的相位余量较大。即,测试模式的稳定性(耐振荡性)较高。因此,测试模式难以受到寄生电感的影响。

72.1.5本实施方式的效果

73.根据本实施方式所涉及的构成,能够提高恒压电路的测试的可靠性。以下,对其效果进行详细说明。

74.近年来,智能手机、行车记录仪等搭载摄像机的设备增加。与此相伴,对摄像机所使用的图像传感器供给电压的线性稳压器被要求较高的psrr特性、高速响应性。为了抑制由于与线性稳压器连接的布线的寄生电感的影响而产生的线性稳压器的振荡,优选将电容元件cin及cout连接于线性稳压器的附近。但是,在量产测试(出厂检查)时,由于夹具的限制等,有时无法将电容元件cin及cout连接于线性稳压器的附近。线性稳压器相对于寄生电感的稳定性(鲁棒性)、即耐振荡性,与高psrr特性以及高速响应性处于相反的关系。即,当线性稳压器的psrr特性以及响应性提高时,耐振荡性降低。因此,线性稳压器的测试的可靠性降低。

75.与此相对,根据本实施方式所涉及的构成,恒压电路具有测试模式和通常模式这两个动作模式,且包括模式选择电路。在测试模式的情况下,与通常模式相比,能够减少第1增益级以及第2增益级的动作电流。其结果,例如,恒压电路在出厂测试时能够使用具有较高稳定性(耐振荡性)的测试模式。另外,恒压电路在通常使用时能够使用具有高psrr特性、高速响应性的通常模式。因此,在具有高psrr特性以及高速响应性的恒压电路中,能够提高测试的可靠性。

76.2.第2实施方式

77.接着,对第2实施方式进行说明。在第2实施方式中,对于与第1实施方式不同的恒压电路1的构成说明两个例子。以下,以与第1实施方式的不同点为中心进行说明。

78.2.1第1例

79.首先,使用图5对第1例的恒压电路1的构成进行说明。图5是表示恒压电路1的电路构成的一例的电路图。

80.如图5所示,本实施例的恒压电路1为,在第1增益级10中取消电流源12以及开关电路sw1。其他构成与第1实施方式的图1相同。

81.从电流源11向节点nd2流动电流i1c。电流i1c与在第1实施方式中说明过的电流i1a或者i1b,可以相同也可以不同。因此,与动作模式无关,在第1增益级10(差动放大电路)中流动动作电流i1c。

82.2.2第2例

83.接着,使用图6对第2例的恒压电路1的构成进行说明。图6是表示恒压电路1的电路构成的一例的电路图。

84.如图6所示,在本实施例的恒压电路1中,在第1增益级10的输入端子使用pmos晶体管,在第2增益级20使用nmos晶体管。

85.第1增益级10包括pmos晶体管p1和p2、nmos晶体管n1和n2、以及电流源11。

86.电流源11的一端与节点nd1连接,另一端与节点nd10连接。从电流源11向节点nd10流动电流i1c。

87.pmos晶体管p1的一端与节点nd10连接,另一端与节点nd11连接。pmos晶体管p1的栅极被施加参照电压vref。

88.pmos晶体管p2的一端与节点nd10连接,另一端与节点nd12连接。pmos晶体管p2的栅极被施加电压vfb。

89.nmos晶体管n1的一端以及栅极与节点nd11连接,另一端与节点nd2连接。

90.nmos晶体管n2的一端与节点nd12连接,另一端与节点nd2连接,栅极与节点nd11连接。nmos晶体管n1以及nmos晶体管n2构成电流反射镜。

91.第2增益级20包括nmos晶体管n3、电流源21和22、以及开关电路sw2。

92.电流源21的一端与节点nd1连接,另一端与节点nd13连接。从电流源21向节点nd13流动电流i2a。

93.电流源22的一端与节点nd1连接,另一端与开关电路sw2的一端连接。从电流源22向开关电路sw2流动电流i2b。

94.开关电路sw2的另一端与节点nd13连接。开关电路sw2根据从模式选择电路40接收到的模式信号ms来进行动作。例如,开关电路sw2为,在模式信号ms为“h”电平的情况下被设为接通状态,在模式信号ms为“l”电平的情况下被设为断开状态。

95.nmos晶体管n3的一端与节点nd13连接,另一端与节点nd2连接。nmos晶体管n3的栅极与节点nd12连接。换言之,nmos晶体管n3的栅极被施加第1增益级10的输出电压v1。

96.输出级30的pmos晶体管pp的栅极与节点nd13连接。换言之,pmos晶体管pp的栅极被施加第2增益级20的输出电压v2。

97.其他构成与第1实施方式的图1相同。

98.2.3本实施方式的效果

99.根据本实施方式所涉及的构成,能够得到与第1实施方式同样的效果。

100.此外,在第2例中,也可以与第1实施方式同样,在第1增益级10中与电流源11并联地设置有电流源12以及开关电路sw1。

101.3.第3实施方式

102.接着,对第3实施方式进行说明。在第3实施方式中,对于信号端子t4说明两个例子。以下,以与第1实施方式以及第2实施方式的不同点为中心进行说明。

103.3.1第1例

104.首先,使用图7对第1例进行说明。图7是搭载了恒压电路1的封装的立体图。

105.如图7所示,在封装(管壳)上设置有与信号端子t4连接的测试引脚。从测试引脚向信号端子t4施加电压。例如,在出厂检查的情况下,在最终形态(出厂形态)下执行测试。此外,封装的方式能够任意地进行设计。只要能够从外部施加电压的引脚之一与信号端子t4对应即可。

106.3.2第2例

107.首先,使用图8对第2例进行说明。图8是恒压电路1的半导体芯片的立体图。

108.如图8所示,例如,在恒压电路1的制造工序中,也可以在组装前执行测试。在该情

况下,在芯片表面上设置与信号端子t4对应的测试焊盘。此外,在组装工序中,测试焊盘也可以不被焊接。

109.3.本实施方式的效果

110.根据本实施方式所涉及的构成,能够得到与第1实施方式同样的效果。

111.4.第4实施方式

112.接着,对第4实施方式进行说明。在第4实施方式中,对于与第1实施方式不同的模式选择电路40的构成说明两个例子。

113.4.1第1例

114.首先,使用图9~图11对第1例进行说明。图9是模式选择电路40的框图。图10以及图11分别是表示模式选择电路40的输入信号与动作模式之间的关系的一例的表。

115.如图9所示,本例的模式选择电路40包括vin输入端子t5、使能信号输入端子t6以及vout输入端子t7。本例的模式选择电路40根据三个输入信号(电压)的组合来选择动作模式。

116.与输入电压端子t1同样,vin输入端子t5被施加输入电压vin。

117.从外部接收到的使能信号(enable)被输入至使能信号输入端子t6。例如,使能信号是用于使恒压电路1成为使能状态的信号。例如,在使能信号为“h”电平的情况下,恒压电路1被设为动作状态(接通状态)。

118.vout输入端子t7被施加输出电压vout。

119.首先,对使能信号、以及电压vin和vout的组合的第1个例子进行说明。

120.如图10所示,模式选择电路40例如可以根据输入电压vin与输出电压vout之间的电压差来选择模式信号ms的电平。

121.更具体而言,例如,在使能信号为“l”电平的情况下,恒压电路1被设为断开状态。

122.在使能信号为“h”电平的状态下,在输入电压vin与输出电压vout之间的电压差为预先设定的电压va以上的情况下,模式选择电路40输出与测试模式对应的“l”电平的模式信号ms。换言之,由于输出电压vout恒定,因此在恒压电路1的动作保证范围内,在输入电压vin为(vout-va)以下的电压值的情况下,选择测试模式。

123.另一方面,在输入电压vin与输出电压vout之间的电压差小于预先设定的电压va的情况下,模式选择电路40输出与通常模式对应的“h”电平的模式信号ms。换言之,在恒压电路1的动作保证范围内,在输入电压vin为比(vout-va)高的电压值的情况下,选择通常模式。

124.接着,对使能信号enable、以及电压vin和vout的组合的第二个例子进行说明。

125.如图11所示,模式选择电路40例如可以根据输入电压vin与“h”电平的使能信号之间的电压差来选择模式信号ms的电平。

126.更具体而言,例如,在使能信号为“l”电平的情况下,恒压电路1被设为断开状态。

127.在使能信号为“h”电平的状态下,在输入电压vin与“h”电平的使能信号之间的电压差为预先设定的电压vb以上的情况下,模式选择电路40输出与测试模式对应的“l”电平的模式信号ms。因此,例如,在使能信号的“h”电平的电压为恒定的情况下,在恒压电路1的动作保证范围内,当输入电压vin为((“h”电平的使能信号)-vb)以下的电压值时,选择测试模式。或者,例如,在输入电压vin为恒定的情况下,在被判定为“h”电平的电压范围内,当使

能信号的“h”电平的电压成为(vin vb)以上的电压值时,选择测试模式。

128.另一方面,在输入电压vin与“h”电平的使能信号之间的电压差小于预先设定的电压vb的情况下,模式选择电路40输出与通常模式对应的“h”电平的模式信号ms。因此,例如,在使能信号的“h”电平的电压为恒定的情况下,在恒压电路1的动作保证范围内,在输入电压vin为比((“h”电平的使能信号)-vb)高的电压值情况下,选择通常模式。或者,例如,在输入电压vin为恒定的情况下,在被判定为“h”电平的电压范围内,当使能信号的“h”电平的电压为小于(vin vb)的电压值时,选择通常模式。

129.4.2第2例

130.接着,使用图12和图13对第2例进行说明。图12是模式选择电路40的框图。图13是表示模式选择电路40的输入信号与动作模式之间的关系的一例的时序图。

131.在第2例中,对恒压电路1与spi(serial peripheral interface:串行外设接口)或者i2c(inter-integrated circuit:内置集成电路)这样的通信格式对应的情况进行说明。恒压电路1具有符合任意标准的数字通信接口电路。并且,能够根据来自外部的通信而使恒压电路1转移到测试模式。

132.如图12所示,本例的模式选择电路40包括时钟输入端子t8、使能信号输入端子t9以及data输入端子t10。本例的模式选择电路40根据三个输入信号(电压)的组合来选择动作模式。

133.从外部接收到的时钟信号clock被输入至时钟输入端子t8。

134.从外部接收到的使能信号(enable)被输入至使能信号输入端子t9。本例中的使能信号例如是用于使数据输入使能的信号。例如,在使能信号为“h”电平的情况下,模式选择电路40被设为能够接收数据data的状态。

135.从外部接收到的数据data被输入至data输入端子t10。

136.接着,对时钟信号clock、使能信号以及数据data的组合的一例进行说明。

137.如图13所示,例如,在使能信号enable为“h”电平的期间,在时钟信号clock从“l”电平上升到“h”电平的定时,数据data被收入到模式选择电路40。此时,例如,如果数据data为“lllhlllh”,则模式信号ms被设为“l”电平。即,恒压电路1选择测试模式。另外,在数据data为“lllhlllh”以外的情况下,模式信号ms被设为“h”电平。即,稳选器1选择通常模式。

138.4.3本实施方式的效果

139.能够将本实施方式应用于第1实施方式~第3实施方式。

140.5.变形例等

141.实施方式不限于上述说明的方式,能够进行各种变形。

142.对本发明的几个实施方式进行了说明,但这些实施方式是作为例子而提示的,并不意图对发明的范围进行限定。这些新的实施方式能够以其他各种方式加以实施,在不脱离发明的主旨的范围内能够进行各种省略、置换、变更。这些实施方式及其变形包括于发明的范围及主旨中,并且包括于专利请求范围所记载的发明和与其等同的范围中。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。