一种基于fpga和dsp的导航计算机板

技术领域

1.本发明涉及导航计算机技术领域,尤其涉及一种基于fpga和dsp的导航计算机板。

背景技术:

2.随着科技的发展,各行业对惯导系统的要求也越来越高;传统导航设备硬件结构采用if板,电源板,导航计算机板,导航底板的架构,复杂度高且体积难以控制,并且需要增加mcu进行数据的处理和转换,从而使得现有惯导设备体积较大,成本也较高。

技术实现要素:

3.针对现有技术存在的上述不足,本发明的目的在于提供一种基于fpga和dsp的导航计算机板,能够简化整个导航计算机板的电路结构,并降低设备体积,同时能够有效提高运算效率,并降低成本。

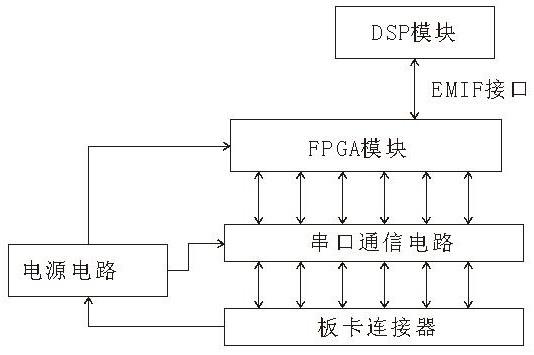

4.为了解决上述技术问题,本发明采用的技术方案是这样的:一种基于fpga和dsp的导航计算机板,其特征在于:包括电路板,在该电路板上集成有fpga模块、dsp模块以及外围接口电路和电源电路;所述dsp模块通过emif接口fpga模块与相连;所述外围接口电路包括串口通信电路和板卡连接器,fpga模块的外围电路通过串口通信电路与板卡连接器相连;所述电源电路也与板卡连接器相连,以接入外部电源,同时,该电源电路为fpga模块和dsp模块供电。

5.进一步地,所述dsp模块包括cpu核心、片上外围电路以及两级cache系统。

6.进一步地,所述fpga模块的外围电路包括复位与时钟电路、jtag模式的配置电路、与上位机进行通信的串口通信电路,与外部进行通信的网络通信电路以及电源电路。

7.进一步地,所述fpga模块采用xc7k325t-2ffg900芯片。

8.进一步地,所述电源电路采用双电源结构,其中,一个电源提供fpga的内核1.0v电压;另一个电源提供4路并行电源,分别为fpga的bank1,2以及外围模块提供3.3v电压,bank3提供1.8v电压,以及dsp内核1.2v电压。

9.与现有技术相比,本发明具有如下优点:1、将fpga、dsp以及外围接口电路集成在同一块电路板上,从而大大简化硬件结构,使整体结构更加简单,并且体积更小。

10.2、dsp通过emif接口技术与fpga相连,有效解决的fpga、dsp通信难的问题,从而大大提高数据传递、处理的效率。

附图说明

11.图1为本发明的电路原理框图。

具体实施方式

12.下面将结合附图及实施例对本发明作进一步说明。

13.实施例:参见图1,一种基于fpga和dsp的导航计算机板,包括电路板,在该电路板上集成有fpga模块、dsp模块以及外围接口电路和电源电路。

14.所述dsp模块通过emif接口fpga模块与相连;从而实现数据通信,并通过fpga模块提供rs-422、以太网等硬件接口。其中,所述dsp模块包括cpu核心、片上外围电路以及两级cache系统。具体地,cpu核心采用八流出超长指令字结构,整体作为sram映射到存储空间;为了降低功耗,其采用了双电源供电的方案,可并行输出4路电源。dsp芯片的内核电源需要1.2v,dsp外围电路的供电电源为3.3v,主要为dsp的io供电;其次,dsp需要设计时钟电路来产生时钟信号作为内核、片内外设以及外部接口的时钟源,本方案选用24mhz晶振作为时钟源;最后采用flash和sdram对导航程序、数据、参数进行保存以及对dsp的复位和emif通信。

15.实施时,所述fpga模块采用xc7k325t-2ffg900芯片;其包含840个数字信号器、445个36kb的bram,、326080个逻辑单元、10个cmt,16个gtx等可编程资源、可实现高性能数字信号处理、大容量的逻辑运算等应用,具有高带宽的数据吞吐能力。在导航计算机中fpga主要实现的功能是数据采集、将数据传输给dsp、与上位机通信等。所述fpga模块的外围电路包括复位与时钟电路、jtag模式的配置电路、与上位机进行通信的串口通信电路,与外部进行通信的网络通信电路以及电源电路。

16.所述外围接口电路包括串口通信电路和板卡连接器,fpga模块的外围电路通过串口通信电路与板卡连接器相连。fpga模块通过外围串口,网口处理接收到的外部导航信息,运用 emif总线技术传输给dsp,dsp通过导航算法对导航信息进行解算将结果传输给fpga,最后通过串口,网口输出至外部。

17.所述电源电路也与板卡连接器相连,以接入外部电源,同时,该电源电路为fpga模块和dsp模块供电。所述电源电路采用双电源结构,其中,一个电源提供fpga的内核1.0v电压;另一个电源提供4路并行电源,分别为fpga的bank1,2以及外围模块提供3.3v电压,bank3提供1.8v电压,以及dsp内核1.2v电压;上电时序为1.0v>1.2v>1.8v>3.3v。

18.工作过程中,fpga的io口ac26连接到dsp的复位管脚,上电后对此io进行先拉低再拉高操作,以此对dsp进行复位;惯性导航系统数据通过串口i存入fpga的ram1中的指定地址,dsp通过emif总线读取该地址中的数据,进行分析解算后,将解算后的数据又通过emif总线写入ram2的指定地址,fpga将该地址的数据通过串口ii或者通过spi总线到网络芯片输出至外部系统或上位机。

19.最后需要说明的是,以上实施例仅用以说明本发明的技术方案而非限制技术方案,本领域的普通技术人员应当理解,那些对本发明的技术方案进行修改或者等同替换,而不脱离本技术方案的宗旨和范围,均应涵盖在本发明的权利要求范围当中。

技术特征:

1.一种基于fpga和dsp的导航计算机板,其特征在于:包括电路板,在该电路板上集成有fpga模块、dsp模块以及外围接口电路和电源电路;所述dsp模块通过emif接口fpga模块与相连;所述外围接口电路包括串口通信电路和板卡连接器,fpga模块的外围电路通过串口通信电路与板卡连接器相连;所述电源电路也与板卡连接器相连,以接入外部电源,同时,该电源电路为fpga模块和dsp模块供电。2.根据权利要求1所述的一种基于fpga和dsp的导航计算机板,其特征在于:所述dsp模块包括cpu核心、片上外围电路以及两级cache系统。3.根据权利要求1所述的一种基于fpga和dsp的导航计算机板,其特征在于:所述fpga模块的外围电路包括复位与时钟电路、jtag模式的配置电路、与上位机进行通信的串口通信电路,与外部进行通信的网络通信电路以及电源电路。4.根据权利要求1所述的一种基于fpga和dsp的导航计算机板,其特征在于:所述fpga模块采用xc7k325t-2ffg900芯片。5.根据权利要求1所述的一种基于fpga和dsp的导航计算机板,其特征在于:所述电源电路采用双电源结构,其中,一个电源提供fpga的内核1.0v电压;另一个电源提供4路并行电源,分别为fpga的bank1,2以及外围模块提供3.3v电压,bank3提供1.8v电压,以及dsp内核1.2v电压。

技术总结

本发明公开了一种基于FPGA和DSP的导航计算机板,包括电路板,在该电路板上集成有FPGA模块、DSP模块以及外围接口电路和电源电路;所述DSP模块通过EMIF接口FPGA模块与相连;所述外围接口电路包括串口通信电路和板卡连接器,FPGA模块的外围电路通过串口通信电路与板卡连接器相连;所述电源电路也与板卡连接器相连,同时,该电源电路为FPGA模块和DSP模块供电。本发明能够简化整个导航计算机板的电路结构,并降低设备体积,同时能够有效提高运算效率,并降低成本。并降低成本。并降低成本。

技术研发人员:刘熙文 黄国松 苏柳 莫兰俊

受保护的技术使用者:重庆华渝电气集团有限公司

技术研发日:2021.11.30

技术公布日:2022/2/23

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。