1.本发明构思涉及半导体器件,更具体地,涉及包括多个图案的半导体器件。

背景技术:

2.半导体器件可以包括多个图案。随着半导体器件变得高度集成,多个图案由于曝光工艺中出现的光干涉现象而彼此贴附(adhere)。例如,当多个图案是布线图案时,多个图案可能彼此贴附,因此,可能发生短路。

技术实现要素:

3.本发明构思涉及其中多个图案不彼此贴附的可靠的半导体器件。

4.根据本发明构思的一些实施方式,提供一种半导体器件,其包括第一金属布线图案区域以及在平面图中不与第一金属布线图案区域重叠的第二金属布线图案区域。第一金属布线图案区域包括第一图案。第二金属布线图案区域包括第二图案,该第二图案与第一图案间隔开并包括一条或更多条线。第一金属布线图案区域包括辅助图案,该辅助图案包括一条或更多条线。辅助图案与第二图案间隔开,与第二图案平行,并且在第一图案和第二图案之间。辅助图案的一端连接到第一图案。

5.根据本发明构思的一些实施方式,提供一种半导体器件,其包括第一金属布线图案区域和第二金属布线图案区域,该第二金属布线图案区域在平面图中不与第一金属布线图案区域重叠并包括第二图案,该第二图案包括一条或更多条线。第一金属布线图案区域包括包含第一图案的第一子图案区域以及与第一子图案区域相邻的第二子图案区域。第二子图案区域包括辅助图案,该辅助图案包括与第二图案平行并连接到第一图案的一条或更多条线。

6.根据本发明构思的一些实施方式,提供一种半导体器件,其包括第一金属布线图案区域以及在平面图中不与第一金属布线图案区域重叠的第二金属布线图案区域。第一金属布线图案区域包括第一图案,该第一图案包括块。第二金属布线图案区域包括在第一方向上与第一图案间隔开的第二图案,并且第二图案包括多个子图案,所述多个子图案包括在垂直于第一方向的第二方向上彼此间隔开的多条线。

7.第一金属布线图案区域包括辅助图案,该辅助图案在第二方向上在第一图案和第二图案之间。辅助图案包括多个子辅助图案,所述多个子辅助图案包括在第一方向上与第二图案的子图案平行并在第二方向上彼此间隔开的多条线。所述多个子辅助图案连接到第一图案。

附图说明

8.本发明构思的实施方式将由以下结合附图的详细描述被更清楚地理解,附图中:

9.图1和图2是示出根据本发明构思的一些实施方式的半导体器件的布局图(即,平面图);

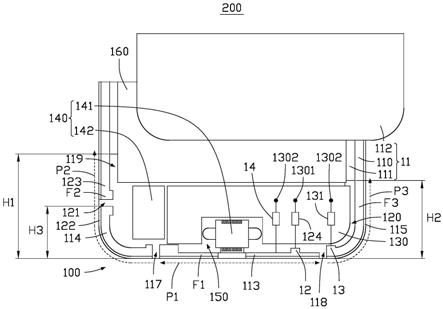

10.图3至图5是分别沿着图1的线iii-iii'、iv-iv'和v-v'截取的截面图,每个截面图示出了半导体器件的主要部分;

11.图6和图7是示出根据本发明构思的一些实施方式的半导体器件的布局图;

12.图8至图10是分别沿着图6的线viii-viii'、ix-ix'和x-x'截取的截面图,每个截面图示出了半导体器件的主要部分;

13.图11和图12是示出根据本发明构思的一些实施方式的半导体器件的布局图;

14.图13至图15是分别沿着图11的线xiii-xiii'、xiv-xiv'和xv-xv'截取的截面图,每个截面图示出了半导体器件的主要部分;

15.图16和图17是示出根据本发明构思的一些实施方式的半导体器件的布局图;以及

16.图18至图20是分别沿着图16的线xviii-xviii'、xix-xix'和xx-xx'截取的截面图,每个截面图示出了半导体器件的主要部分。

具体实施方式

17.在下文中,将参照附图详细描述本发明构思的实施方式。在下文中,实施方式被分开描述。然而,本发明构思可以通过实施方式之一形成,或通过实施方式当中的多个实施方式的组合形成。

18.在以下实施方式中,术语“区域(area)”可以被称为“区(region)”。

19.(实施方式1)

20.图1和图2是示出根据本发明构思的一些实施方式的半导体器件10-1的布局图。

21.具体地,图2是图1的局部区域的视图,示出了图2的半导体器件10-1。在图1和图2中,x-y平面可以与半导体衬底(图3至图5的sl1)平行。半导体器件10-1可以包括第一图案20-1、第二图案30-1和第一辅助图案40-1。

22.第一辅助图案40-1可以防止第二图案30-1贴附到第一图案20-1。第一辅助图案40-1可以被称为狭缝图案。第一辅助图案40-1可以被称为虚设图案。第一辅助图案40-1可以被称为第一加强图案或第一协助图案。

23.在一些实施方式中,第一图案20-1、第二图案30-1和第一辅助图案40-1可以是布线图案。第一图案20-1、第二图案30-1和第一辅助图案40-1可以是金属图案。

24.在一些实施方式中,第一图案20-1、第二图案30-1和第一辅助图案40-1可以包括选自银(ag)、金(au)、镍(ni)、铂(pt)、钯(pd)、铱(ir)、铑(rh)、钽(ta)、钨(w)、钛(ti)、钼(mo)、铝(al)和铜(cu)的元素或者使用该元素作为成分的合金材料或复合材料。

25.在以下实施方式中,主要通过使用布线图案或金属图案来描述第一图案20-1、第二图案30-1和第一辅助图案40-1。然而,本发明构思不限于此。

26.半导体器件10-1可以包括包含呈线形式(即,包括一条或更多条线)的第一图案20-1和第一辅助图案40-1的第一金属布线图案区域ar-1、以及包含呈线形式(即,包括一条或更多条线)的第二图案30-1的第二金属布线图案区域ar-2。第一金属布线图案区域ar-1可以包括包含第一图案20-1的第一子图案区域ar-1a和包含第一辅助图案40-1的第二子图案区域ar-1b。包括第一辅助图案40-1的第二子图案区域ar-1b和包括第二图案30-1的第二金属布线图案区域ar-2可以是线和空间图案区域,该线和空间图案区域包括彼此间隔开的线。

1的一端可以连接到第一图案20-1的第二内周os2。第一辅助图案40-1可以包括连接到第一图案20-1的第一辅助连接部分apl_cp1。

39.第一辅助图案40-1可以包括以线形式彼此间隔开的第一至第三子辅助图案40-1a、40-1b和40-1c。在图1中,第一辅助图案40-1中包括的第一至第三子辅助图案40-1a、40-1b和40-1c的数量被示出为5个。然而,本发明构思不限于此。

40.第一至第三子辅助图案40-1a、40-1b和40-1c可以通过第一分隔层50-1彼此分隔开。第一分隔层50-1可以是绝缘层,例如氧化物层或氮化物层。第一分隔层50-1可以包括第一子分隔层50-1a和第二子分隔层50-1b。

41.在第一至第三子辅助图案40-1a、40-1b和40-1c当中,第一子辅助图案40-1a最靠近第一图案20-1的第一部分20-1a。在第一至第三子辅助图案40-1a、40-1b和40-1c当中,第三子辅助图案40-1c最靠近第二图案30-1的第一子图案30-1a。第二子辅助图案40-1b在y方向上位于第一子辅助图案40-1a和第三子辅助图案40-1c之间。

42.第一子分隔层50-1a可以位于第一图案20-1的第一部分20-1a和第一子辅助图案40-1a之间。第一子分隔层50-1a可以位于第一图案20-1的第一部分20-1a的第一内周os1和第一子辅助图案40-1a之间。第二子分隔层50-1b可以位于第一子辅助图案40-1a和第二子辅助图案40-1b之间以及在第二子辅助图案40-1b和第三子辅助图案40-1c之间。

43.第一至第三子辅助图案40-1a、40-1b和40-1c可以以线形式与第二图案30-1的第一子图案30-1a和第二子图案30-1b平行地布置。第一至第三子辅助图案40-1a、40-1b和40-1c可以连接到第一图案20-1的第二部分20-1b。第一至第三辅助图案40-1a、40-1b和40-1c可以连接到第一图案20-1的第二内周os2。因为第一至第三子辅助图案40-1a、40-1b和40-1c在y方向上形成在第一子图案区域ar-1a和第二图案30-1之间,所以第二图案30-1的第二图案密度不会沿着y方向快速地改变,使得第二图案30-1可以被精确地形成。

44.如图2所示,第二图案30-1的第一子图案30-1a和第一至第三子辅助图案40-1a、40-1b和40-1c当中的最靠近第一子图案30-1a的第三子辅助图案40-1c可以通过第一至第三子辅助图案40-1a、40-1b和40-1c的布置而不彼此贴附。即使第一子辅助图案40-1a和第二子辅助图案40-1b彼此贴附,但是因为第一图案20-1不贴附到第二图案30-1,所以第一图案20-1和第二图案30-1可以分别独立地施加第一电压和第二电压。

45.这里,将描述诸如第一图案20-1、第二图案30-1和第一辅助图案40-1的宽度、间隔和节距的布置结构。

46.首先,第一图案20-1的第一部分20-1a可以在y方向上具有第一宽度w1a。在一些实施方式中,第一宽度w1a可以为100μm至300μm。第一图案20-1的第一部分20-1a可以与第一子辅助图案40-1a隔开第一距离s1a。在一些实施方式中,第一距离s1a可以为0.3μm至0.6μm。

47.第一辅助图案40-1中包括的第一至第三子辅助图案40-1a、40-1b和40-1c中的每个可以在y方向上具有第二宽度w2a。第一图案20-1的第一部分20-1a和第一辅助图案40-1可以集体地在y方向上具有第四宽度w4a。第一至第三子辅助图案40-1a、40-1b和40-1c可以与彼此的相邻子辅助图案隔开第二距离s2a。

48.即,如果第一辅助图案40-1的第一子辅助图案40-1a和第二子辅助图案40-1b彼此相邻,则它们可以彼此间隔开第二距离s2a。第一辅助图案40-1的第二子辅助图案40-1b和

第三子辅助图案40-1c可以彼此间隔开第二距离s2a。在第一至第三子辅助图案40-1a、40-1b和40-1c中,第二宽度w2a和第二距离s2a之一可以是最小特征尺寸。第一至第三子辅助图案40-1a、40-1b和40-1c可以以第一节距p1a在第二方向上布置。

49.第二图案30-1中包括的第一子图案30-1a和第二子图案30-1b中的每个可以在y方向上具有第三宽度w3a。第二图案30-1的第一子图案30-1a和第二子图案30-1b可以与彼此的相邻子图案间隔开第三距离s3a。在第一子图案30-1a和第二子图案30-1b中,第三宽度w3a和第三距离s3a之一可以是最小特征尺寸。第一子图案30-1a和第二子图案30-1b可以以第二节距p2a在第二方向上布置。

50.在一些实施方式中,在y方向上,第一宽度w1a可以大于第一辅助图案40-1的第二宽度w2a和/或第二图案30-1的第三宽度w3a。在y方向上,第一图案20-1(例如,第一部分20-1a)的第一宽度w1a可以大于第一辅助图案40-1的第二宽度w2a和/或第二图案30-1的第三宽度w3a,并且第一部分20-1a可以被称为宽图案。

51.第一辅助图案40-1和第二图案30-1可以呈在x方向上延伸的线的形式。第一辅助图案40-1的第二宽度w2a和/或第二图案30-1的第三宽度w3a可以小于第一图案20-1(例如,第一部分20-1a)的第一宽度w1a,并且第一辅助图案40-1和/或第二图案30-1可以被称为窄图案。

52.在一些实施方式中,第一距离s1a可以大于第二距离s2a和第三距离s3a。当第一距离s1a大于第二距离s2a和第三距离s3a时,在制造工艺期间,可以更精确地形成与第一子辅助图案40-1a相邻的第一图案20-1。

53.在一些实施方式中,第二宽度w2a可以等于第三宽度w3a。第二距离s2a可以等于第三距离s3a。第一节距p1a可以等于第二节距p2a。在一些实施方式中,第二宽度w2a和第三宽度w3a可以为0.1μm至0.2μm。第二距离s2a和第三距离s3a可以为0.1μm至0.2μm。

54.当第二宽度w2a等于第三宽度w3a、第二距离s2a等于第三距离s3a、并且第一节距p1a等于第二节距p2a时,第二金属布线图案区域ar-2和第二子图案区域ar-1b之间的图案均匀性可以改善,使得第二图案30-1和第一图案20-1可以被精确地形成。

55.在一些实施方式中,在y方向上,第一图案20-1(例如,第一部分20-1a)的第一宽度w1a可以不小于第一辅助图案40-1和/或第二图案30-1的最小特征尺寸(例如,第二宽度w2a、第二距离s2a、第三宽度w3a或第三距离s3a之一)的100倍。

56.在一些实施方式中,在y方向上,第一图案20-1的第一部分20-1a和第一辅助图案40-1集体所具有的第四宽度w4a可以不小于第一辅助图案40-1和/或第二图案30-1的最小特征尺寸(例如,第二宽度w2a、第二距离s2a、第三宽度w3a或第三距离s3a之一)的100倍。

57.具有上述布局的半导体器件10-1包括包含第一辅助图案40-1的第二子图案区域ar-1b,并将第一辅助图案40-1连接到第一图案20-1。在半导体器件10-1中,即使第一辅助图案40-1在y方向上贴附到第一图案20-1,第一图案20-1也不贴附到第二图案30-1,使得第一图案20-1和第二图案30-1可以独立地施加电压。

58.因此,半导体器件10-1可以通过包括不彼此贴附的第一图案20-1和第二图案30-1而提高元件可靠性。特别地,因为第一图案20-1和第二图案30-1不被短接,所以元件可靠性可以显著提高。

59.图3至图5是分别沿着图1的线iii-iii'、iv-iv'和v-v'截取的截面图,每个截面图

示出了半导体器件10-1的主要部分。

60.具体地,在图3至图5中,与图1和图2的附图标记相同的附图标记表示相同的元件。在图3至图5中,省略或简单描述了与图1和图2的内容相同的内容。在图3至图5中,z方向垂直于x-y平面。

61.在半导体器件10-1中,半导体层sl2可以位于半导体衬底sl1上。在一些实施方式中,半导体衬底sl1可以是硅衬底。半导体层sl2可以是其上提供元件部件(例如,晶体管和电容器)的材料层。第一图案20-1、第一辅助图案40-1、第二图案30-1、第一分隔层50-1和第二分隔层52可以位于半导体层sl2上。

62.如图3所示,在半导体层sl2上,第二图案30-1通过包括第一辅助图案40-1的第一辅助图案区域apl1与第一图案20-1分隔开。第二图案30-1可以包括在y方向上彼此间隔开的第一子图案30-1a和第二子图案30-1b。

63.第一子图案30-1a和第二子图案30-1b中的每个具有第三宽度w3a。第一子图案30-1a和第二子图案30-1b可以通过第二分隔层52彼此分隔开。第一子图案30-1a和第二子图案30-1b可以彼此间隔开第三距离s3a。第二分隔层52的宽度可以对应于第三距离s3a。

64.如图3和图5所示,在半导体层sl2上,第一辅助图案40-1可以包括在y方向上彼此间隔开的第一子辅助图案40-1a、第二子辅助图案40-1b和第三子辅助图案40-1c。第一子辅助图案40-1a、第二子辅助图案40-1b和第三子辅助图案40-1c中的每个可以具有第二宽度w2a。第二宽度w2a可以等于第三宽度w3a。

65.第一子辅助图案40-1a、第二子辅助图案40-1b和第三子辅助图案40-1c可以通过第一分隔层50-1(即,第二子分隔层50-1b)彼此分隔开。第一子辅助图案40-1a、第二子辅助图案40-1b和第三子辅助图案40-1c可以彼此间隔开第二距离s2a。第一分隔层50-1(即,第二子分隔层50-1b)的宽度可以对应于第二距离s2a。第一子图案30-1a和第三子辅助图案40-1c可以彼此间隔开第三距离s3a。第二距离s2a可以等于第三距离s3a。

66.第一图案20-1(即,第一部分20-1a)可以位于第一辅助图案区域apl1的一侧。第一子辅助图案40-1a可以与第一图案20-1(即,第一部分20-1a)间隔开第一距离s1a。通过使第一距离s1a大于第二距离s2a和第三距离s3a,可以防止第一图案20-1的第一部分20-1a贴附到第一子辅助图案40-1a。

67.如图4所示,第一辅助图案区域apl1中包括的第一辅助连接部分apl_cp1可以位于半导体层sl2上。第一辅助连接部分apl_cp1可以连接到第一图案20-1,即第二部分20-1b。

68.如上所述,半导体器件10-1的第一辅助图案区域apl1包括连接到第一图案20-1的第二部分20-1b的第一辅助连接部分apl_cp1。因此,在半导体器件10-1中,即使第一子辅助图案40-1a或第二子辅助图案40-1b在y方向上贴附到第一图案20-1,第一图案20-1(尤其是第一图案20-1的第一部分20-1a)和第二图案30-1也可以在y方向上不彼此贴附。

69.(实施方式2)

70.图6和图7是示出根据本发明构思的一些实施方式的半导体器件10-2的布局图。

71.具体地,图7是图6的局部区域的视图,示出了半导体器件10-2。图6和图7的半导体器件10-2与图1和图2的半导体器件10-1的不同之处在于第一金属布线图案区域ar-1中包括的第三子图案区域ar-1c的结构。在图6和图7中,与图1和图2的附图标记相同的附图标记表示相同的元件。在图6和图7中,省略或简单地描述了与图1和图2的内容相同的内容。

72.半导体器件10-2可以包括第一图案20-1、第二图案30-1和第二辅助图案40-2。第二辅助图案40-2可以对应于图1和图2的第一辅助图案40-1。第二辅助图案40-2可以由与第一辅助图案40-1相同的材料形成。

73.半导体器件10-2可以包括包含第一图案20-1和第二辅助图案40-2的第一金属布线图案区域ar-1、以及包含第二图案30-1的第二金属布线图案区域ar-2。第一金属布线图案区域ar-1可以包括包含第一图案20-1的第一子图案区域ar-1a和包含第二辅助图案40-2的第三子图案区域ar-1c。

74.第三子图案区域ar-1c可以包括第二辅助图案区域apl2。即,第二辅助图案区域apl2可以布置在第一金属布线图案区域ar-1的一部分中。第二辅助图案区域apl2可以对应于图1和图2的第一辅助图案区域apl1。

75.第二辅助图案区域apl2包括连接到第一图案20-1的第二辅助图案40-2。第二辅助图案区域apl2可以被布置,以便控制第一子图案区域ar-1a的图案密度。第二辅助图案40-2可以用于在曝光工艺期间抑制第二金属布线图案区域ar-2和第一子图案区域ar-1a之间的光干涉。

76.第二辅助图案40-2与第二图案30-1平行地布置,并连接到第一图案20-1。第二辅助图案40-2可以包括连接到第一图案20-1的第二辅助连接部分apl_cp2。

77.第二辅助图案40-2可以包括以线形式彼此间隔开的第四至第六子辅助图案40-2a、40-2b和40-2c。在图6中,第二辅助图案40-2中包括的第四至第六子辅助图案40-2a、40-2b和40-2c的数量被示出为3个。然而,本发明构思不限于此。

78.第四至第六子辅助图案40-2a、40-2b和40-2c可以通过第三分隔层50-2彼此分隔开。第三分隔层50-2可以是绝缘层,例如氧化物层或氮化物层。第三分隔层50-2可以包括第三子分隔层50-2a和第四子分隔层50-2b。

79.第四子辅助图案40-2a靠近第一图案20-1的第一部分20-1a。第六子辅助图案40-2c靠近第二图案30-1的第一子图案30-1a。第五子辅助图案40-2b在y方向上位于第四子辅助图案40-2a和第六子辅助图案40-2c之间。

80.第三子分隔层50-2a可以位于第一图案20-1的第一部分20-1a和第四子辅助图案40-2a之间。第三子分隔层50-2a可以位于第一图案20-1的第一部分20-1a的第一内周os1和第四子辅助图案40-2a之间。

81.第四子分隔层50-2b可以位于第四子辅助图案40-2a和第五子辅助图案40-2b之间和/或在第五子辅助图案40-2b和第六子辅助图案40-2c之间。第四至第六子辅助图案40-2a、40-2b和40-2c可以以线形式与第二图案30-1的第一子图案30-1a和第二子图案30-1b平行地布置。第四至第六子辅助图案40-2a、40-2b和40-2c可以连接到第一图案20-1的第二部分20-1b。

82.第一图案20-1的第一部分20-1a可以与第四子辅助图案40-2a隔开第一距离s1a。第四至第六子辅助图案40-2a、40-2b和40-2c中的每个可以在y方向上具有第二宽度w2a。第一图案20-1的第一部分20-1a和第二辅助图案40-2可以集体地在y方向上具有第四宽度w4a。第四至第六子辅助图案40-2a、40-2b和40-2c可以彼此间隔开第四距离s2b。

83.即,第四子辅助图案40-2a和第五子辅助图案40-2b可以彼此间隔开第四距离s2b,第五子辅助图案40-2b和第六子辅助图案40-2c可以彼此间隔开第四距离s2b。在第四至第

六子辅助图案40-2a、40-2b和40-2c中,第二宽度w2a可以是最小特征尺寸。第四至第六子辅助图案40-2a、40-2b和40-2c可以以第三节距p1b在第二方向上布置。

84.第一子图案30-1a和第二子图案30-1b可以以第二节距p2a在第二方向上布置。在一些实施方式中,在y方向上,第一宽度w1a可以大于第二辅助图案40-2的第二宽度w2a和/或第二图案30-1的第三宽度w3a。在y方向上,第一图案20-1(例如,第一部分20-1a)的第一宽度w1a可以大于第二辅助图案40-2的第二宽度w2a和/或第二图案30-1的第三宽度w3a,并且第一部分20-1a可以被称为宽图案。

85.第二辅助图案40-2和第二图案30-1可以呈在x方向上延伸的线的形式。第二辅助图案40-2的第二宽度w2a和/或第二图案30-1的第三宽度w3a可以小于第一图案20-1(例如,第一部分20-1a)的第一宽度w1a,并且第二辅助图案40-2和/或第二图案30-1可以被称为窄图案。

86.在一些实施方式中,第一距离s1a可以等于第四距离s2b。在一些实施方式中,第四距离s2b可以为0.3μm至0.6μm。第一距离s1a和第四距离s2b可以大于第三距离s3a。第三节距p1b可以大于第二节距p2a。

87.在一些实施方式中,在y方向上,第一图案20-1(例如,第一部分20-1a)的第一宽度w1a可以不小于第二辅助图案40-2和/或第二图案30-1的最小特征尺寸(例如,第二宽度w2a、第三宽度w3a和第三距离s3a之一)的100倍。

88.在一些实施方式中,在y方向上,第一图案20-1的第一部分20-1a和第二辅助图案40-2集体所具有的第四宽度w4a可以不小于第二辅助图案40-2和/或第二图案30-1的最小特征尺寸(例如,第二宽度w2a、第三宽度w3a和第三距离s3a之一)的100倍。

89.具有以上布局的半导体器件10-2包括包含第二辅助图案40-2的第三子图案区域ar-1c,并将第二辅助图案40-2连接到第一图案20-1。在半导体器件10-2中,即使第四子辅助图案40-2a和第五子辅助图案40-2b在y方向上贴附到第一图案20-1,第一图案20-1也不贴附到第二图案30-1。

90.图8至图10是分别沿着图6的线viii-viii'、ix-ix'和x-x'截取的截面图,每个截面图示出了半导体器件10-2的主要部分。

91.具体地,在图8至图10中,与图6和图7的附图标记相同的附图标记表示相同的元件。在图8至图10中,省略或简单地描述了与图6和图7的内容相同的内容。在图8至10中,z方向垂直于x-y平面。

92.在半导体器件10-2中,半导体层sl2可以位于半导体衬底sl1上。第一图案20-1、第二辅助图案40-2、第二图案30-1、第二分隔层52和第三分隔层50-2可以位于半导体层sl2上。

93.如图8所示,在半导体层sl2上,第二图案30-1通过包括第二辅助图案40-2的第二辅助图案区域apl2与第一图案20-1分隔开。第二图案30-1可以包括第一子图案30-1a和第二子图案30-1b。第一子图案30-1a和第二子图案30-1b通过第二分隔层52分隔开,并且第一子图案30-1a和第二子图案30-1b中的每个具有第三宽度w3a。第一子图案30-1a和第二子图案30-1b可以彼此间隔开第三距离s3a。

94.如图8和图10所示,在半导体层sl2上,第二辅助图案40-2可以包括在y方向上彼此间隔开的第四子辅助图案40-2a、第五子辅助图案40-2b和第六子辅助图案40-2c。第四子辅

3a、40-3b和40-3c。在图11中,第三辅助图案40-3中包括的第七至第九子辅助图案40-3a、40-3b和40-3c的数量被示出为3个。然而,本发明构思不限于此。

107.第七至第九子辅助图案40-3a、40-3b和40-3c可以通过第四分隔层50-3彼此分隔开。第四分隔层50-3可以是绝缘层,例如氧化物层或氮化物层。第四分隔层50-3可以包括第五子分隔层50-3a和第六子分隔层50-3b。

108.第七子辅助图案40-3a靠近第一图案20-1的第一部分20-1a。第九子辅助图案40-3c靠近第二图案30-1的第一子图案30-1a。第八子辅助图案40-3b在y方向上位于第七子辅助图案40-3a和第九子辅助图案40-3c之间。

109.第五子分隔层50-3a可以位于第一图案20-1的第一部分20-1a和第七子辅助图案40-3a之间。第五子分隔层50-3a可以位于第一图案20-1的第一部分20-1a的第一内周os1和第七子辅助图案40-3a之间。

110.第六子分隔层50-3b可以位于第七子辅助图案40-3a和第八子辅助图案40-3b之间以及在第八子辅助图案40-3b和第九子辅助图案40-3c之间。第七至第九子辅助图案40-3a、40-3b和40-3c可以以线形式与第二图案30-1的第一子图案30-1a和第二子图案30-1b平行地布置。第七至第九子辅助图案40-3a、40-3b和40-3c可以连接到第一图案20-1的第二部分20-1b。

111.第一图案20-1的第一部分20-1a可以与第七子辅助图案40-3a隔开第一距离s1a。第七子辅助图案40-3a和第八子辅助图案40-3b中的每个可以在y方向上具有第五宽度w2b。第五宽度w2b可以等于第一距离s1a。在一些实施方式中,第五宽度w2b可以为0.3μm至0.6μm。第九子辅助图案40-3c可以在y方向上具有第二宽度w2a。

112.第七子辅助图案40-3a和第八子辅助图案40-3b中的每个可以具有与第九子辅助图案40-3c的宽度不同的宽度。在一些实施方式中(例如,如图11和图12所示),第七子辅助图案40-3a和第八子辅助图案40-3b中的每个具有与第九子辅助图案40-3c的宽度不同的宽度。然而,第七至第九子辅助图案40-3a、40-3b和40-3c的宽度可以彼此不同。

113.第一图案20-1的第一部分20-1a和第三辅助图案40-3可以集体地在y方向上具有第四宽度w4a。第七至第九子辅助图案40-3a、40-3b和40-3c可以彼此间隔开第二距离s2a。

114.即,第七子辅助图案40-3a和第八子辅助图案40-3b可以彼此间隔开第二距离s2a,第八子辅助图案40-3b和第九子辅助图案40-3c可以彼此间隔开第二距离s2a。在第九子辅助图案40-3c中,第二宽度w2a可以是最小特征尺寸。第七子辅助图案40-3a和第八子辅助图案40-3b可以以第四节距p1c在第二方向上布置。第一子图案30-1a和第二子图案30-1b可以第二节距p2a在第二方向上布置。

115.在一些实施方式中,在y方向上,第一宽度w1a可以大于第三辅助图案40-3的第二宽度w2a和第五宽度w2b和/或第二图案30-1的第三宽度w3a。在一些实施方式中,第一距离s1a可以大于第二距离s2a和第三距离s3a。第四节距p1c可以大于第二节距p2a。

116.在一些实施方式中,在y方向上,第一图案20-1(例如,第一部分20-1a)的第一宽度w1a可以不小于第九子辅助图案40-3c和/或第二图案30-1的最小特征尺寸(例如,第二宽度w2a、第三宽度w3a和第三距离s3a之一)的100倍。

117.在一些实施方式中,在y方向上,第一图案20-1的第一部分20-1a和第三辅助图案40-3集体所具有的第四宽度w4a可以不小于第九子辅助图案40-3c和/或第二图案30-1的最

小特征尺寸(例如,第二宽度w2a、第三宽度w3a和第三距离s3a之一)的100倍。

118.具有以上布局的半导体器件10-3包括包含第三辅助图案40-3的第四子图案区域ar-1d,并将第三辅助图案40-3连接到第一图案20-1。在半导体器件10-3中,即使第七子辅助图案40-3a和第八子辅助图案40-3b在y方向上贴附到第一图案20-1,第一图案20-1也不贴附到第二图案30-1。

119.图13至图15是分别沿着图11的线xiii-xiii'、xiv-xiv'和xv-xv'截取的截面图,每个截面图示出了半导体器件10-3的主要部分。

120.具体地,在图13至图15中,与图11和图12的附图标记相同的附图标记表示相同的元件。在图13至图15中,省略或简单地描述了与图11和图12的内容相同的内容。在图13至图15中,z方向垂直于x-y平面。

121.在半导体器件10-3中,半导体层sl2可以位于半导体衬底sl1上。第一图案20-1、第三辅助图案40-3、第二图案30-1、第二分隔层52和第四分隔层50-3可以位于半导体层sl2上。

122.如图13所示,在半导体层sl2上,第二图案30-1通过包括第三辅助图案40-3的第三辅助图案区域apl3与第一图案20-1分隔开。第二图案30-1可以包括第一子图案30-1a和第二子图案30-1b。第一子图案30-1a和第二子图案30-1b通过第二分隔层52分隔开,并且第一子图案30-1a和第二子图案30-1b中的每个具有第三宽度w3a。第一子图案30-1a和第二子图案30-1b可以彼此间隔开第三距离s3a。

123.如图13和图15所示,在半导体层sl2上,第三辅助图案40-3可以包括在y方向上彼此间隔开的第七子辅助图案40-3a、第八子辅助图案40-3b和第九子辅助图案40-3c。第七子辅助图案40-3a和第八子辅助图案40-3b中的每个可以具有第五宽度w2b。第五宽度w2b可以大于第三宽度w3a。

124.第七子辅助图案40-3a、第八子辅助图案40-3b和第九子辅助图案40-3c可以通过第四分隔层50-3(即,第六子分隔层50-3b)彼此分隔开。第七子辅助图案40-3a、第八子辅助图案40-3b和第九子辅助图案40-3c可以彼此间隔开第二距离s2a。第四分隔层50-3(即,第六子分隔层50-3b)的宽度可以对应于第二距离s2a。第一子图案30-1a和第九子辅助图案40-3c可以彼此间隔开第三距离s3a。

125.第一图案20-1(即,第一部分20-1a)可以位于第三辅助图案区域apl3的一侧。第七子辅助图案40-3a可以与第一图案20-1(即,第一部分20-1a)隔开第一距离s1a。通过使第一距离s1a大于第二距离s2a或第三距离s3a,可以防止第一图案20-1的第一部分20-1a贴附到第七子辅助图案40-3a。

126.如图14所示,第三辅助图案区域apl3中包括的第三辅助连接部分apl_cp3可以位于半导体层sl2上。第三辅助连接部分apl_cp3可以连接到第一图案20-1,即第二部分20-1b。在半导体器件10-3中,即使第七子辅助图案40-3a和第八子辅助图案40-3b在y方向上贴附到第一图案20-1,第一图案20-1和第二图案30-1也可以不彼此贴附。

127.(实施方式4)

128.图16和图17是示出根据本发明构思的一些实施方式的半导体器件10-4的布局图。

129.具体地,图17是图16的局部区域的视图,示出了半导体器件10-4。图16和图17的半导体器件10-4与图1和图2的半导体器件10-1的不同之处在于第一金属布线图案区域ar-1

中包括的第五子图案区域ar-1e的结构。在图16和图17中,与图1和图2的附图标记相同的附图标记表示相同的元件。在图16和图17中,省略或简单地描述了与图1和图2的内容相同的内容。

130.半导体器件10-4可以包括第一图案20-1、第二图案30-1和第四辅助图案40-4。第四辅助图案40-4可以对应于图1和图2的第一辅助图案40-1。第四辅助图案40-4可以由与第一辅助图案40-1相同的材料形成。

131.半导体器件10-4可以包括包含第一图案20-1和第四辅助图案40-4的第一金属布线图案区域ar-1、以及包含第二图案30-1的第二金属布线图案区域ar-2。第一金属布线图案区域ar-1可以包括包含第一图案20-1的第一子图案区域ar-1a和包含第四辅助图案40-4的第五子图案区域ar-1e。

132.第五子图案区域ar-1e可以包括第四辅助图案区域apl4。即,第四辅助图案区域apl4可以布置在第一金属布线图案区域ar-1的一部分中。第四辅助图案区域apl4可以对应于图1和图2的第一辅助图案区域apl1。

133.第四辅助图案区域apl4包括连接到第一图案20-1的第四辅助图案40-4。第四辅助图案区域apl4可以被布置,以便控制第一子图案区域ar-1a的图案密度。第四辅助图案40-4可以用于在曝光工艺期间抑制第二金属布线图案区域ar-2和第一子图案区域ar-1a之间的光干涉。

134.第四辅助图案40-4与第二图案30-1平行地布置,并连接到第一图案20-1。第四辅助图案40-4可以包括连接到第一图案20-1的第四辅助连接部分apl_cp4。

135.第四辅助图案40-4可以包括以线形式彼此间隔开的第十至第十二子辅助图案40-4a、40-4b和40-4c。在图16中,第四辅助图案40-4中包括的第十至第十二子辅助图案40-4a、40-4b和40-4c的数量被示出为3个。然而,本发明构思不限于此。

136.第十至第十二子辅助图案40-4a、40-4b和40-4c可以通过第五分隔层50-4彼此分隔开。第五分隔层50-4可以是绝缘层,例如氧化物层或氮化物层。第五分隔层50-4可以包括第七子分隔层50-4a和第八子分隔层50-4b。

137.第十子辅助图案40-4a靠近第一图案20-1的第一部分20-1a。第十二子辅助图案40-4c靠近第二图案30-1的第一子图案30-1a。第十一子辅助图案40-4b在y方向上位于第十子辅助图案40-4a和第十二子辅助图案40-4c之间。

138.第七子分隔层50-4a可以位于第一图案20-1的第一部分20-1a和第十子辅助图案40-4a之间。第七子分隔层50-4a可以位于第一图案20-1的第一部分20-1a的第一内周os1和第十子辅助图案40-4a之间。

139.第八子分隔层50-4b可以位于第十子辅助图案40-4a和第十一子辅助图案40-4b之间以及在第十一子辅助图案40-4b和第十二子辅助图案40-4c之间。第十至第十二子辅助图案40-4a、40-4b和40-4c可以以线形式与第二图案30-1的第一子图案30-1a和第二子图案30-1b平行地布置。第十至第十二子辅助图案40-4a、40-4b和40-4c可以连接到第一图案20-1的第二部分20-1b。

140.第一图案20-1的第一部分20-1a可以与第十子辅助图案40-4a间隔开第五距离s1b。第十一子辅助图案40-4b和第十二子辅助图案40-4c中的每个可以在y方向上具有第五宽度w2b。第十子辅助图案40-4a可以在y方向上具有第六宽度w2c。

141.第十一子辅助图案40-4b和第十二子辅助图案40-4c中的每个可以具有与第十子辅助图案40-4a的宽度不同的宽度。在一些实施方式中,第六宽度w2c可以小于第五宽度w2b。第五距离s1b可以等于第六宽度w2c。在一些实施方式中,第五距离s1b和第六宽度w2c可以为0.3μm至0.4μm。

142.在一些实施方式中,第十一子辅助图案40-4b和第十二子辅助图案40-4c中的每个具有与第十子辅助图案40-4a的宽度不同的宽度。然而,第十至第十二子辅助图案40-4a、40-4b和40-4c的宽度可以彼此不同。

143.第一图案20-1的第一部分20-1a和第四辅助图案40-4可以集体地在y方向上具有第四宽度w4a。第十至第十二子辅助图案40-4a、40-4b和40-4c可以彼此间隔开第二距离s2a。

144.即,第十子辅助图案40-4a和第十一子辅助图案40-4b可以彼此间隔开第二距离s2a,第十一子辅助图案40-4b和第十二子辅助图案40-4c可以彼此间隔开第二距离s2a。在第十至第十二子辅助图案40-4a、40-4b和40-4c当中,第二距离s2a可以是最小特征尺寸。第十一子辅助图案40-4b和第十二子辅助图案40-4c可以以第五节距p1d在第二方向上布置。第一子图案30-1a和第二子图案30-1b可以以第二节距p2a在第二方向上布置。

145.在一些实施方式中,在y方向上,第一宽度w1a可以大于第四辅助图案40-4的第五宽度w2b和第六宽度w2c和/或第二图案30-1的第三宽度w3a。在一些实施方式中,第五距离s1b可以大于第二距离s2a和第三距离s3a。第五节距p1d可以大于第二节距p2a。

146.在一些实施方式中,在y方向上,第一图案20-1(例如,第一部分20-1a)的第一宽度w1a可以不小于第四辅助图案40-4和/或第二图案30-1的最小特征尺寸(例如,第二距离s2a、第三宽度w3a和第三距离s3a之一)的100倍。

147.在一些实施方式中,在y方向上,第一图案20-1的第一部分20-1a和第四辅助图案40-4集体所具有的第四宽度w4a可以不小于第四辅助图案40-4和/或第二图案30-1的最小特征尺寸(例如,第二距离s2a、第三宽度w3a和第三距离s3a之一)的100倍。

148.具有以上布局的半导体器件10-4包括包含第四辅助图案40-4的第五子图案区域ar-1e,并将第四辅助图案40-4连接到第一图案20-1。在半导体器件10-4中,即使第十子辅助图案40-4a和第十一子辅助图案40-4b在y方向上贴附到第一图案20-1,第一图案20-1也不贴附到第二图案30-1。

149.图18至图20是分别沿着图16的线xviii-xviii'、xix-xix'和xx-xx'截取的截面图,每个截面图示出了半导体器件10-4的主要部分。

150.具体地,在图18至图20中,与图16和图17的附图标记相同的附图标记表示相同的元件。在图18至图20中,省略或简单地描述了与图16和图17的内容相同的内容。在图18至图20中,z方向垂直于x-y平面。

151.在半导体器件10-4中,半导体层sl2可以位于半导体衬底sl1上。第一图案20-1、第四辅助图案40-4、第二图案30-1、第二分隔层52和第五分隔层50-4可以位于半导体层sl2上。

152.如图18所示,在半导体层sl2上,第二图案30-1通过包括第四辅助图案40-4的第四辅助图案区域apl4与第一图案20-1分隔开。第二图案30-1可以包括第一子图案30-1a和第二子图案30-1b。第一子图案30-1a和第二子图案30-1b通过第二分隔层52分隔开,并且第一

子图案30-1a和第二子图案30-1b中的每个具有第三宽度w3a。第一子图案30-1a和第二子图案30-1b可以彼此间隔开第三距离s3a。

153.如图18和图20所示,在半导体层sl2上,第四辅助图案40-4可以包括在y方向上彼此间隔开的第十子辅助图案40-4a、第十一子辅助图案40-4b和第十二子辅助图案40-4c。第十一子辅助图案40-4b和第十二子辅助图案40-4c中的每个可以具有第五宽度w2b。第十子辅助图案40-4a可以具有第六宽度w2c。第五宽度w2b可以大于第六宽度w2c。

154.第十子辅助图案40-4a、第十一子辅助图案40-4b和第十二子辅助图案40-4c可以通过第五分隔层50-4(即,第八子分隔层50-4b)彼此分隔开。第十子辅助图案40-4a、第十一子辅助图案40-4b和第十二子辅助图案40-4c可以彼此间隔开第二距离s2a。第五分隔层50-4(即,第八子分隔层50-4b)的宽度可以对应于第二距离s2a。第一子图案30-1a和第十二子辅助图案40-4c可以彼此间隔开第三距离s3a。

155.第一图案20-1(即,第一部分20-1a)可以位于第四辅助图案区域apl4的一侧。第十子辅助图案40-4a可以与第一图案20-1(即,第一部分20-1a)间隔开第五距离s1b。通过使第五距离s1b大于第二距离s2a或第三距离s3a,可以防止第一图案20-1的第一部分20-1a贴附到第十子辅助图案40-4a。

156.如图19所示,第四辅助图案区域apl4中包括的第四辅助连接部分apl_cp4可以位于半导体层sl2上。第四辅助连接部分apl_cp4可以连接到第一图案20-1,即第二部分20-1b。在半导体器件10-4中,即使第十子辅助图案40-4a和第十一子辅助图案40-4b在y方向上贴附到第一图案20-1,第一图案20-1和第二图案30-1也可以不彼此贴附。

157.虽然参照本发明构思的实施方式具体示出和描述了本发明构思,但是将理解,在不背离所附权利要求的精神和范围的情况下,可以在其中进行形式和细节上的各种改变。

158.本技术是基于2020年8月19日在韩国知识产权局提交的韩国专利申请第10-2020-0104155号并要求其优先权,该韩国专利申请的公开内容通过引用全文合并于此。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。