技术特征:

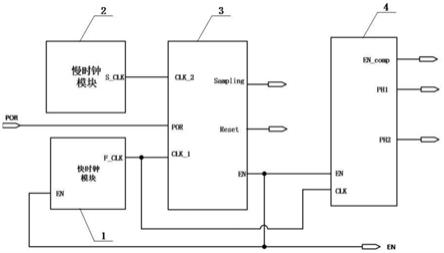

1.一种amr传感器开关芯片的时序控制电路架构,其特征在于,包括:快时钟电路(1)、慢时钟电路(2)、第一组合逻辑运算模块(3)和第二组合逻辑运算模块(4);所述快时钟电路(1)的f_clk输出端接所述第一组合逻辑运算模块(3)的clk_1输入端和所述第二组合逻辑运算模块(4)的clk输入端,所述快时钟电路(1)的en输入端接所述第一组合逻辑运算模块(3)的en输出端;所述慢时钟电路(2)的s_clk输出端接所述第一组合逻辑运算模块(3)的clk_2输入端;所述第一组合逻辑运算模块(3)的sampling输出端输出采样信号,en输出端输出检测使能信号;所述第二组合逻辑运算模块(4)的en_comp输出端输出比较器使能信号,斩波输出端输出两相斩波信号。2.根据权利要求1所述的一种amr传感器开关芯片的时序控制电路架构,其特征在于,所述第一组合逻辑运算模块(3)的por输入端接收上电复位信号,reset输出端输出复位信号,en输出端接所述第二组合逻辑运算模块(4)的en输入端;所述第二组合逻辑运算模块(4)的斩波输出端包括斩波ph1输出端和斩波ph2输出端。3.根据权利要求1所述的一种amr传感器开关芯片的时序控制电路架构,其特征在于,所述第一组合逻辑运算模块(3)包括:检测使能信号生成单元(31)、采样信号生成单元(32)和复位信号生成单元(33);所述检测使能信号生成单元(31)的输入端接所述慢时钟电路(2)的输出端并接收por信号,输出端输出检测使能信号;所述采样信号生成单元(32)的输入端接所述快时钟电路(1)的输出端并接收por信号,输出端输出采样信号;所述复位信号生成单元(33)的输入端接所述采样信号生成单元(32)的输出端,输出端接所述检测使能信号生成单元(31)和所述采样信号生成单元(32);所述复位信号生成单元(33)接收por信号,输出复位信号。4.根据权利要求3所述的一种amr传感器开关芯片的时序控制电路架构,其特征在于,所述检测使能信号生成单元(31)包括:二输入与门a1、触发器b6和驱动缓冲器d1;所述a1、b6和d1依次连接,a1的一个输入端接慢时钟电路(2)的s_clk输出端,另一个输入端接收por信号;d1的输出端输出检测使能信号;所述采样信号生成单元(32)包括:二输入与门a2和计数器;所述a2和计数器依次连接,a2的一个输入端接快时钟电路(1)的f_clk输出端,另一个输入端接收por信号;计数器的输出端输出采样信号;所述复位信号生成单元(33)包括:二输入与门a3、延时缓冲器e1和e2,以及反相器n1;所述e1和e2串联后接a3的一个输入端,a3的输出端接n1的输入端,n1的输出端输出复位信号;e1的输入端接计数器的输出端,a3的另一个输入端接收por信号,n1的输出端接计数器的reset端和b6的reset端。5.根据权利要求4所述的一种amr传感器开关芯片的时序控制电路架构,其特征在于,所述计数器包括:触发器b1、b2、b3、b4和b5,以及二输入与门a4;所述b1、b2、b3、b4和b5级联,每一个触发器的d输入端接q输出端;b1的ck输入端接快时钟电路(1)的f_clk输出端;b3的q输出端接a4的一个输入端,b5的q输出端接a4的另一个输入端;b1、b2、b3、b4和b5的复位端接收复位信号。6.根据权利要求1所述的一种amr传感器开关芯片的时序控制电路架构,其特征在于,所述第二组合逻辑运算模块(4)包括:二输入与门a5、a6、a7和a8,三输入与非门a9,触发器b6、b7、b8、b9和b10,延时缓冲器e3,反相器n2,以及两相非交叠时钟发生器f;

a5的一个输入端接收clk信号,另一输入端接收en信号,输出端接b6的ck输入端;b6、b7、b8和b9级联,b6的q输出端接a6的一个输入端,b7的q输出端接a7的一个输入端,b9的q输出端接a6的另一个输入端和a7的另一个输入端;a7的输出端依次连接e3和n2后接入a8的一个输入端,a8的另一个输入端接第一组合逻辑运算模块(3)的en输出端,a8的输出端接b6、b7、b8和b9的复位端;a7的输出端接b10的ck输入端,b10的q输出端接f的输入端,b10接收en信号;f的输出端输出两相斩波信号;b6、b7、b8、b9和b10的d输入端接q输出端;a5、a6的输出端和f的ph2输出端接a9的输入端,a9的输出端输出比较器使能信号。7.根据权利要求6所述的一种amr传感器开关芯片的时序控制电路架构,其特征在于,所述两相非交叠时钟发生器f包括:反相器n4、n5、n6、n7、n8和n9,二输入与非门a10和a11,以及延时缓冲器e4、e5、e6和e7;n4和n5串联后接入a10的一个输入端,a10、e4、e5、n6和n7依次串联,n4的输入端接b10的q输出端,n7输出斩波信号ph1;a11、e6、e7、n8和n9依次串联,a11的一个输入端连接在n4和n5之间,另一个输入端接n7的输出端,n9的输出端接a10的另一个输入端,n9输出斩波信号ph2。8.根据权利要求4所述的一种amr传感器开关芯片的时序控制电路架构,其特征在于,所述延时缓冲器包括:多个级联的偶数反相器。9.根据权利要求4所述的一种amr传感器开关芯片的时序控制电路架构,其特征在于,所述驱动缓冲器包括:多个级联的奇数反相器。10.一种如权利要求1-9中任意一项所述的时序控制电路架构的控制方法,其特征在于,包括以下步骤:慢时钟电路向第一组合逻辑运算模块发送s_clk信号;快时钟电路向第一组合逻辑运算模块发送f_clk信号;第一逻辑运算模块根据所述s_clk信号和所述f_clk信号进行逻辑运算,输出检测使能信号和采样信号;快时钟电路向第二组合逻辑运算模块发送f_clk信号;第一组合逻辑运算模块向第二组合逻辑运算模块发送en信号;第二组合逻辑运算模块根据所述f_clk信号和所述en信号进行逻辑运算,输出比较器使能信号和两相斩波信号;根据所述检测使能信号、所述采样信号、所述输出比较器使能信号和所述两相斩波信号,控制芯片的工作时序。

技术总结

本发明公开了一种AMR传感器开关芯片的时序控制电路架构,快时钟电路的F_CLK输出端接第一组合逻辑运算模块的CLK_1输入端和第二组合逻辑运算模块的CLK输入端,快时钟电路的EN输入端接第一组合逻辑运算模块的EN输出端;慢时钟电路的S_CLK输出端接第一组合逻辑运算模块的CLK_2输入端;第一组合逻辑运算模块的采用信号输出端输出采样信号,EN输出端输出检测使能信号;第二组合逻辑运算模块的比较器使能信号输出端输出比较器使能信号,斩波输出端输出两相斩波信号。本发明可降低磁阻开关芯片的工作电流,减小工作能耗,不易产生毛刺信号,采用斩波失调消除技术提高检测精度。用斩波失调消除技术提高检测精度。用斩波失调消除技术提高检测精度。

技术研发人员:肖登艳 陈忠志 彭卓 赵翔

受保护的技术使用者:成都芯进电子有限公司

技术研发日:2021.11.26

技术公布日:2022/2/18

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。