1.本发明涉及半导体制造技术领域,特别涉及一种非易失性存储器版图及非易失性存储器。

背景技术:

2.闪存(flash)作为一种安全、快速的存储体,以其体积小、容量大、成本低、掉电数据不丢失等一系列优点,成为了嵌入式系统中数据和程序最主要的载体。近年来,随着智能电子产品市场的飞速发展,各类mcu(micro controller unit,微控制器)及soc(system-on-chip,片上系统)的使用已经深入到汽车电子、工业控制和医疗产品等日常生活的各个方面。在现有的非易失性存储器(nord flash)中,用于实现电连接两个控制栅的连接结构的形状通常呈z字型,而随nord flash器件的微缩,器件设计规则越来越小,现有的控制栅的连接结构由于工艺上的限制已不再适用。

技术实现要素:

3.本发明的目的在于提供一种非易失性存储器版图及非易失性存储器,以增大非易失性存储器的控制栅中的连接结构的工艺窗口。

4.为实现上述目的,本发明提供一种非易失性存储器版图,所述非易失性存储器版图包括:控制栅版图,包括沿着第一方向平行排布并沿着第二方向延伸的多个控制栅图形组,所述第一方向与所述第二方向垂直,每个所述控制栅图形组包括两个呈镜像对称的控制栅图形,其中,所述栅极图形包括呈直条形且沿所述第二方向延伸的栅极图形和从所述栅极图形的中间位置伸出的凸起图形,所述凸起图形在所述第一方向上凸出于所述栅极图形并与所述栅极图形连接为一体,且每个所述控制栅图形组中的两个所述凸起图形相背设置;

5.字线版图,包括沿着所述第一方向平行排布并沿着所述第二方向延伸的多个字线图形组,每个所述控制栅图形组中的所述两个控制栅图形之间设置有一个所述字线图形组,其中,每个所述字线图形组包括沿着所述第二方向间隔设置的两个呈直条形的字线图形,所述两个字线图形之间的间隔区域对准所述凸起图形。

6.可选的,在所述的非易失性存储器版图中,每个所述栅极图形均包括平行排列的第一栅极图形和第二栅极图形,所述凸起图形设置于所述第一栅极图形和所述第二栅极图形之间并与所述第一栅极图形和所述第二栅极图形连接为一体。

7.可选的,在所述的非易失性存储器版图中,所述非易失性存储器版图还包括接触孔版图,所述接触孔版图包括多个接触孔图形组,每个所述控制栅图形组中设有一个所述接触孔图形组,其中,每个所述接触孔图形组包括两个接触孔图形,所述两个接触孔图形分别与所述控制栅图形组的两个所述控制栅图形相对应。

8.可选的,在所述的非易失性存储器版图中,每个所述接触孔图形在所述控制栅版图上的投影均位于所述凸起图形内。

9.可选的,在所述的非易失性存储器版图中,每个所述接触孔图形组中的所述两个所述接触孔图形在位置上相错设置。

10.可选的,在所述的非易失性存储器版图中,所述非易失性存储器版图还包括有源区版图,所述有源区版图包括沿着所述第二方向平行排布并沿着所述第一方向延伸的至少两个有源区图形,每个所述字线图形横跨所有的有源区图形。

11.可选的,在所述的非易失性存储器版图中,每个所述控制栅图形横跨所有的所述有源区图形。

12.基于同一发明构思,本发明还提供一种非易失性存储器,所述的非易失性存储器版图形成,所述非易失性存储器包括:

13.半导体衬底;

14.形成于所述半导体衬底上的多个控制栅结构组,所述多个控制栅结构组沿着第一方向平行排布并沿着第二方向延伸,所述第一方向与所述第二方向垂直,每个所述控制栅结构组包括两个呈镜像对称的控制栅结构,其中,每个所述控制栅结构包括呈直条形且沿所述第二方向的栅极部和从所述栅极部的中间位置伸出的凸起部,所述凸起部在所述第一方向上凸出于所述栅极部并与所述栅极部连接为一体,且每个所述控制栅图形组中的所述两个凸起部相背设置;

15.形成于所述半导体衬底上的多个字线结构组,所述多个字线结构组沿着所述第一方向平行排布并沿着所述第二方向延伸,每个所述控制栅结构组的所述两个控制栅结构之间形成有一个所述字线结构组,其中,每个所述字线结构组包括沿着所述第二方向间隔设置的两个呈直条形的字线结构,所述两个字线结构之间的间隔开口对准所述凸起部。

16.可选的,在所述的非易失性存储器中,每个所述栅极部包括平行排列的第一栅极部和第二栅极部,所述凸起部设置于所述第一栅极部和所述第二栅极部之间并与所述第一栅极部和所述第二栅极部连接为一体。

17.可选的,在所述的非易失性存储器中,所述非易失性存储器还包括:形成于所述多个控制栅结构组上的多个接触结构组,其中,每个所述控制栅结构组上形成有一个所述接触结构组,每个所述接触结构组包括两个接触结构,所述两个接触结构分别与所述控制栅结构组中的所述两个控制栅结构相对应。

18.可选的,在所述的非易失性存储器中,每个所述接触结构位于各自对应的所控制栅结构的凸起部上并与所述凸起部电连接。

19.可选的,在所述的非易失性存储器中,每个所述接触结构组中的所述两个接触结构在位置上相错设置。

20.在本发明提供的非易失性存储器版图及非易失性存储器中,所述非易失性存储器版图包括控制栅版图和字线版图,所述控制栅版图包括多个控制栅图形组,每个所述控制栅图形组包括两个呈镜像对称的控制栅图形。其中,所述栅极图形包括呈直条形且沿所述第二方向延伸的栅极图形和从所述栅极图形的中间位置伸出的凸起图形,所述凸起图形在所述第一方向上凸出于所述栅极图形并与所述栅极图形连接为一体,每个所述控制栅图形组中的两个所述凸起图形相背设置。所述字线版图包括多个字线图形组,每个所述控制栅图形组中的所述两个控制栅图形之间设置有一个所述字线图形组,其中,每个所述字线图形组包括沿着所述第二方向间隔设置的两个呈直条形的字线图形,所述两个字线图形之间

的间隔区域对准所述凸起图形,即字线图形之间的间隔区域靠近凸起图形的背部,如此可使得存储器中的字线结构与控制栅结构的凸起部相间隔,由此可避免控制栅结构的凸起部与字线之间发生短路,并且增大了控制栅结构中的凸起部的工艺窗口。此外,由于每个所述控制栅结构组中的两个凸起部相背设置,相比现有技术,可减少连接结构(凸起部作为连接结构)占用的面积。

附图说明

21.图1~4是本发明实施例的非易失性存储器版图的示意图;

22.图5~图6是本发明实施例的非易失性存储器的结构示意图;

23.其中,附图标记说明如下:

24.110-控制栅图形组;111、112-控制栅图形;1111、1121-栅极图形;1111a第一栅极图形;1111b-第二栅极图形;1112、1122-凸起图形;

25.120-字线图形组;121、122-字线图形;

26.130-接触孔图形组;131、132-接触孔图形;

27.140-有源区图形;

28.200-半导体衬底;201-浅沟槽隔离结构;202-栅间介质层;

29.210-控制栅结构组;211、212-控制栅结构;2111、2121-栅极部;2112、2122-凸起部;2112-控制栅结构;2111a、2111b、2112a、2112b-栅极部;

30.220-字线结构组;220a-间隔开口;221、222-字线结构;

31.230-接触结构组;231、232-接触结构。

具体实施方式

32.以下结合附图和具体实施例对本发明提出的非易失性存储器版图及非易失性存储器作进一步详细说明。根据下面说明,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

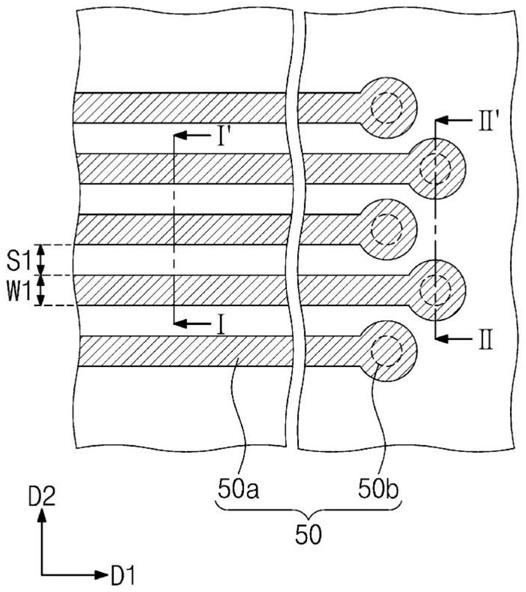

33.图1是本发明实施例的非易失性存储器版图的示意图。如图1所示,所述非易失性存储器版图包括控制栅版图,所述控制栅版图用于形成非易失性存储器多个控制栅结构。所述控制栅版图包括沿着第一方向y平行排布并沿着第二方向x延伸的多个控制栅图形组110,所述第一方向y与所述第二方向x垂直,每个所述控制栅图形组110包括两个呈镜像对称的控制栅图形111和控制栅112,由于控制栅图形111和控制栅图形112呈镜像对称,由此能够使控制栅图形组110的形状一致性。

34.如图1所示,本实施例中,控制栅图形111包括一个呈直条形且沿所述第二方向x延伸的栅极图形1111和从所述栅极图形1111的中间位置伸出的凸起图形1112。控制栅图形112包括一个呈直条形且沿所述第二方向x延伸的栅极图形1121和从所述栅极图形1121的中间位置伸出的凸起图形1122。所述栅极图形111、112用于形成非易失性存储器中的控制栅结构,所述凸起图形1112、1121用于形成存储器中的凸起部,以实现两个栅极部之间的电连接。

35.其中,每个所述凸起图形1122在所述第一方向y上凸出于所述栅极图形1121并与

所述栅极图形1121连接为一体,即所述控制栅图形111呈一凸字形;每个所述凸起图形1112在所述第一方向上凸出于所述栅极图形112并与所述栅极图形1122连接为一体,即所述控制栅图形112呈一凸字形,也就是说,所述栅极图形1121与所述栅极图形1121远离所述凸起图形1112的线段为平齐的线段。每个所述控制栅图形组110中的凸起图形1112和凸起图形1122相背设置,即凸起图形1112与凸起图形1122的位置位于平行于第一方向y上的一条直线上,且凸起图形1112凸出于栅极图形1111的方向与凸起图形1122凸出于栅极图形1121的方向相背。

36.进一步的,每个所述栅极图形1111均包括平行排列的第一栅极图形1111a和第二栅极图形1111b,所述凸起图形1112设置于所述第一栅极图形和1111a所述第二栅极图形1111b之间并与所述第一栅极图形1111a和所述第二栅极图形1111b连接为一体。每个所述栅极图形1121均包括平行排列的第一栅极图形和第二栅极图形,所述凸起图形1122设置于所述第一栅极图形和所述第二栅极图形之间并与所述第一栅极图形和所述第二栅极图形连接为一体。其中,所述第一栅极图形1111a和所述第二栅极图形1111b用于形成相邻两个存储阵列(cell array)的栅极部(在此指控制栅),所述凸起图形1122用于形成凸起部,凸起部可作为连接结构,用于连接相邻两个存储阵列(cell array)的栅极部(在此指器件中的第一栅极部和第二栅极部),并为器件提供接触区(pickup)的区域。

37.本实施例中,如图2所示,所述非易失性存储器版图还包括字线版图,所述字线版图结构包括沿着所述第一方向y平行排布并沿着所述第二方向x延伸的多个字线图形组120,所述字线图形组120用于形成非易失性存储器中的字线结构组。每个所述控制栅图形组110中的所述两个控制栅图形111、112之间设置有一个所述字线图形组120。每个所述字线图形组120包括沿着所述第二方向x间隔设置的两个字线图形121、122,所述字线图形121和所述字线图形122之间具有间隔区域a,所述间隔区域a对准所述凸起图形1112、1122。由于所述字线图形121和字线图形122之间具有间隔区域a,增大了控制栅结构的凸起部的工艺窗口,并可避免控制栅结构的凸起部与字线之间发生短路。以及减小了实际的非易失性存储器中的控制栅结构的凸起部的尺寸,从而减小了凸起部占用的面积。

38.如图3所示,本实施例中,所述非易失性存储器版图还包括接触孔版图结构,所述接触孔版图结构包括多个接触孔图形组130,每个所述控制栅图形组110中设有一个所述接触孔图形组130,其中,每个所述接触孔图形组130包括两个接触孔图形131、132,所述接触孔图形131与所述控制栅图形111相对应,所述接触孔图形132与所述控制栅图形112相对应。

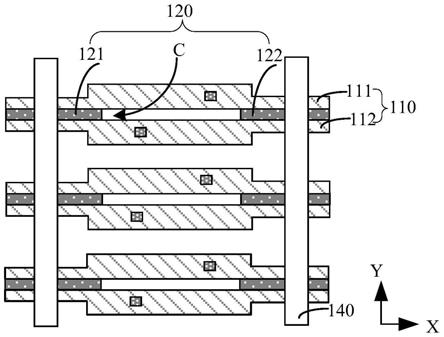

39.其中,所述接触孔图形131、132用于定义存储器中的接触结构的位置。较佳的,每个所述接触孔图形组130中的接触孔图形131和接触孔图形132在位置上相错设置,如此一来,可避免接触孔图形131和接触孔图形132连接在一起,由此避免非易失性存储器中相邻的两个接触结构连接在一起,从而避免造成短路。

40.如图4所示,所述非易失性存储器版图还包括有源区版图,所述有源区版图包括沿着所述第二方向x平行排布并沿着所述第一方向y延伸的至少两个有源区图形140,所述有源区图形140用于定义非易失性存储器中的有源区的位置。

41.本实施例中,每个所述控制栅图形111、112横跨所有的所述有源区图形140,每个所述字线图形121、122横跨所有的所述有源区图形140。

42.需要说明的是,在版图结构中,各层版图结构的图形通常使用最小设计规则。为此,本实施例中,单个所述有源区图形140的最小面积满足drc(desigh rule check,设计限制)规则。

43.基于同一发明构思,本发明还提供一种非易失性存储器,所述非易失性存储器采用本实施提供的非易失性存储器版图形成。

44.图5~图6是本发明实施例的非易失性存储器的结构示意图。如图5和图6所示,所述非易失性存储器包括:半导体衬底200;形成于所述半导体衬底200上的多个控制栅结构组210,所述多个控制栅结构组210沿着第一方向y平行排布并沿着第二方向x延伸,所述第一方向y与所述第二方向x垂直,在此,所述第一方向y和第二方向x均为半导体衬底200的水平方向。每个所述控制栅结构组210包括呈镜像对称的控制栅结构211和控制栅结构212。

45.其中,每个所述控制栅结构211包括呈直条形且沿着所述第二方向x延伸的栅极部2111和从所述栅极部2111的中间位置伸出的凸起部2112,所述凸起部2112在所述第一方向y上凸出于所述栅极部2111并与所述栅极部2111连接为一体。每个所述控制栅结构212包括呈直条形且沿着所述第二方向x延伸的栅极部2121和从所述栅极部2121的中间位置伸出的凸起部2122,所述凸起部2122在所述第一方向y上凸出于所述栅极部2121并与所述栅极部2121连接为一体。其中,所述栅极部包括第一栅极部2112a和第二栅极部2112b,第一栅极部2112a和第二栅极部2112b可作为相邻两个存储阵列(cell array)的控制栅,所述凸起部2112、2122用于连接相邻两个存储阵列(cell array)的控制栅(即第一栅极部2112a和第二栅极部2112b),以实现相邻两个存储阵列(cell array)的控制栅之间的电连接,并为器件提供接触区(pickup)的区域。

46.所述半导体衬底200的材料为硅;在其他实施例中,所述半导体衬底200的材料还可以为锗、锗化硅、碳化硅、砷化镓或镓化铟。

47.本实施例中,每个所述控制栅结构组110中的凸起部2112和凸起部2122相背设置,如此一来,可以增大字线结构221和字线结构222与凸起部2112、2122之间的间距,避免了控制栅结构的凸起部2112与字线结构221、222之间发生短路,以及增大了控制栅结构中的凸起部2112和凸起部2122的工艺窗口。此外,还可增大形成于凸起部2112、2122上的接触结构的工艺窗口,避免接触结构与字线结构之间发生短路。本实施例中,所述控制栅结构211、212的材质可以为掺杂的多晶硅。

48.此外,所述半导体衬底200与所述多个控制栅结构组210之间还形成有浮栅层和栅间介质层102,以及浅沟槽隔离结构101,所述浅沟槽隔离结构101贯穿所述浮栅层和所述浮栅氧化层。其中,栅间介质层102包括自下而上依次堆叠的第一氧化层、氮化层和第二氧化层,为了更好的阐述本实施例的非失性存储器,省略了浮栅层和栅间介质层的描述,同时省略了浮栅层的图示。以及,所述凸起部2112、2122对准所述浅沟槽隔离结构101。

49.如图5所示,所述非易失性存储器还包括形成于所述半导体衬底200的多个字线结构组220,所述多个字线结构组220沿着所述第一方向y平行排布并沿着所述第二方向x延伸,其中,每个所述字线结构组220包括沿着所述第二方向x间隔设置的两个呈直条形的字线结构221、222,字线结构221与字线结构222之间具有间隔区域a,且字线结构221与字线结构222之间的间隔区域a对准凸起部2112,即字线结构221与字线结构222之间的间隔区域靠近凸起部2112的背部,如此一来,可以增加形成于凸起部上的接触结构与字线结构221、221

之间的距离,避免字线结构221、222与接触结构之间发生短路。本实施例中的字线结构221、222的材质为多晶硅。

50.本实施例中,非易失性存储器还包括形成于所述多个控制栅结构组210上的多个接触结构组230,其中,每个所述控制栅结构组210上形成有一个所述接触结构组230,所述接触结构组230包括两个接触结构231、232,所述接触结构231和所述接触结构232分别与所述控制栅结构2111和控制栅结构2112相对应,即接触结构231与控制栅结构2111相对应,接触结构232与控制栅结构2112相对应。其中,所述接触结构231、232的材质为金属,例如钨或者铜。

51.优选的方案中,每个所述接触结构组230的所述接触结构231和接触结构232在位置上相错设置,如来一来,可避免接触结构231和接触结构232之间的短路。

52.此外,本实施例中,所述非易失性存储器为nord闪存。

53.综上可见,在本发明提供的非易失性存储器版图及非易失性存储器中,所述非易失性存储器版图包括控制栅版图和字线版图,所述控制栅版图包括多个控制栅图形组,每个所述控制栅图形组包括两个呈镜像对称的控制栅图形。其中,所述栅极图形包括呈直条形且沿所述第二方向延伸的栅极图形和从所述栅极图形的中间位置伸出的凸起图形,所述凸起图形在所述第一方向上凸出于所述栅极图形并与所述栅极图形连接为一体,每个所述控制栅图形组中的两个所述凸起图形相背设置。所述字线版图包括多个字线图形组,每个所述控制栅图形组中的所述两个控制栅图形之间设置有一个所述字线图形组,其中,每个所述字线图形组包括沿着所述第二方向间隔设置的两个呈直条形的字线图形,所述两个字线图形之间的间隔区域对准所述凸起图形,即字线图形之间的间隔区域靠近凸起图形的背部,如此可使得存储器中的字线结构与控制栅结构的凸起部相间隔,由此可避免控制栅结构的凸起部与字线之间发生短路。

54.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。