1.本发明涉及一种半导体模块及其制造方法,且特别是涉及一种具有压电层的半导体模块及其制造方法。

背景技术:

2.现有的堆叠式半导体装置(stacked semiconductor apparatus)通常利用接合(bonding)技术使用个别半导体元件相互堆叠连接来完成。常见的接合技术包含打线接合(wire bonding)、倒装芯片(flip chip)、硅穿孔(through silicon via,简称tsv)等。

3.打线接合技术是利用金属线材完成半导体元件,例如芯片(chip),与引线架(lead frame)或外部电路之间的电连接,依据焊接点的形状不同可分为楔型接合(wedge bonding)及球型接合(ball bonding)。倒装芯片技术是将芯片的正面翻转,利用锡铅球或凸块直接连接至基板。硅穿孔技术则是利用贯穿芯片的孔洞及填充于孔洞中的导电材料来完成垂直堆叠的半导体元件之间的电互连。

4.以现有技术中常见的前端模块(front end module,简称fem)为例,事先在不同的制作工艺中分别制造声表面波(surface acoustic wave,简称saw)滤波器与集成电路基板(ic substrate),然后利用打线接合技术、倒装芯片技术、硅穿孔技术等接合技术来使声表面波滤波器与集成电路基板电连接,所形成的堆叠式半导体装置。然而,现有的接合技术面临许多严峻的挑战,例如接合声表面波滤波器与集成电路基板时的对准精确性、焊线品质的稳定性、额外的接合工序使个别半导体元件,例如声表面波滤波器,难以被良好地控制、以及额外的接合工序提高制造成本并降低整体半导体设备的整合度与效能等问题。

5.因此,如何提出一种改善半导体模块的整合度的技术是本领域业者不断努力的目标。

技术实现要素:

6.本发明涉及一种半导体模块及其制造方法,可提高半导体模块的整合度、控制性与效能、并减少额外的接合工序,以改善前述现有问题。

7.本发明的一方面提出一种半导体模块。半导体模块包括一基板、一屏蔽结构及一压电层(piezoelectric layer)。基板包括一前侧与至少一半导体元件形成于前侧上。屏蔽结构形成于至少一半导体元件上。压电层形成于屏蔽结构上。

8.本发明的另一方面提出一种用以制造一半导体模块的方法。方法包括以下步骤:提供一基板,基板包括一前侧与至少一半导体元件形成于前侧上;在至少一半导体元件上形成一屏蔽结构;以及在屏蔽结构上形成一压电层。

9.根据上述实施例,在本发明所提供的半导体模块中,是先在前端模块上形成屏蔽结构,并且采用例如是沉积或接合技术直接在屏蔽结构上形成压电层,直接再进行后段工序以形成一或多个声表面波滤波器。相较于现有的技术方案,事先以制造工序形成滤波器,再采用额外的接合工序将已制作完成的滤波器安装至半导体模块的前端模块上,本发明所

提供的半导体模块可避免由于额外的接合工序而产生的对准精确性问题与焊线品质不稳定的问题。另外,由于不需要额外的接合工序,本发明提供的半导体模块中的声表面波滤波器可被良好地控制,且同时可改善半导体模块的整合度与效能,并降低制造成本

10.为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合所附的附图详细说明如下。

附图说明

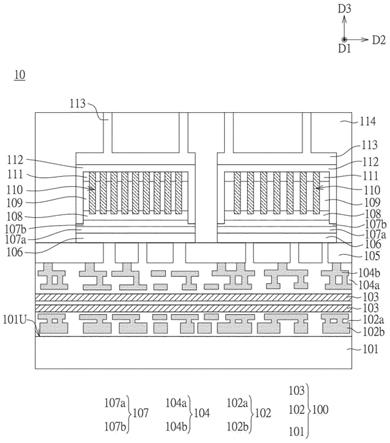

11.图1是本发明一实施例的半导体模块的示意图;

12.图2a是本发明一实施例的导电结构的俯视示意图;

13.图2b是本发明一实施例的导电结构的俯视示意图;

14.图3是本发明另一实施例的半导体模块的示意图;

15.图4a~图4e是本发明一实施例的半导体模块的制造方法示意图。

具体实施方式

16.以下结合附图和具体实施例,对本发明进行详细描述。

17.本发明涉及一种半导体模块及其制造方法,半导体模块包括基板、屏蔽结构及压电层。基板包括前侧与至少一半导体元件形成于前侧上。屏蔽结构形成于至少一半导体元件上。压电层形成于屏蔽结构上。通过此些配置,半导体模块可不需要额外的接合工序,进而提升半导体模块的整合度、控制性与效能。

18.需注意的是,本发明并非显示出所有可能的实施例,未于本发明提出的其他实施态样也可能可以应用。再者,图上的尺寸比例并非按照实际产品等比例绘制。因此,说明书和图示内容仅作叙述实施例的用途,而非用来作为限缩本发明保护范围。另外,实施例中的叙述,例如细部结构、制作工艺步骤和材料应用等等,仅为举例说明之用,并非对本发明欲保护的范围做限缩。实施例的步骤和结构的各细节可在不脱离本发明的精神和范围内根据实际应用制作工艺的需要而加以变化与修饰。以下是以相同/类似的符号表示相同/类似的元件做说明。

19.此外,在本篇内容中,所有方向性术语,例如「上表面」、「下表面」、「前侧」和「后侧」等,仅用于解释装置在某一特定姿态(例如是附图所示的姿态)下各部件之间的相对位置或相对方位关系。因此,如果在一个附图中所示的装置翻转,该方向性指示也相应地随之改变,但不应影响各部件之间的相对位置或相对方位关系。

20.此外,在本篇内容中如涉及「第一」、「第二」等叙述,其仅用于描述目的,而不能理解为指示或暗示其相对重要性或制造组装顺序,也不能理解为隐含所形容的技术特征的数量。

21.图1是本发明一实施例的半导体模块10的示意图。半导体模块10包括基板100、屏蔽结构107及压电层109。基板100包括至少一个形成于基板100前侧的半导体元件103。屏蔽结构107形成于半导体元件103上。压电层109形成于屏蔽结构107上。

22.在一实施例中,基板100可包括承载件101、第一线路层102与多个半导体元件103。承载件101提供于第一方向d1与第二方向d2交错形成的平面上,承载件101的上表面101u垂直于第三方向d3,第一方向d1、第二方向d2与第三方向d3两两相互垂直。半导体元件103形

成于承载件101的上表面101u上,第一线路层102设置于半导体元件103与承载件101的上表面101u之间以提供半导体元件103与承载件101之间的电连接。

23.在一实施例中,基板100的前侧可理解为基板100包括集成电路的一侧,前侧相对于没有设置集成电路的后侧;换言之,基板100的前侧可理解为在第三方向d3上和承载件101的上表面101u同方向。在一实施例中,承载件101可以是一种承载晶圆(handling wafer),或是含硅基板。

24.在一实施例中,第一线路层102可包括层间介电材料(interlayer dielectric,ild)102a。在一实施例中,可采用布线技术,在层间介电材料102a中形成金属内连线(interconnection)102b,以制备第一线路层102。在一实施例中,第一线路层102可包括重新布线层(redistribution layer,简称rdl)。

25.半导体元件103可以是一种用于无线通讯领域的射频(rf)前端元件。例如在一实施例中,半导体元件103可以是一种具有嵌入式电感器(embedded inductors)、导线和耦合器(couplers)的功能性基板。在另一实施例中,半导体元件103可以是一种能与控制器、功率放大器(power amplifiers)和其他半导体开关整合在同一个集成电路(ic)基板上的前端模块(front end module,fem)。

26.屏蔽结构107可形成于半导体元件103上方。更具体地,屏蔽结构107沿着第三方向d3形成于半导体元件103上方,使屏蔽结构107和承载件101分别设置于半导体元件103的相对侧。半导体模块10还可包括第二线路层104和金属层105,设置于屏蔽结构107和半导体元件103之间。金属层105可以是一种金属焊垫,具有纳米级别的厚度。在一实施例中,金属层105的厚度可介于0.5微米(μm)至1毫米(mm)之间。

27.第二线路层104可设置于金属层105与半导体元件103之间,以提供金属层105与半导体元件103之间的电连接。在一实施例中,第二线路层104的结构与第一线路层102类似,可包括层间介电材料104a和金属内连线104b。在另一实施例中,第二线路层104可包括重新布线层。

28.在一实施例中,形成屏蔽结构107的材料可包括介电材料或磁性材料。例如,磁性材料可包括铁氧体(ferrite)、金属软磁(soft magnetic)材料等;金属软磁材料可包括铁(fe)、钴(co)、镍(ni)或其合金等。在另一实施例中,形成屏蔽结构107的材料可包括氮化硅(sin)、低介电常数材料、铪氧化物(hfo

x

)、二氧化硅(sio2)、氮化铝(aln)、氧化铝(al2o3)、氧化锌(zno)、锆钛酸铅(pzt)、钽酸锂(litao3)、铌酸锂(linbo3)或四氧化三铁(fe3o4)等。本发明不限制用于屏蔽结构107的材料种类。

29.在本实施例中,屏蔽结构107可包括第一屏蔽层107a与第二屏蔽层107b。第一屏蔽层107a具有第一密度,且在第三方向d3上堆叠于半导体元件103上方。第二屏蔽层107b具有第二密度且堆叠于第一屏蔽层107a上方。其中,第一屏蔽层107a的第一密度大于第二屏蔽层107b的第二密度。但在另一实施例中,第一屏蔽层107a的第一密度可以小于第二屏蔽层107b的第二密度。

30.具体而言,第一屏蔽层107a与第二屏蔽层107b可利用层压(lamination)技术来形成片状的屏蔽结构107,层压技术可提升屏蔽结构107的强度与稳定性。第一屏蔽层1071的第一密度与第二屏蔽层1072的第二密度差异愈大,半导体模块10的表现愈好,例如,第一屏蔽层107a的第一密度趋近于0,第二屏蔽层107b的第二密度则趋近于金属钨的密度(19.35

克/每立方厘米(g/cm3)),或反之亦然。

31.例如,第一屏蔽层107a可包括高介电常数材料(high dielectric constant material,简称high-k material),第二屏蔽层107b可包括低介电常数材料(low-k material),或反之亦然。高介电常数材料与低介电常数材料可分别选用本发明所述技术领域中现有的材料。低介电常数材料可以例如是氮化硅、二氧化硅、氟化硅玻璃材料(fluorinated silicate glass,简称fsg)、极低介电常数材料(ultra-low-k material,简称ulk)、氮掺杂碳化物(nitrogen doped carbide,简称ndc)。高介电常数材料可以例如是氧化鋡(hfo2)、氧化铝(alo

x

)、氧化锆(zro2)、氧化铑(la2o3)或其他合适的材料。

32.值得注意的是,屏蔽结构107不仅仅为二层结构。在一实施例中,屏蔽结构107可以包括第三屏蔽层(未绘示),在第三方向d3上堆叠于第二屏蔽层107b上方。其中,构成第三屏蔽层的材料可以与构成第一屏蔽层107a或/和第二屏蔽层107b的材料相同或不同。其中,第三屏蔽层的第三密度,与相邻接的第二屏蔽层107b的第二密度不同;但第三屏蔽层的第三密度可以与第一屏蔽层107a的第一密度相同或不同。

33.在一实施例中,半导体模块10还可包括第一缓冲层106,设置于金属层105与屏蔽结构107之间。也可理解为第一缓冲层106形成于屏蔽结构107与半导体元件103之间。在一实施例中,第一缓冲层106可包括氧化物(oxide)、氮氧化物或碳氮化物等,但不限于此。例如,第一缓冲层106可包括氮氧化硅(silicon oxynitride;sion)或碳氮化硅(silicon carbonitride;sicn)。在一实施例中,第一缓冲层106可提升半导体模块10的散热效能。在一实施例中,第一缓冲层106可改善不同层元件之间的界面相容性,例如是改善金属层105与屏蔽结构107之间的界面相容性,以使金属层105与屏蔽结构107稳定连接。

34.压电层109可形成于屏蔽结构107上。更具体地,在第三方向d3上,压电层109可形成于屏蔽结构107上,压电层109和半导体元件103可分别设置于屏蔽结构107的相对侧。压电层109可由压电材料制成。压电材料可包括压电单晶体、压电多晶体、压电聚合物或压电复合材料。更具体地,压电材料可包括氮化铝(aln)、石英(quartz)、钽酸锂(litao3)、铌酸锂(linbo3)、陶瓷(ceramics)、锆钛酸铅(pzt)、pvdf(polyvinylidene fluoride)及其共聚物(copolymer)、聚氯乙烯(polyvinyl chloride,简称pvc)、或陶瓷和聚合物组成的复合材料等任意合适的压电材料。

35.在本实施例中,压电层109直接形成于屏蔽结构107上,而不需要采用额外的接合(bonding)工序来完成压电层109与屏蔽结构107之间的连接,也就是说,在不需要额外的焊接步骤或额外设置用于连接的凸块或贯穿孔的情况下,压电层109可整合入半导体模块10中。因此,半导体模块10的可靠度不会因对准精确性不佳或焊线品质不稳定而降低,且可提升压电层109的控制性。也就是说,现有技术中采用接合工序来连接元件,却难以被良好地控制的问题、以及现有技术中半导体模块10的一致性、整合度与效能不足的问题,可透过上述本发明提供的技术方案获得一并改善。

36.如图1所示,半导体模块10还可包括导电结构110嵌入压电层109中。导电结构110可沿第三方向d3贯穿导电结构110的上表面与下表面。在本实施例中,导电结构110包括多个在第三方向d3上延伸的叉指状电极210/211,且多个叉指状电极210/211沿着第二方向d2间隔设置于压电层109中。

37.例如请参照图2a,图2a是绘示图1中导电结构110的俯视图。在本实施例中,导电结

构110包括至少一对叉指状电极210/211设置于压电层109中。其中,叉指状电极210包括多个彼此相连的导电指部110f1,叉指状电极211包括多个彼此相连的导电指部110f2,二者在第一方向d1与第二方向d2交错形成的平面上分散地设置,并且使叉指状电极210的多个导电指部110f1与叉指状电极211的导电指部110f2彼此间隔设置。其中,导电结构110中的叉指状电极210/211的配置可以形成一种金属-绝缘体-金属电容(metal oxide metal capacitor,mom cap)元件。

38.在一实施例中,导电结构110中的一对叉指状电极210/211可建构成一种叉指式换能器(interdigital transducer,简称idt)。也可说是导电结构110包括叉指式换能器。在此情况下,导电结构110与压电层109可作为滤波器,例如是声表面波滤波器。在导电结构110与压电层109作为滤波器的情况下,导电结构110中的一对叉指状电极210/211可分别是信号输入端电极与信号输出端电极。

39.在另外一实施例中,叉指式换能器可包含多种配置样式,以形成多种类型的滤波器,例如是横向滤波器(transverse filter)、复线耦合滤波器(multistrip coupler filter)、多指滤波器(interdigitated interdigital transducer)与双模滤波器(double-mode filter)等。除此之外,半导体模块10还可包含共振电路,以降低滤波器的插入耗损(insertion loss)。

40.但值得注意的是,导电结构110的配置方式并不以此为限。虽然在本实施例中,叉指状电极210/211沿着第三方向d3延伸贯穿压电层109。但在另一实施例中,导电结构110仅设置于压电层109的上表面。又虽然图2a中仅绘示一对叉指状电极210/211,且所绘示的叉指状电极210仅包括3个导电指部110f1,叉指状电极211仅包括4个导电指部110f2。但导电结构110可以包括复数对叉指状电极210/211(例如图2b中导电结构110具有3对叉指状电极210/211)。且每一对叉指状电极210/211中的导电指部110f1和110f2的数量不以此为限。在其他实施例中,叉指状电极210/211中导电指部110f1和110f2的数量可以依照半导体模块10的设计需求而有所增减。在一实施例中,半导体模块10还可包括第二缓冲层108,设置于屏蔽结构107上。如图1所示,在第三方向d3上,第一缓冲层106与第二缓冲层108分别设置于屏蔽结构107的相对侧。换言之,第二缓冲层108形成于屏蔽结构107与压电层109之间。在一实施例中,第二缓冲层108可包括氧化物、氮氧化物或碳氮化物等,但不限于此。例如,第二缓冲层108可包括氮氧化硅(silicon oxynitride;sion)或碳氮化硅(silicon carbonitride;sicn)。在一实施例中,第二缓冲层108和第一缓冲层106可以包括相同的材料或由相同的材料制成。

41.在一实施例中,第二缓冲层108可吸收半导体模块10中的电磁波。在一实施例中,第二缓冲层108可改善不同层元件之间的界面相容性,例如是改善屏蔽结构107与压电层109之间的界面相容性,以使屏蔽结构107与压电层109稳定连接。

42.半导体模块10还可包括第一保护层111,设置于压电层109上。在一实施例中,第一保护层111设置于压电层109的上表面,第二缓冲层108设置于压电层109的下表面,导电结构110沿着第三方向d3贯穿第一保护层111、压电层109及第二缓冲层108,且导电结构110在第三方向d3上的下端点设置于第二缓冲层108中。

43.半导体模块10还可包括第二保护层112,设置于第一保护层111上。在一实施例中,第二保护层112设置于第一保护层111的上表面,且设置于第一保护层111、压电层109与第

二缓冲层108的侧表面。在一实施例中,第二保护层112设置于屏蔽结构107的部分上表面与部分侧表面。

44.在一实施例中,第一保护层111与第二保护层112可包括相同的材料或不同的材料。在一实施例中,第一保护层111与第二保护层112可包括介电材料。在一实施例中,第一保护层111与第二保护层112可包括和现有技术的互补式金属氧化物半导体(complementary metal-oxide-semiconductor,简称cmos)制作工艺相容的材料,例如是氮化物、氧化物或陶瓷类材料等。在一实施例中,第一保护层111与第二保护层112可包括氮化硅(sin)。

45.在一实施例中,第一保护层111与第二保护层112可使半导体模块10的刚度(stiffness)提升。

46.半导体模块10还可包括氧化物结构113,设置于第二保护层112上。

47.半导体模块10还可包括接触结构(contact)114。在一实施例中,接触结构114设置于金属层105的上表面,以提供金属层105和其他电路或装置(未绘示)之间的电连接。

48.在一实施例中,在导电结构110与压电层109作为声表面波滤波器的情况下,屏蔽结构107可增强信号;第一保护层111与第二保护层112可提升声表面波滤波器的表现;金属层105可用于散热且避免声表面波滤波器产生的热传递至金属层105与承载件101之间,例如是传递至半导体元件103。第一保护层111可提升声表面波滤波器的刚度,且可提升声表面波滤波器的效能,例如是声表面波滤波器在高频时的效能。第二保护层112可使两个声表面波滤波器彼此电性隔离,或者,第二保护层112可使两个声表面波滤波器和接触结构114电性隔离。在一实施例中,半导体模块10还可包括温度检测电路(未绘示)及/或温度补偿电路(未绘示),以避免声表面波滤波器的稳定性受温度影响而降低。

49.图3是本发明另一实施例的半导体模块30的示意图。其中,半导体模块30的结构与半导体模块10的结构大致类似。差别在于图3所示出的半导体元件303可包括氮化镓(gan)装置与射频绝缘体上覆硅(rf-silicon-on-insulator;rf-soi)装置,且半导体模块30所采用的屏蔽结构307也与半导体模块10所采用的屏蔽结构107不同。

50.在本实施例中,半导体模块30包括基板300、屏蔽结构307及压电层309。基板300包括承载件301、第一线路层302与多个半导体元件303。屏蔽结构307形成于半导体元件303上。压电层309形成于屏蔽结构307上。

51.详言之,第一线路层302形成于承载件301的上表面301u上,包括层间介电材料302a和金属内连线302b。半导体元件303包括两个射频绝缘体上覆硅元件303a与一个氮化镓元件303b。射频绝缘体上覆硅元件303a设置于第一线路层302上方;氮化镓元件303b设置于射频绝缘体上覆硅元件303a上方;且射频绝缘体上覆硅元件303a和氮化镓元件303b之间还包括一个介电缓冲层315。

52.半导体模块30还可包括第二线路层304和金属层305,设置于屏蔽结构307和半导体元件303之间。金属层305可以是一种金属焊垫,具有纳米级别的厚度。在一实施例中,金属层305的厚度可介于0.5微米(μm)至1毫米(mm)之间。第二线路层304可设置于金属层305与半导体元件303之间,以提供金属层305与半导体元件303之间的电连接。在一实施例中,第二线路层304的结构与第一线路层302类似,可包括层间介电材料304a和金属内连线304b。在另一实施例中,第二线路层304可包括重新布线层。

53.本发明不限制用于屏蔽结构307的材料种类。在一实施例中,形成屏蔽结构307的材料可包括介电材料或磁性材料。例如,磁性材料可包括铁氧体、金属软磁材料、氮化硅、低介电常数材料、铪氧化物、二氧化硅、氮化铝、氧化铝、氧化锌、锆钛酸铅、钽酸锂、铌酸锂或四氧化三铁等。

54.在本实施例中,屏蔽结构307可以是一种具有梯度密度(gradient density)的单一层状结构。更具体地,屏蔽结构307具有沿着承载件301、第一线路层302、半导体元件303、屏蔽结构307和压电层309之堆叠方向逐渐变大或变小的密度。在一实施例中,屏蔽结构307的密度,沿着上述的堆叠方向,随着远离压电层309的距离增加而降低;在另一实施例中,屏蔽结构307的密度,沿着上述的堆叠方向,随着远离压电层309的距离减少而降低。

55.在一实施例中,半导体模块30还可包括第一缓冲层306,设置于金属层305与屏蔽结构307之间。也可理解为第一缓冲层306形成于屏蔽结构307与半导体元件303之间。第一缓冲层306可包括氧化物、氮氧化物或碳氮化物等(但不限于此),可提升半导体模块30的散热效能,改善金属层305与屏蔽结构307之间的界面相容性,以使金属层305与屏蔽结构307稳定连接。

56.压电层309可形成于屏蔽结构307上,使压电层309和半导体元件303可分别设置于屏蔽结构307的相对侧。压电层309可由压电材料制成。在本实施例中,压电层309直接形成于屏蔽结构307上,而不需要采用额外的接合工序来完成压电层309与屏蔽结构307之间的连接。因此,半导体模块30的可靠度不会因对准精确性不佳或焊线品质不稳定而降低,且可提升压电层309的控制性。

57.半导体模块30还可包括导电结构310嵌入压电层309中。在本实施例中,导电结构310的结构与图1和图2a~图2b所绘示的导电结构110相同,都包括至少一对叉指状电极210/211设置于压电层109中。导电结构310中的叉指状电极210/211可建构成一种叉指式换能器。

58.半导体模块30还可包括第二缓冲层308、第一保护层311、第二保护层312和氧化物结构313。第二缓冲层308设置于屏蔽结构307与压电层309之间,使第一缓冲层306与第二缓冲层308分别设置于屏蔽结构307的相对侧。第一保护层311设置于压电层309上。第二保护层312,设置于第一保护层311上,且包覆于屏蔽结构307、第一保护层311、压电层309与第二缓冲层308的侧表面。氧化物结构313设置于第二保护层312上。

59.第二缓冲层308可包括氧化物、氮氧化物或碳氮化物等(但不限于此),可吸收半导体模块30中的电磁波,并改善屏蔽结构307与压电层309之间的界面相容性,以使屏蔽结构307与压电层309稳定连接。第一保护层311与第二保护层312可使半导体模块30的刚度提升。

60.半导体模块30还可包括接触结构314,设置于金属层305的上表面,以提供金属层305和其他电路或装置(未绘示)之间的电连接。

61.图4a~图4e是本发明一实施例的半导体模块10的制造方法示意图。图4a~图4e分别示出的半导体模块10各个制造工序中的示例性结构的剖面图。方法包括以下步骤:

62.请参照图4a。提供基板100,基板100包括承载件101、第一线路层102与至少一半导体元件103,半导体元件103形成于承载件101的上表面101u上,第一线路层102形成于半导体元件103与承载件101的上表面101u之间,以提供半导体元件103与承载件101之间的电连

接。第一线路层102可包括层间介电材料102a和金属内连线102b。在一实施例中,提供基板100的步骤包含依据布线图形使层间介电材料102a和金属内连线102b沉积于承载件101的上表面,以形成第一线路层102。

63.接着,在半导体元件103的上表面上形成第二线路层104。在一实施例中,第二线路层104的结构与第一线路层102类似,可包括层间介电材料104a和金属内连线104b。在一实施例中,可依据布线图形使层间介电材料104a和金属内连线104b沉积于承载件101的上表面,以形成第二线路层104。接着,在第二线路层104上形成金属层105,使第二线路层104设置于金属层105与半导体元件103之间。在一实施例中,金属层105可沉积于第二线路层104上。

64.在金属层105的上表面上形成第一缓冲层106,接着,在第一缓冲层106的上表面上形成屏蔽结构107。在一实施例中,第一缓冲层106可沉积于金属层105的上表面上,屏蔽结构107可沉积于第一缓冲层106的上表面上。

65.在一实施例中,形成屏蔽结构107的步骤可包括形成第一屏蔽层107a与第二屏蔽层107b。更具体地,形成屏蔽结构107的步骤可包括:形成第一屏蔽层107a,第一屏蔽层107a具有第一密度且堆叠于半导体元件103;形成第二屏蔽层107b,第二屏蔽层107b具有第二密度且堆叠于第一屏蔽层107a上。在一实施例中,第一屏蔽层107a与第二屏蔽层107b可依序形成于第一缓冲层106上,例如是采用沉积技术来形成。在另一实施例中,可在另外的制造工序中形成包括第一屏蔽层107a与第二屏蔽层107b的屏蔽结构107,接着再以接合技术将包括第一屏蔽层107a与第二屏蔽层107b的屏蔽结构107连接至第一缓冲层106。

66.请参照图4b。在屏蔽结构107形成后,在屏蔽结构107的上表面上形成第二缓冲层108,在第二缓冲层108的上表面上形成压电层109,然后在压电层109的上表面上形成第一保护层111。在一实施例中,第二缓冲层108、压电层109及第一保护层111可采用沉积技术或接合技术来形成。

67.请参照图4c。接着,形成导电结构110贯穿压电层109。在一实施例中,可先移除部分的第二缓冲层108、压电层109及第一保护层111,以形成第一开口501,第一开口501使第二缓冲层108暴露;在第一开口501中沉积导电材料,以形成导电结构110。在一实施例中,移除可通过蚀刻(etch)技术来进行。

68.请参照图4d,移除部分的屏蔽结构107、第二缓冲层108、压电层109及第一保护层111,以形成第二开口502。第二开口502使第二缓冲层108、压电层109及第一保护层111的侧壁暴露,且第二开口502使屏蔽结构107暴露。在一实施例中,第二开口502使屏蔽结构107的部分侧壁暴露。在一实施例中,移除可通过蚀刻技术来进行。

69.请参照图4e,在图4d的处理阶段后,可在第二开口502的侧表面、第二开口502的底表面及第一保护层111的上表面上形成第二保护层112,且第二保护层112覆盖导电结构110。接着,移除第二开口502的底表面的第二保护层112、屏蔽结构107与第一缓冲层106,以使金属层105暴露。在一实施例中,移除可通过蚀刻技术来进行。

70.在图4e的处理阶段后,可形成氧化物结构113与接触结构114,以形成如图1所示的半导体模块10。

71.根据上述实施例,在本发明所提供的半导体模块中,是先在前端模块上形成屏蔽结构,并且采用例如是沉积或接合技术直接在屏蔽结构上形成压电层,直接再进行后段工

序以形成一或多个声表面波滤波器。相较于现有的技术方案,事先以制造工序形成滤波器,再采用额外的接合工序将已制作完成的滤波器安装至半导体模块的前端模块上,本发明可避免由于额外的接合工序而产生的对准精确性问题与焊线品质不稳定的问题。另外,由于不需要额外的接合工序,本发明提供的半导体模块中的声表面波滤波器可被良好地控制,且同时可改善半导体模块的整合度与效能,并降低制造成本。

72.综上所述,虽然结合以上实施例公开了本发明,然而其并非用以限定本发明。本发明所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,可作各种的更动与润饰。因此,本发明的保护范围应当以附上的权利要求所界定的为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。