1.本发明涉及存储器领域,尤其涉及三维集成芯片及其构建方法、数据处理方法以及电子设备。

背景技术:

2.神经网络系统的计算需要高带宽和高能效的存储系统。现有技术中采用高带宽存储器(high bandwidth memory,hbm)单元作为神经网络计算单元的内存,如图1中所示。当神经网络计算单元工作时,数据访问高带宽存储器hbm单元进行操作获取数据。高带宽存储器hbm单元相对于动态随机存取存储器dram可提供较高的内存带宽,但是也具有较高的成本。另外,神经网络系统采用分立内存的方式会具有较高的延迟和功耗。

3.因此,亟需解决现有技术中的上述技术问题。

技术实现要素:

4.本发明旨在通过三维集成技术来实现神经网络系统,为神经网络系统的众多神经网络计算核提供大容量、高带宽、低延迟、低功耗的存储器,有效提升了神经网络系统的性能且降低了神经网络系统的成本。

5.根据本发明的第一方面,提供了一种三维集成芯片,所述三维集成芯片至少包括存储器单元以及神经网络单元,

6.所述存储器单元包括至少两个存储阵列,所述至少两个存储阵列各自具有对应的第一三维集成端口;

7.所述神经网络单元包括至少两个神经网络子单元,所述至少两个神经网络子单元各自至少包括第二三维集成端口、至少一个路由单元和至少一个神经网络计算核,其中:

8.所述第二三维集成端口与对应的所述第一三维集成端口连接,进而将所述存储器单元与所述神经网络单元三维基质集成连接;

9.所述至少一个路由单元被配置为将所述至少两个神经网络子单元连接,其中,源神经网络子单元中的路由单元被配置为基于从所述源神经网络子单元中的神经网络计算核所接收的访问指令中的目标访问地址,至少通过所述源神经网络子单元中的路由单元以及目标神经网络子单元中的路由单元的连接,实现所述源神经网络子单元中的神经网络计算核对相应目标访问地址的访问;

10.所述至少一个神经网络计算核被配置为对所述至少两个存储阵列或所述目标访问地址进行访问,并且利用访问的数据实现对应的神经网络计算功能。

11.根据本发明的三维集成芯片的一个优选实施方案,所述目标访问地址为目标神经网络子单元中的神经网络计算核的地址,其中

12.所述源神经网络子单元中的路由单元被配置为基于从所述源神经网络子单元中的神经网络计算核所接收的访问指令中的所述目标神经网络子单元中的神经网络计算核的地址,至少通过所述源神经网络子单元中的路由单元以及目标神经网络子单元中的路由

单元的连接,实现所述源神经网络子单元中的神经网络计算核对所述目标神经网络子单元中的神经网络计算核的访问。

13.根据本发明的三维集成芯片的一个优选实施方案,所述目标访问地址为目标存储阵列的地址,其中,

14.所述源神经网络子单元中的路由单元被配置为基于从所述源神经网络子单元中的神经网络计算核所接收的访问指令中的所述目标存储阵列的地址,至少通过所述源神经网络子单元中的路由单元、所述目标存储阵列所对应的神经网络子单元中的路由单元、所述目标存储阵列所对应的神经网络子单元中的第二三维集成端口与所述目标存储阵列的第一三维集成端口的连接,实现所述源神经网络子单元中的神经网络计算核对所述目标存储阵列的访问。

15.根据本发明的三维集成芯片的一个优选实施方案,所述至少两个神经网络子单元各自进一步包括内存控制器,所述内存控制器与所述至少一个神经网络计算核连接且与所述第二三维集成端口连接,所述内存控制器基于从所述至少一个神经网络计算核所接收的访问指令中的目标存储阵列的地址,在未通过所述至少一个路由单元的情况下,通过所述第二三维集成端口和所述第一三维集成端口的连接而控制所述至少一个神经网络计算核对所述目标存储阵列进行存储访问。

16.根据本发明的三维集成芯片的一个优选实施方案,所述至少两个神经网络子单元各自进一步包括多路选择开关,所述多路选择开关与所述至少一个路由单元以及所述内存控制器连接,所述多路选择开关被配置为选择性地将所述神经网络计算核与所述至少一个路由单元连接,以实现对所述目标访问地址进行访问,或者将所述神经网络计算核与所述内存控制器连接,以实现对所述目标存储阵列的访问。

17.根据本发明的三维集成芯片的一个优选实施方案,所述神经网络子单元还包括:

18.缓存模块,所述缓存模块被配置用于在所述神经网络单元对所述存储器单元进行存储访问时,将所述神经网络单元的工作电压转换成所述存储器单元的工作电压或者将所述存储器单元的工作电压转换成所述神经网络单元的工作电压。

19.根据本发明的三维集成芯片的一个优选实施方案,所述至少两个神经网络子单元通过所述至少一个路由单元被连接成总线型、星型、环型、树型、网状和混合型拓扑结构。

20.根据本发明的三维集成芯片的一个优选实施方案,所述存储阵列为动态随机存取存储器阵列。

21.根据本发明的第二方面,提供了一种三维集成芯片的构建方法,所述三维集成芯片至少包括存储器单元以及神经网络单元,所述构建方法包括:

22.构建所述存储器单元,所述存储器单元包括至少两个存储阵列和至少两个第一三维集成端口,其中:

23.所述存储阵列包括至少一个存储体;

24.每个存储体对应一个第一三维集成端口;

25.构建所述神经网络单元,所述神经网络单元包括至少两个神经网络子单元,所述神经网络子单元至少包括第二三维集成端口、至少一个神经网络计算核和至少一个路由器,其中:

26.所述第二三维集成端口与所述至少一个第一三维集成端口连接;

27.所述神经网络计算核被配置为对所述至少一个存储体进行访问,并且利用访问的数据实现对应的神经网络计算功能;

28.所述路由单元被配置为将所述至少两个神经网络子单元连接,其中,源神经网络子单元中的路由单元被配置为基于从所述源神经网络子单元中的神经网络计算核所接收的访问指令中的目标访问地址,至少通过所述源神经网络子单元中的路由单元以及目标神经网络子单元中的路由单元的连接,实现所述源神经网络子单元中的神经网络计算核对相应目标访问地址的访问。

29.根据本发明的第三方面,提供一种三维集成芯片的数据处理方法,所述数据处理方法基于第一三维集成芯片,所述方法包括:源神经网络子单元中的神经网络计算核接收访问指令;基于所述访问指令,通过所述源神经网络子单元中的路由单元以及目标神经网络子单元中的路由单元实现所述源神经网络子单元中的神经网络计算核对相应目标访问地址的访问;利用访问的数据实现对应的神经网络计算功能。

30.根据本发明的第四方面,提供了一种电子设备,所述电子设备包括根据本发明的第一方面所述的三维集成芯片。

附图说明

31.通过下文结合对附图的说明,将更容易理解本发明,在附图中:

32.图1示意性示出了现有技术中的基于高带宽存储器单元的神经网络系统的结构图。

33.图2示意性示出了根据本发明的三维集成芯片的一个实施例。

34.图3示意性示出了在根据本发明的三维集成芯片中,神经网络子单元访问其所属的存储阵列的一个实施例。

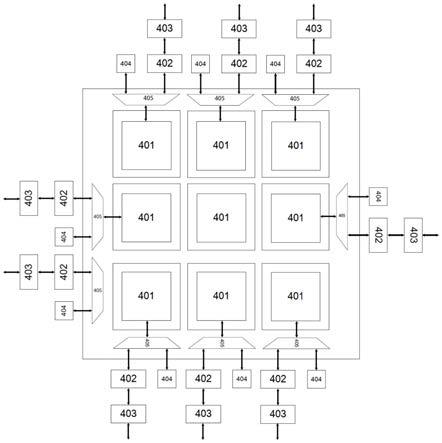

35.图4示意性示出了根据本发明的三维集成芯片的内部连接的一个实施例。

具体实施方式

36.下面将结合附图来对本发明的实施方案进行进一步详述。

37.图2示意性示出了根据本发明的三维集成神经网络芯片的一个实施例。

38.图2所示的三维集成神经网络芯片包括一个神经网络晶圆200(相当于神经网络单元)和一个存储器晶圆210(相当于存储器单元)。神经网络晶圆200是用于实现神经网络逻辑功能的晶圆,存储器晶圆210是用于实现存储器功能的晶圆。神经逻辑晶圆200能够实现模仿动物神经网络行为特征、进行分布式并行信息处理的逻辑功能。神经逻辑晶圆200具有很高的运算速度、很强的联想能力、很强的适应性、很强的容错能力和自组织能力,能够应用于信息领域(诸如,进行信息处理、模式识别等)、医学领域(诸如,进行生物信号的检测与分析等)、经济领域(诸如,进行市场价格预测、风险评估等)、控制领域、交通领域、心理学领域等中。

39.如图2中所示,神经网络晶圆200、存储器晶圆210在竖向方向上堆叠集成。此处的“竖向方向”指的是神经网络晶圆200、存储器晶圆210的厚度方向。

40.另外,存储器晶圆210和神经网络晶圆200之间通过三维异质集成的方式键合连接,以实现神经网络晶圆200与存储器晶圆210的三维异质集成。具体而言,存储器晶圆210

通过混合键合技术(图2中示意性示出为)直接连接至神经网络晶圆200。

41.从图2中还可看到,神经网络晶圆200通过凸点(bump)工艺被连接至基板220。凸点工艺包括但不限于现有技术中已知的bopcoa、boac、hotrod。

42.另外,在图2中结合神经网络晶圆和存储器晶圆进行了描述。已知的是,晶圆是制造半导体器件的基础性原材料,极高纯度的半导体经过拉晶、切片等工艺被制备成为晶圆。晶圆经过一系列半导体制造工艺形成极微小的电路结构,再经切割、封装、测试成为芯片。本发明不限于神经网络晶圆和存储器晶圆,实际上神经网络晶圆200也可以是神经网络芯片,存储器晶圆210也可以是存储器芯片。优选地,存储器晶圆210可以为动态随机存取存储器晶圆或者动态随机存取存储器芯片。

43.图2中示出的是一个存储器晶圆210或一层存储器晶圆210。应理解,为了满足带宽和存储容量需求,存储器晶圆210可以是更多层,包括但不限于2层、4层、6层等。另外,在多层存储器晶圆的同一层中还可以设置多个存储器晶圆。例如,同一层存储器晶圆层中设置两个存储器晶圆,两个存储器晶圆之间相互独立。

44.此外,多层存储器晶圆可以分别设置于神经网络晶圆的两侧,例如,一个存储器晶圆可以设置于神经网络晶圆的上方,另一存储器晶圆可以设置于神经网络晶圆的下方。由此,缩短了神经网络晶圆至存储器晶圆之间的存储访问路径,提高了存储访问效率。

45.具体而言,神经网络晶圆两侧的存储器晶圆可以通过混合键合技术直接连接至神经网络晶圆;而神经网络晶圆首先通过混合键合技术连接至下方的存储器晶圆,然后贯穿下方的存储器晶圆的硅通孔tsv且之后通过凸点工艺连接至基板。

46.在本发明中,描述的是神经网络晶圆,所获得的对应三维集成芯片为三维集成神经网络芯片。神经网络系统的性能受到存储器带宽、容量、延迟和功耗等的限制。在本发明中,通过为神经网络系统的众多神经网络计算核提供大容量、高带宽、低延迟、低功耗的存储器,有效提升了神经网络系统的性能且降低了神经网络系统的成本。

47.图3示意性示出了在根据本发明的三维集成神经网络芯片中,神经网络子单元访问其所属的存储阵列的一个实施例。

48.本发明的三维集成神经网络芯片包括若干个神经网络子单元(诸如图4中示出的九个神经网络子单元),每个神经网络子单元能够访问其所属的存储阵列,图3中示出了这样的一个实施例。

49.在图3中,神经网络子单元30与所属的存储阵列31之间堆叠集成,且优选地通过键合方式堆叠集成,或者更优选地通过混合键合方式堆叠集成。

50.如图3中所示,神经网络子单元30至少包括神经网络计算核301、内存控制器302以及缓存模块303。

51.缓存模块303中的输入输出三维异质集成端口(即,混合键合的端口,通过图中的两行

“●”

示意性示出)与存储阵列304中的输入输出三维异质集成端口(即,混合键合的端口,通过图中的两行

“●”

示意性示出)连接,从而将神经网络子单元30与存储阵列304三维异质集成。应理解,图3仅为示意性的,输入输出三维异质集成端口也可以位于其他模块中。

52.缓存模块330被配置用于进行电压转换,用于在神经网络子单元30对存储阵列304进行存储访问时,将神经网络子单元30的工作电压转换成存储阵列304的工作电压,或者将存储阵列304的工作电压转换成神经网络子单元30的工作电压。

53.神经网络计算核301能够直接访问其所属的存储阵列304(即,通过其三维异质集成端口所连接的存储阵列304)。

54.例如,当神经网络计算核301接收到访问指令,并且访问指令所携带的访问地址为其三维异质集成端口所连接的存储阵列304时,内存控制器320基于访问地址,通过缓存模块303中的输入输出三维异质集成端口与存储阵列304中的输入输出三维异质集成端口之间的连接,对存储阵列304进行访问。

55.具体地,访问指令例如包括读取指令以及写入指令。当访问指令为读取指令时,内存控制器320基于读取指令通过缓存模块303中的输入输出三维异质集成端口与存储阵列304中的输入输出三维异质集成端口之间的连接,从存储阵列304读取数据。当访问指令为写入指令时,访问指令同时还包括需要写入的数据,内存控制器320基于写入指令通过缓存模块303中的输入输出三维异质集成端口与存储阵列304中的输入输出三维异质集成端口之间的连接将需要写入的数据写入左上角的存储阵列304中。

56.图4示意性示出了根据本发明的三维集成神经网络芯片(即,片上系统)的内部连接的一个实施例。

57.在图4中,示意性示出了九个神经网络子单元40。图4中的九个神经网络子单元40各自进一步包括路由单元404。多个神经网络子单元40通过位于神经网络子单元40中的路由单元404互连形成片上系统。

58.另外,图4中这九个神经网络子单元40各自进一步多路选择开关405。在各个神经网络子单元40中,多路选择开关405与路由单元404以及内存控制器402连接。

59.当多路选择开关405与内存控制器402连接时,神经网络子单元40中的神经网络计算核401能够直接访问其所属的存储阵列(即,通过其三维异质集成端口所连接的存储阵列),步骤可以参见如上面关于图3所描述的。

60.当多路选择开关405与路由单元404连接时,一个神经网络子单元中的神经网络计算核可以通过一个或多个路由单元访问另一神经网络子单元中的神经网络计算核或者存储阵列。

61.具体而言,例如,当图4所示右上角的神经网络子单元(以下称为“源神经网络子单元”)中的神经网络计算核接收到访问指令,并且访问指令所携带的访问地址为图4所示右下角的神经网络子单元(以下称为“目标神经网络子单元”)所属的存储阵列(即,图4所示右下角的神经网络子单元通过其三维异质集成端口所连接的存储阵列)时,源神经网络子单元中的内存控制器基于访问地址,通过源神经网络子单元中的路由单元(以下称为“源路由单元”)、图4中最右侧行的中间神经网络子单元(以下称为“中间神经网络子单元”)中的路由单元(以下称为“中间路由单元”)、目标神经网络子单元中的路由单元(以下称为“目标路由单元”)所形成的访问路径,对目标神经网络子单元所属的存储阵列进行访问。

62.又例如,当图4所示的源神经网络子单元中的神经网络计算核接收到访问指令,并且访问指令所携带的访问地址为图4所示的目标神经网络子单元中的神经网络计算核时,源神经网络子单元中的内存控制器基于访问地址,通过源神经网络子单元中的源路由单元、中间神经网络子单元中的中间路由单元、目标神经网络子单元中的目标路由单元所形成的访问路径,对目标神经网络子单元中的神经网络计算核进行访问。

63.图4中仅示意性示出了网状拓扑结构的存储器网络。本发明的存储器网络包括但

不限于总线型、星型、环型、树型、网状和混合型拓扑结构。

64.本发明中所提出的三维集成芯片是存储芯片或存储晶圆(例如,rom、sdram、ram、dram、sram、flash、eprom、eeprom、cd-rom或其他光盘存储装置、磁盘存储装置或其他磁性存储装置),以用于存储数据和/或计算机代码。三维集成芯片可以是或包括非瞬态易失性存储器或非易失性存储器等。

65.本技术还提出一种三维集成芯片的数据处理方法,所述方法包括:

66.步骤s1:源神经网络子单元中的神经网络计算核接收访问指令。

67.步骤s2:基于所述访问指令,通过所述源神经网络子单元中的路由单元以及目标神经网络子单元中的路由单元实现所述源神经网络子单元中的神经网络计算核对相应目标访问地址的访问。

68.步骤s3:利用访问的数据实现对应的神经网络计算功能。

69.具体而言,例如,当图4所示右上角的神经网络子单元(以下称为“源神经网络子单元”)中的神经网络计算核接收到访问指令,并且访问指令所携带的访问地址为图4所示右下角的神经网络子单元(以下称为“目标神经网络子单元”)所属的存储阵列(即,图4所示右下角的神经网络子单元通过其三维异质集成端口所连接的存储阵列)时,源神经网络子单元中的内存控制器基于访问地址,通过源神经网络子单元中的路由单元(以下称为“源路由单元”)、图4中最右侧行的中间神经网络子单元(以下称为“中间神经网络子单元”)中的路由单元(以下称为“中间路由单元”)、目标神经网络子单元中的路由单元(以下称为“目标路由单元”)所形成的访问路径,对目标神经网络子单元所属的存储阵列进行访问。

70.又例如,当图4所示的源神经网络子单元中的神经网络计算核接收到访问指令,并且访问指令所携带的访问地址为图4所示的目标神经网络子单元中的神经网络计算核时,源神经网络子单元中的内存控制器基于访问地址,通过源神经网络子单元中的源路由单元、中间神经网络子单元中的中间路由单元、目标神经网络子单元中的目标路由单元所形成的访问路径,对目标神经网络子单元中的神经网络计算核进行访问。

71.应注意,上文所提及的实施方案例示而非限制本发明,且在不脱离所附权利要求的范围的前提下,本领域技术人员将能够设计许多替代实施方案。应理解,本发明的范围由权利要求限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。