技术特征:

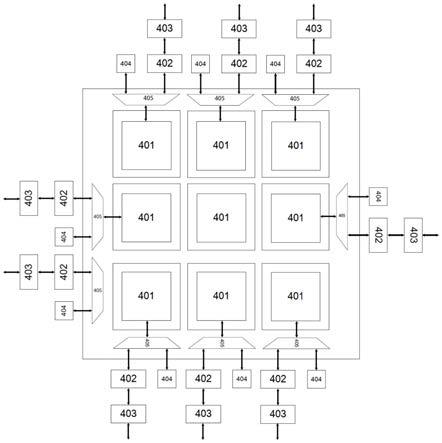

1.一种三维集成芯片,其特征在于,所述三维集成芯片至少包括存储器单元以及神经网络单元,所述存储器单元包括至少两个存储阵列,所述至少两个存储阵列各自具有对应的第一三维集成端口;所述神经网络单元包括至少两个神经网络子单元,所述至少两个神经网络子单元各自至少包括第二三维集成端口、至少一个路由单元和至少一个神经网络计算核,其中:所述第二三维集成端口与对应的所述第一三维集成端口连接,进而将所述存储器单元与所述神经网络单元三维基质集成连接;所述至少一个路由单元被配置为将所述至少两个神经网络子单元连接,其中,源神经网络子单元中的路由单元被配置为基于从所述源神经网络子单元中的神经网络计算核所接收的访问指令中的目标访问地址,至少通过所述源神经网络子单元中的路由单元以及目标神经网络子单元中的路由单元的连接,实现所述源神经网络子单元中的神经网络计算核对相应目标访问地址的访问;所述至少一个神经网络计算核被配置为对所述至少两个存储阵列或所述目标访问地址进行访问,并且利用访问的数据实现对应的神经网络计算功能。2.根据权利要求1所述的三维集成芯片,其特征在于,所述目标访问地址为目标神经网络子单元中的神经网络计算核的地址,其中所述源神经网络子单元中的路由单元被配置为基于从所述源神经网络子单元中的神经网络计算核所接收的访问指令中的所述目标神经网络子单元中的神经网络计算核的地址,至少通过所述源神经网络子单元中的路由单元以及目标神经网络子单元中的路由单元的连接,实现所述源神经网络子单元中的神经网络计算核对所述目标神经网络子单元中的神经网络计算核的访问。3.根据权利要求1或2所述的三维集成芯片,其特征在于,所述目标访问地址为目标存储阵列的地址,其中,所述源神经网络子单元中的路由单元被配置为基于从所述源神经网络子单元中的神经网络计算核所接收的访问指令中的所述目标存储阵列的地址,至少通过所述源神经网络子单元中的路由单元、所述目标存储阵列所对应的神经网络子单元中的路由单元、所述目标存储阵列所对应的神经网络子单元中的第二三维集成端口与所述目标存储阵列的第一三维集成端口的连接,实现所述源神经网络子单元中的神经网络计算核对所述目标存储阵列的访问。4.根据权利要求1或2所述的三维集成芯片,其特征在于,所述至少两个神经网络子单元各自进一步包括内存控制器,所述内存控制器与所述至少一个神经网络计算核连接且与所述第二三维集成端口连接,所述内存控制器基于从所述至少一个神经网络计算核所接收的访问指令中的目标存储阵列的地址,在未通过所述至少一个路由单元的情况下,通过所述第二三维集成端口和所述第一三维集成端口的连接而控制所述至少一个神经网络计算核对所述目标存储阵列进行存储访问。5.根据权利要求4所述的三维集成芯片,其特征在于,所述至少两个神经网络子单元各自进一步包括多路选择开关,所述多路选择开关与所述至少一个路由单元以及所述内存控制器连接,所述多路选择开关被配置为选择性地将所述神经网络计算核与所述至少一个路

由单元连接,以实现对所述目标访问地址进行访问,或者将所述神经网络计算核与所述内存控制器连接,以实现对所述目标存储阵列的访问。6.根据权利要求1或2所述的三维集成芯片,其特征在于,所述神经网络子单元还包括:缓存模块,所述缓存模块被配置用于在所述神经网络单元对所述存储器单元进行存储访问时,将所述神经网络单元的工作电压转换成所述存储器单元的工作电压或者将所述存储器单元的工作电压转换成所述神经网络单元的工作电压。7.根据权利要求1或2所述的三维集成芯片,其特征在于,所述至少两个神经网络子单元通过所述至少一个路由单元被连接成总线型、星型、环型、树型、网状和混合型拓扑结构。8.根据权利要求1或2所述的三维集成芯片,其特征在于,所述存储阵列为动态随机存取存储器阵列。9.一种三维集成芯片的构建方法,其特征在于,所述三维集成芯片至少包括存储器单元以及神经网络单元,所述构建方法包括:构建所述存储器单元,所述存储器单元包括至少两个存储阵列和至少两个第一三维集成端口,其中:所述存储阵列包括至少一个存储体;每个存储体对应一个第一三维集成端口;构建所述神经网络单元,所述神经网络单元包括至少两个神经网络子单元,所述神经网络子单元至少包括第二三维集成端口、至少一个神经网络计算核和至少一个路由器,其中:所述第二三维集成端口与所述至少一个第一三维集成端口连接;所述神经网络计算核被配置为对所述至少一个存储体进行访问,并且利用访问的数据实现对应的神经网络计算功能;所述路由单元被配置为将所述至少两个神经网络子单元连接,其中,源神经网络子单元中的路由单元被配置为基于从所述源神经网络子单元中的神经网络计算核所接收的访问指令中的目标访问地址,至少通过所述源神经网络子单元中的路由单元以及目标神经网络子单元中的路由单元的连接,实现所述源神经网络子单元中的神经网络计算核对相应目标访问地址的访问。10.一种三维集成芯片的数据处理方法,其特征在于,所述数据处理方法基于权利要求1-8中的任一项所述的三维集成芯片,所述方法包括:源神经网络子单元中的神经网络计算核接收访问指令;基于所述访问指令,通过所述源神经网络子单元中的路由单元以及目标神经网络子单元中的路由单元实现所述源神经网络子单元中的神经网络计算核对相应目标访问地址的访问;利用访问的数据实现对应的神经网络计算功能。11.一种电子设备,其特征在于,所述电子设备包括根据权利要求1-8中的任一项所述的三维集成芯片。

技术总结

本发明涉及通过三维集成技术来实现神经网络系统,为神经网络系统的众多神经网络计算核提供大容量、高带宽、低延迟、低功耗的存储器,有效提升了神经网络系统的性能且降低了神经网络系统的成本。经网络系统的成本。经网络系统的成本。

技术研发人员:周小锋

受保护的技术使用者:西安紫光国芯半导体有限公司

技术研发日:2021.10.22

技术公布日:2022/1/25

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。