1.本公开大体涉及高压晶体管,且更具体来说涉及具有场板的高压晶体管。

技术实现要素:

2.在所描述的实例中,一种设备包含形成在半导体衬底上的晶体管,所述晶体管包含:晶体管栅极和在所述晶体管栅极与晶体管漏极触点之间的延伸漏极;晶体管源极触点,其耦合到源极触点探针垫;第一电介质层,其覆盖所述衬底和所述晶体管栅极;源极场板,其位于所述第一电介质层上并耦合到与所述源极触点探针垫隔开并电隔离的源极场板探针垫;且所述源极场板通过所述第一电介质层电容耦合到所述延伸漏极的第一部分。

附图说明

3.图1是高压、高电子迁移率晶体管(hv

‑

hemt)的横截面图,所述晶体管具有栅极场板、源极场板以及用于晶体管源极和源极场板的单独探针垫。

4.图2为具有栅极场板、第一源极场板和第二源极场板的hv

‑

hemt的横截面图,其具有用于晶体管源极、第一源极场板和第二源极场板的单独探针垫。

5.图3a和3b是具有与晶体管栅极隔离的栅极场板的hv

‑

hemt的横截面图。

6.图4为具有栅极场板、第一源极场板和第二源极场板的高压、漏极延伸mos晶体管(hvdemos)的横截面图,其具有用于晶体管源极、第一源极场板和第二源极场板的单独探针垫。

7.图5是具有高压延伸漏极晶体管的裸片的拐角的平面图,所述晶体管具有晶体管源极,并且具有线接合到引线框架上的第一引线的第一和第二源极场板探针垫,并且具有线接合到第二引线的晶体管漏极探针垫。

8.分开来说,图6a是具有高压延伸漏极晶体管的裸片的平面图,且图6b是其横截面图。

9.分开来说,图7a是具有高压延伸漏极晶体管的裸片的平面图,且图7b是其横截面图,所述晶体管的源极和第一和第二源极场板探针垫耦合在一起。

10.分开来说,图8a是具有高压延伸漏极晶体管的裸片的平面图,且图8b是其横截面图,所述晶体管的源极探针垫和第一和第二源极场板探针垫与重布层耦合在一起。

11.图9a、9b、9c和9d是说明具有使用倒装芯片球接合耦合到衬底上的相同引线的晶体管源极探针垫、第一源极场板探针垫和第二源极场板探针垫的布置的横截面图。

12.图10a、10b、10c和10d是说明测试和封装具有电独立源极探针垫和源极场板探针垫的高压延伸漏极晶体管的主要步骤的横截面图。

13.图11是列出测试和封装具有电独立源极探针垫和源极场板探针垫的高压延伸漏极晶体管的步骤的流程图。

具体实施方式

14.不同图中对应的数字和符号一般指对应的部分,除非另有指示。所述图不一定按比例绘制。

15.在此描述中,层被描述为在底层“上”形成。但是,可使用中介层。例如,导体金属可形成在称为“金属间电介质”或“imd”的电介质层上。术语“在

……

上”包含将金属直接沉积在金属间电介质(imd)层上的替代方案,以及将金属沉积在例如抗反射涂层(arc)层、背面抗反射涂层(barc)层、粘附层或扩散势垒层的中介层上的替代方案;这些中介层改进结果,包含改进光刻结果,减少分层,以及减少原子向周围材料的扩散。无论是否存在这样的中介层,在本文中,导体层都被称为在电介质层“上”或“上方”。

16.所述布置中描述的若干层是电介质层。实例包含金属前电介质(pmd)层和金属间电介质(imd)层,有时称为“层间电介质”层(ild)。尽管这些层在实例中被描述为单层,但所述布置也包含多层电介质层。用于所述布置的电介质层的材料包含二氧化硅或简单的“氧化物”、氮化硅或简单的“氮化物”、氧氮化硅、碳化硅和用于半导体装置的其它电介质。各种电介质膜沉积工艺可用于所述布置,包含化学气相沉积(cvd)、等离子体增强化学气相沉积(pecvd)、分子束外延(mbe)等。若干层在本文被描述为“金属层”或“导体层”。这些金属或导体层可为例如铝或铝合金、铜或铜合金,并且可包含额外的板,例如镍、钯、金、银、铂、钨、钛和这些的组合。溅射和镶嵌工艺可与图案化和蚀刻一起使用来形成金属层。可使用电镀和化学镀来形成金属层。可使用化学机械抛光(cmp)来形成金属层。

17.在本描述中,使用术语“通孔”。如本文所使用,通孔是形成在由电介质层隔开的金属层之间的连接。所述通孔包含在所述电介质层中的开口和在所述开口中的导电材料(例如导电插头或电镀材料),其填充开口或在开口中形成导电衬层,以通过电介质层电连接金属层。

18.在本描述中,使用术语“触点”。如本文所使用,触点是导电材料电和物理地接触半导体衬底中的区域的区域。触点(例如)在导体层和源极、主体或漏极区域之间形成电连接。

19.在本描述中,使用术语“高压晶体管”。如本文所使用,术语高压晶体管是指操作以提供大于20伏电压的晶体管。布置对于使用一个源极场板或多于一个源极场板的晶体管是有用的。高压晶体管经常使用源极场板。

20.在本描述中,使用术语“宽带隙半导体衬底”。如本文所使用的,宽带隙半导体衬底是具有2到4电子伏特(ev)范围内的带隙电压的材料的一者。实例材料包含iii到v和ii到vi化合物。氮化镓(gan)、氮化铝镓(algan)、氮化铝(aln)和氮化硼是实例材料。在实例中,gan层用作半导体衬底。gan层可为绝缘体上或另一半导体衬底上的外延层。在另一布置中,可使用ga2o3(三氧化镓)。

21.在实例布置中,展示多个金属层。所用的金属层的数量与工艺有关,且可大于本文所展示的实例,也可小于本文所展示的实例。半导体工艺可包含八层或多于八层金属,不过通常使用更少的金属。

22.在延伸漏极晶体管中,具有低压栅极电介质的晶体管用于切换高压。例如,具有在5伏特或更低的电压下击穿的栅极电介质的晶体管可用来在高压延伸漏极晶体管中切换多达几百伏特。跨漏极触点和低压晶体管栅极之间的延伸漏极区域的压降足以保护低压栅极电介质免受施加到漏极触点的高压的影响。通过在漏极区域上形成导电材料的场板,可减

小此晶体管所需的延伸漏极区域的长度。例如,可使用覆盖的互连层的一者。当高压晶体管关断时,场板耦合到源极触点并保持在接地。接地的源极场板通过电介质层电容耦合到延伸漏极区域,降低延伸漏极的表面电势。

23.在布置中,通过使用提供给装置中的源极场板的探针垫和使用到装置的源极的另一探针垫,来解决测试具有源极和源极场板的装置的问题,以在晶片探针测试中实现装置的过电压应力测试(ovst)。布置能够在晶片探针测试期间和封装裸片之前测试电介质层,节省原本会花费在封装坏裸片上的成本和时间。当封装装置时,源极和源极场板电耦合在一起,以便在正常操作中作为单个端子使用。

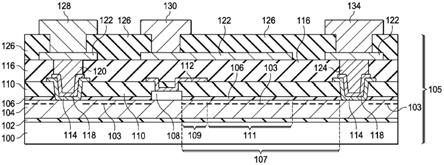

24.图1说明具有栅极场板112和源极场板122的增强模式gan高压(hv)高电子迁移率晶体管(hv

‑

hemt)。源极场板122耦合到与源极探针垫128分离的源极场板探针垫130,以改进可测试性。在图示的实例中使用gan hv

‑

hemt 105。也可使用采用替代高迁移率衬底(例如三氧化镓(ga2o3))的hv

‑

hemt。具有场板的漏极延伸mos晶体管(demos)可与下文进一步描述的布置一起使用。增强模式或耗尽模式晶体管都可与所述布置一起使用。

25.分开控制高压延伸漏极晶体管的源极和源极场板上的电压的能力使得能够在晶片探针测试中测试晶体管中的电介质,使得有缺陷的电介质可被检测到,并且可在晶片探针测试中报废这些装置。在晶片探针测试中识别故障装置的这种能力避免了封装良好的和坏的裸片的费用,并减少或消除了对裸片执行老化测试以接着识别哪些封装的裸片具有缺陷的电介质且应该报废的需要。由于封装步骤的成本很高,所以在晶片探针测试中,报废封装的装置比识别有缺陷的裸片要昂贵得多,也浪费得多。

26.图1中的实例hv

‑

hemt 105的衬底是形成在硅衬底100上的氮化铝绝缘体(aln)102上的氮化镓(gan)104。氮化铝镓(algan)电子产生层106覆盖氮化镓层104的部分,并在gan 104层中产生二维电子气(图1中展示为虚线103)。其它宽带隙半导体衬底可与所述布置一起使用。形成在硅衬底上的漏极延伸装置也可与所述布置一起使用。在源极触点120和漏极触点124之间的沟道上方的栅极108形成增强模式hv

‑

hemt。栅极108和高压漏极触点124之间的延伸漏极区域107的长度足以降低足够的电压以保护晶体管栅极108。金属前电介质(pmd)层110覆盖gan衬底104和栅极108。在pmd层110上或上方的栅极场板112覆盖栅极108,并覆盖邻近于栅极108的延伸漏极区109的第一部分。栅极场板可由第一互连层制成。栅极场板112通过穿过pmd层110的触点耦合到栅极108。第一金属间电介质(imd1)层116覆盖pmd层110和栅极场板112。

27.第一金属间电介质(imd1)层116上的源极场板122部分地覆盖在栅极场板112的端和源极场板122的端之间的延伸漏极区111的第二部分。源极场板122可由第二互连层制成。第二imd层(imd2)覆盖imd1层并覆盖源极场板122。imd2层126上的源极场板探针垫130通过穿过imd2层的通孔连接到源极场板122。imd2层126上的源极探针垫128通过延伸穿过imd2层126、imd1层116和pmd层110的多个通孔连接到源极触点120。imd2层126上的漏极探针垫134通过延伸穿过imd2层126、imd1层116和pmd层110的多个通孔连接到漏极124。在源极120和漏极124触点的底部的例如tin或tiw的触点衬层金属114形成到下层gan衬底104的欧姆连接。

28.在操作中,当相对于源极触点120的电势在栅极108处放置足够的正电势时,在栅极108之下形成导电沟道区域,并且在漏极和源极之间可发生电流传导。当移除栅极电势

时,电子气层从栅极108下方分散,并且漏极和源极之间的传导被阻断。

29.当hv

‑

hemt关断时,源极触点120和源极场板122可接地。通过接地源极场板122与延伸漏极区107之间的pmd层的电容耦合降低延伸漏极区的表面电势。对于给定的装置尺寸(与没有源极场板的装置相比),使用场板实现更高的电压操作,而不会因电流崩溃产生损耗。栅极场板112和第一延伸漏极区109之间的耦合长度以及源极场板122和第二延伸漏极区111之间的耦合长度取决于由hv

‑

hemt 105切换的高压的量值和晶体管栅极108下的栅极电介质的击穿电压。

30.对源极场板122上的电压和源极触点120上的电压的单独控制可在晶片探针测试中检测有缺陷的pmd层110和有缺陷的imd1层116电介质。在晶片探针测试的缺陷检测消除了将有缺陷的单元与良好的单元一起封装并在稍后执行老化测试以识别哪些封装的单元是坏的需要。通过不封装坏模具,通过使用所述布置实现材料、成本和时间的大量节省。

31.在hv

‑

hemt 105的关断状态下,源极触点120、源极场板122、栅极108和栅极场板112可接地。当高压施加到hv

‑

hemt漏极触点124时,最高电场通过接地源极场板122和接地源极场板122下层的第二延伸漏极区域111之间的电介质堆叠(imd1层116/pmd层110)。如果在此电介质堆叠中存在缺陷,那么从源极场板122到漏极触点124的泄漏电流增加,或者电介质堆叠损坏。在晶片探针测试期间可观察到装置操作中的这些变化,从而指示有缺陷的装置。有缺陷的裸片可在晶片探针测试中被识别,并可报废。

32.在所述布置中,为源极场板122提供单独的探针垫130允许提高源极场板122上的电压,同时保持源触点120上的电压接地。在不单独控制源极场板122和源触点120上的电压的情况下,不能在晶片探针测试中识别具有缺陷pmd层110的hv

‑

hemt 105。提高源极场板122上的电压减小了下层的电介质堆叠(imd1层116/pmd层110)中的场,允许栅极场板112下的第一延伸漏极区109上的电势上升。这提高延伸漏极区域与栅极场板112之间的电压,从而对pmd层110层施加应力。在晶片探针测试中,可以这种方式识别在栅极场板112下的pmd层110中具有缺陷的装置,并且可报废所述装置。

33.图2说明另一hv

‑

hemt 205,其中源极场板分段成第一源极场板222和第二源极场板232。第二源极场板232的添加使hv

‑

hemt 205能够切换更高的电压(当与没有第二源极场板的装置相比时),而延伸漏极的长度几乎没有增加。在图2中,为了清楚起见,类似的元件符号用于如图1中展示的类似元件。(例如,图2中的栅极场板212对应于图1中的栅极场板112。)图2中的hv

‑

hemt 205类似于图1中的hv

‑

hemt 105,但是在形成第一源极场板222时(与图1的布置相比)源极场板的长度减小(相比于图1中的122),并且现在在imd2层226上方添加第二源极场板232。第二源极场板232覆盖第一源极场板222的端,并且覆盖延伸漏极区域213的位于第一源极场板222的端与高压漏极触点224之间的第三部分。第二源极场板232通过包含imd2层226/imd1层216/pmd层210的电介质堆叠电容耦合到第三延伸漏极区213。

34.当hv

‑

hemt 205关断时,源极触点220、第一源极场板222和第二源极场板232可保持接地。由于第二源极场板232下的电介质堆叠(imd2层226/imd1层216/pmd层210)比第一源极场板下的电介质堆叠(imd1层216/pmd层210)厚,因此电容耦合较小,导致第二源极场板232下的第三延伸漏极区域213的表面电势高于第一源极场板222下方的第二延伸漏极区域211的表面电势。当向hv

‑

hemt漏极触点224施加高压时,最大电场穿过接地的第二源极场板232与第三延伸漏极区域213之间的电介质堆叠(imd2层226/imd1层216/pmd层210)。如果

在此电介质堆叠中存在增加通过电介质堆叠的泄漏电流或导致电介质堆叠击穿的缺陷,那么可在晶片探针测试中检测到所述缺陷,并可报废有缺陷的芯片。

35.在此布置中,使用分别用于源极220、第一源极场板222和第二源极场板232的包含源极探针垫228、第一源极场板探针垫230和第二源极场板232的单独探针垫,允许单独地控制源极230、第一源极场板222和第二源极场板232上的电压。在没有如使用所述布置所提供的对第一源极场板222和第二源极场板232上的电压的单独控制的情况下,在晶片探针测试中不能确定栅极场板212和下层的第一延伸漏极区209之间的电介质pmd 210是否有缺陷,或第一源极场板222和下层的第二延伸漏极区211之间的电介质堆叠(imd1 216/pmd 210)是否有缺陷。在晶片探针测试期间,在确定第二场板232下方的电介质堆叠(imd2层226/imd1层216/pmd层210)通过参数测试之后,可首先在第二源极场板232上提高电压,允许高压到达并对第一源极场板222下方的电介质堆叠(imd1层216/pmd层210)加应力;并且可其次在第二源极场板232和第一源极场板222两者上提高电压,允许高压到达并对栅极场板212下方的pmd层210加应力。这使在栅极场板212下的pmd层210中具有电介质缺陷和/或在第一源极场板222下的电介质堆叠(imd1层216/pmd层210)中具有电介质缺陷的高压晶体管能够在探针处被检测到和报废。

36.图3a和3b说明替代布置。在图3a和3b中,为了解释清楚,类似的元件符号用于如图2中展示的类似元件。例如,图3中的栅极场板312对应于图2中的栅极场板212。图3a中的hv

‑

hemt 305类似于图2中的hv

‑

hemt 205,但是图3a中的栅极场板312通过pmd层310与栅极308电隔离。这使栅极308下的电介质能够独立于栅极场板312下的pmd层310而受应力。如图3b中展示,栅极场板312耦合到imd2层326上的栅极场板探针垫340,允许独立控制栅极场板312上的电压。展示对应于图2中的源极触点220的源极触点320。展示对应于图2中的漏极触点224的漏极触点324。在图3a中,延伸漏极区域307在栅极308和漏极触点324之间,延伸漏极区域的第一部分309在栅极场板312下方,延伸漏极区域的第二部分311位于第一源极场板322下方,并且延伸漏极区域的第三部分313位于第二源极场板332下方。

37.图3b是沿着图3a中的虚线3b

‑

3b'的穿过栅极电极308的长度的横截面。栅极场板312通过pmd层310与栅极308电隔离。电介质堆叠imd1层316/imd2层326覆盖栅极场板312。穿过imd1层316的通孔321将栅极场板312连接到imd1层316上的互连引线322。穿过imd2层326的通孔323将互连引线322连接到imd2层326上的探针垫340。触点和通孔的单独堆叠将栅极308连接到imd2层326上方的单独探针垫344。用于栅极场板312和栅极308的单独探针垫340和344分别允许独立地控制栅极308和栅极场板312上的电压。这使在晶片探针测试期间栅极308下的栅极电介质和栅极场板312下的pmd电介质310能够独立地受应力。在封装hv

‑

hemt之前或期间,用于栅极场板312的栅极场探针垫340和用于栅极308的栅极探针垫344耦合在一起,如下文进一步描述。

38.图4展示具有第一源极场板422和第二源极场板432的高压(hv)漏极延伸mos晶体管(demos)405。在图4中,为了清楚起见,类似的元件符号用于如图2中展示的类似元件。例如,图4中的第一源极场板422对应于图2中的源极场板222。使用增强模式n型demos(ndemos)晶体管来说明,但是耗尽模式ndemos和增强或耗尽模式p型demos(pdemos)晶体管也可与所述布置一起使用。demos中的延伸漏极区域407经轻度掺杂,使得当高压被施加到漏极时,它将耗尽载流子。跨漏极和栅极之间的延伸漏极耗尽区发生压降。

39.此实例ndemos装置的衬底400是p型掺杂单晶硅。在源极触点420和漏极触点424之间的沟道上方的栅极450形成增强模式ndemos晶体管。包含栅极450和漏极扩散460之间的延伸漏极扩散456的延伸漏极区域407的长度足以在施加到漏极触点424和栅极450之间降低足够的电压,使得能够使用低压晶体管栅极电介质。例如,可将数百伏的电压施加到漏极触点,并且可将延伸漏极扩散456设计成降低足够的电压,以使具有栅极电压为5伏或更小的栅极电介质的晶体管能够被使用。

40.金属前电介质(pmd)层410覆盖衬底400和demos栅极450的一部分。栅极场板442形成在pmd层410上方。栅极场板442可使用第一互连层形成。延伸穿过pmd层410的通孔将栅极场板442耦合到栅极450。栅极场板442覆盖靠近栅极450的延伸漏极扩散456的第一延伸漏极部分409。imd1层416覆盖pmd层410且覆盖栅极场板442。形成在imd1层416上的第一源极场板422覆盖与栅极场板442的端相邻的延伸漏极456的第二延伸漏极部分411。第一源极场板422可使用第二互连层形成。imd2层426覆盖imd1层416且覆盖第一源极场板422。在imd2层426上方的第二源极场板432部分覆盖在第一源极场板422的端和高压漏极触点424之间的延伸漏极456的第三部分延伸漏极区域413。第二源极场板432可使用第三导电互连层形成。imd2层426上的源极探针垫428用通孔堆叠连接到晶体管源极扩散458,所述通孔延伸穿过由imd2层426/imd1层416/pmd层410形成的电介质堆叠。imd2层426上的漏极探针垫434用穿过电介质堆叠imd2层426/imd1层416/pmd层410的通孔堆叠连接到高压漏极扩散460。imd2层426上的第一源极场板探针垫430用延伸穿过imd2层426的通孔连接到第一源极场板422。imd2层426上的第二场板432可经直接探测并用作第二场板探测垫。通过将电压施加到源极探针垫428、第一源极场板430和第二源极场板432的各个探针垫而提供的源极420、第一源极场板422和第二源极场板432上的电压的单独控制允许在晶片探针测试中单独对栅极场板442下的pmd层410、电介质堆叠(imd1层416/pmd层410)和电介质堆叠(imd2层426/imd1层416/pmd层410)施加应力。对这些源极场板和源触点上的电压的单独控制使得能够在晶片探针测试中检测这些电介质堆叠中的每一者中的缺陷,在不使用这些布置的情况下,无法检测这些缺陷。

41.在正常操作期间,源极探针垫428、源极场板探针垫430和第二源极场板432耦合。在对探针处的各种电介质堆叠中的缺陷进行测试之后,源极场板探针垫430、源极场板432和源极探针垫428可在裸片仍处于晶片形式时耦合在一起,或可在切割之后和封装期间耦合在一起,如下文进一步描述。

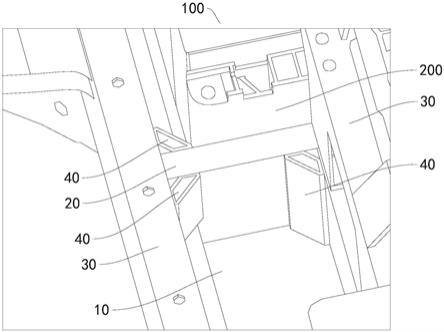

42.图5在局部平面图中说明用线接合576耦合到同一引线框架引线570的布置高压晶体管半导体裸片536的源极探针垫528、第一源极场板探针垫530和第二源极场板532。在图5中,类似的元件符号用于如图1中展示的类似元件。例如,图5中的源极探针垫528对应于图1中的源极探针垫128。高压漏极探针垫534用线接合576耦合到单独的引线框架引线572。

43.图6a和6b分别是布置高压半导体装置636的平面图和横截面图,所述装置具有用缝合接合638耦合在一起的源极探针垫628、第一源极场板探针垫630和第二源极场板探针垫632。可在切割前或切割后形成缝合接合638。在图6a和6b中,类似的元件符号用于如图1中展示的类似元件。例如,图6a和6b中的源极探针垫628对应于图1中的源极探针垫128。在高压晶体管装置636安装在引线框架675上之后(在图6b),源极探针垫628和高压漏极探针垫634用线接合676耦合到引线框架引线670和672。展示形成在装置605的部分上方的聚酰

亚胺保护覆盖层636。

44.图7a和7b分别是另一布置高压晶体管装置705的局部平面图和横截面图。装置705展示为具有通过短路条788耦合在一起的源极探针垫728、第一源极场板探针垫730和第二源极场板探针垫732。展示耦合栅极场板探针垫740和栅极探针垫744的短路条(参见图3b)。在图7a和7b中,类似的元件符号用于如图6a和6b中展示的类似元件。例如,图7a和7b中的源极探针垫728对应于图6a和6b中的源极探针垫628。短路条788可在使用标准互连光刻沉积、图案化和蚀刻工艺以晶片形式进行最终测试后添加。在替代方案中,短路条可以晶片形式或使用导电墨水的喷墨沉积后切割的形式添加。在所述布置中,源极探针垫728、漏极探针垫734和栅极探针垫744使用线接合776分别耦合到引线框架775的引线框架引线770、772和778。展示覆盖在保护性覆盖层736上的短路条788,保护性覆盖层736在探针垫之间覆盖装置705。

45.图8a和8b分别是用导电重布层891耦合在一起的源极探针垫828、第一源极场板探针垫830和第二源极场板探针垫832的平面图和横截面图。在图8a和8b中,类似的元件符号用于如图6a和6b中展示的类似元件。例如,图8a和8b中的源极探针垫828对应于图6a和6b中的源极探针垫628。在最终探针测试之后,沉积覆盖探针垫828、830、832和834以及imd2层836的例如聚酰亚胺的电介质层890。导电材料891的重布层沉积在电介质层890上,并被图案化以形成源极接合垫892和漏极接合垫894。延伸穿过电介质层890的通孔将源极探针垫828、第一源极场板探针垫830和第二源极场板探针垫832耦合到源极接合垫892。漏极探针垫834用穿过电介质层890的通孔耦合到漏极接合垫894。源极接合垫892和漏极接合垫894用线接合876连接到引线框架875上的引线框架引线870和872。

46.图9a到9d在横截面图中展示另一布置,其中当芯片安装在衬底上时,源极探针垫928、第一源极场板探针垫930和第二源极场板探针垫932耦合在一起。在图9a到9d中,类似的元件符号用于如图6a和6b中展示的类似元件。例如,图9a到9d中的hv

‑

hemt 905对应于图6a和6b中的hv

‑

hemt 605。在图9a中,在源极探针垫928、第一源极场板探针垫930、第二源极场板探针垫932和高压漏极探针垫934上形成球接合980。

47.具有引线970和972的衬底984在图9b中说明。衬底可为印刷电路板、引线框架或任何具有导电引线的非导电衬底。可使用预模制引线框架(pmlf)和模制互连衬底(mis)衬底。部分蚀刻的引线框架可与所述布置一起使用。

48.图9c展示倒装在衬底984上的引线970和972上的hv

‑

hemt 905。图9d展示倒装在引线框架975上的hv

‑

hemt 905。源极探针垫928、第一源极场板探针垫930和第二源极场板探针垫932上的球接合980全部通过接合到相同的衬底或引线框架引线970而耦合在一起。在高压漏极探针垫934和单独的衬底或引线框架引线972之间形成单独的球接合980。

49.图10a到10d以一系列横截面图描绘用于形成封装的高压晶体管的主要步骤,所述晶体管具有耦合到源极探针垫的单独源极场板探针垫。主要步骤也在图11的流程图中描述。在图10a到10d中,类似的元件符号用于如图1中展示的类似元件。例如,图10a中的源极探针垫1028对应于图1中的源极探针垫128。

50.在图10a中(图11中的步骤1101、1103、1105、1107、1109和1111),电压应力被顺序地施加到第二源极场板、第一源极场板和栅极场板下的单独电介质堆叠,以检测电介质堆叠中的缺陷。首先,在步骤1101中,将源极探针垫1028接地(参见vsource 1095),将第一源

极场板探针垫1030接地(参见vsfp1 1096),将第二源极场板探针垫1033接地(参见vsfp2 1097),并将高压施加到漏极探针垫1034(参见vdrain 1098)。这将高压应力施加到第二源极场板1032和延伸漏极区(1013)下方的第三部分之间的电介质堆叠(imd2层1026/imd层1016/pmd层1010)。如果第二源极场板探针垫1033和漏极探针垫1034之间的泄漏超过规范,那么电介质堆叠是有缺陷的,并且可报废hv

‑

hemt(步骤1103)。其次,在步骤1105中,源极探针垫1028上的电压保持接地(参见vsource 1095),第二源场探针垫1033上的电压升高(参见vsfp2 1097),导致第二源极场板1032下的延伸漏极区域的部分的电势升高,从而将电压应力施加到第一源极场板1022和下方的第二延伸漏极区域(1011)之间的电介质堆叠(imd1层1016/pmd层1010)。第一源极板探针垫1030处的电压接地(vsource 1096)。如果第一源极场板探针垫1030和漏极探针垫1034之间的泄漏电流超过规范,那么电介质堆叠(imd1层1016/pmd层1010)是有缺陷的,并且可报废hv

‑

hemt(步骤1107)。第三,在步骤1109中,第一和第二源极场板探针垫1030和1033上的电压升高(参见1096,vspf1和1097,vspf2),导致第一和第二源极场板1022和1032下方的第二和第三漏极区的电势升高,从而将电压应力施加到栅极场板1012下的pmd 1010。如果栅极场板1012和漏极探针垫1034之间的泄漏电流超过规范,那么pmd层1010是有缺陷的,并且可报废hv

‑

hemt(步骤1111)。以这种方式,通过使用所述布置,包含第二源极场板1032、第一源极场板1022和栅极场板1012的每一个场板下的电介质堆叠可有利地单独受应力,并且有缺陷的电介质堆叠可被检测到。用两个源极场板1022和1032说明应力测试。也可使用一个源极场板或多于两个的源极场板。在使用所述布置时,可在晶片探针测试中检测到电介质缺陷,而在以前的方法中,电介质缺陷只在封装完成后检测到。

51.在图10b中(步骤1113、图11),高压晶体管裸片1005安装在衬底上。引线框架1075衬底用于说明。

52.在图10c中(步骤1115,图11),线接合用于形成将第一源极场板探针垫1030和第二源极场板探针垫1033耦合在一起并耦合到源极探针垫1028的缝合接合1038。线接合还在源极探针垫1028和引线框架1075的引线框架引线1072之间以及漏极探针垫1034和引线框架引线1074之间形成线接合(步骤1117,图11)。或者,可使用例如在图5、6、7、8和9中描述的将源极场板探针垫连接到源极探针垫的其它方法。

53.图10d(步骤1119,图11)展示封装的高压晶体管,其第一源极场板探针垫1030和第二源极场板探针垫1033耦合到源极探针垫1028。高压晶体管1005、线接合1076和引线框架1075的一部分部分地围封在模塑料1099中,以形成封装的高压晶体管1095。

54.在描述的布置中,修改是可能的,且在权利要求书的范围内,其它替代布置是可能的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。