光学引擎

1.相关申请的交叉参考

技术领域

2.根据本公开的实施方案的一个或多个方面涉及光电子系统,且更具体地说,涉及一种光学引擎。

背景技术:

3.相关技术的光收发器可以封装在相对较大的封装中,并且在操作中,部分由于它们的尺寸,可以被放置成距它们可以连接的电交换电路系统相对较远。除了增加所述系统的整体尺寸之外,这种放置可能导致需要可能消耗大量功率的电收发器电路系统来实现光收发器与电交换电路系统之间的高速电通信。

4.因此,需要一种用于光收发器或光学引擎的封装的改进设计。

技术实现要素:

5.根据本发明的实施方案,提供一种光学引擎,所述光学引擎包括电子对接部件,所述电子对接部件包括:上表面,其具有用于形成与主机板的对应多个连接的多个导体;下表面,其具有用于形成与一个或多个光电子元件的对应多个连接的多个导体;以及从下表面延伸到上表面的多个通孔。

6.在一些实施方案中,所述电子对接部件包括硅穿孔管芯,并且所述多个通孔包括位于硅穿孔管芯中的多个硅穿孔。

7.在一些实施方案中,所述硅穿孔管芯包括电阻率为至少30欧姆

‑

厘米的硅。

8.在一些实施方案中,所述电子对接部件包括硅集成电路,所述硅集成电路包括从由以下组成的组中选择的晶体管电路:用于接收和放大光电探测器信号的放大器电路,以及用于驱动光调制器的驱动器电路。

9.在一些实施方案中,所述光学引擎还包括光电子器件,所述光电子器件是从由光电探测器和调制器组成的组中选择的元件。

10.在一些实施方案中,所述光学引擎还包括从晶体管电路到光电子器件的导电路径,所述导电路径具有小于500微米的长度。

11.在一些实施方案中,所述电子对接部件包括位于电子对接部件的底表面上的重分布层。

12.在一些实施方案中,所述光学引擎还包括硅光子集成电路,所述电子对接部件固定到硅光子集成电路的顶表面,所述电子对接部件的下表面的所述多个导体连接到硅光子集成电路的顶表面上的互连层。

13.在一些实施方案中:所述电子对接部件包括硅集成电路,所述硅集成电路包括硅穿孔部分,并且所述多个通孔包括位于硅穿孔部分中的多个硅穿孔。

14.在一些实施方案中,所述硅集成电路包括电阻率为至少30欧姆

‑

厘米的硅。

15.在一些实施方案中,电子对接部件包括晶体管电路,所述晶体管电路选自由以下组成的组:用于接收和放大光电探测器信号的放大器电路,以及用于驱动光调制器的驱动器电路。

16.在一些实施方案中,所述光学引擎还包括光电子器件,所述光电子器件是从由光电探测器和调制器组成的组中选择的元件。

17.在一些实施方案中,所述光学引擎还包括从晶体管电路到光电子器件的导电路径,所述导电路径具有小于250微米的长度。

18.在一些实施方案中,所述电子对接部件包括位于电子对接部件的底表面处的全局互连层。

19.在一些实施方案中,所述光学引擎还包括硅光子集成电路,所述电子对接部件固定到硅光子集成电路的顶表面,所述电子对接部件的下表面的所述多个导体连接到硅光子集成电路的顶表面上的互连层。

附图说明

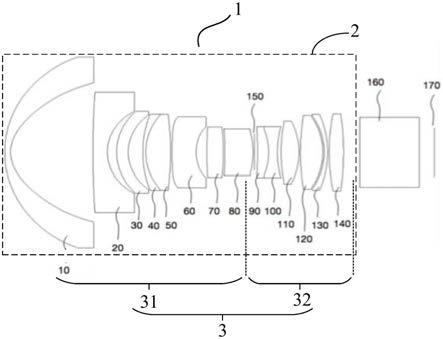

20.参考说明书、权利要求和附图,将明白和理解本公开的这些和其他特征以及优点,其中:

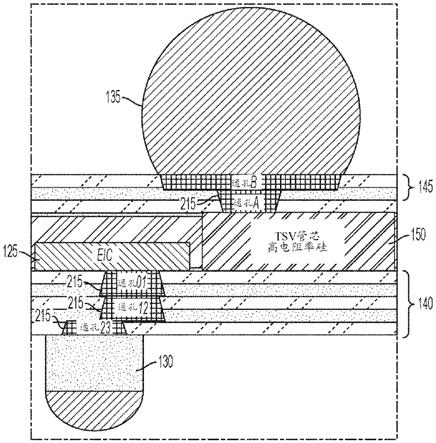

21.图1a是根据本公开的实施方案的光学引擎的示意性横截面侧视图;

22.图1b是根据本公开的实施方案的图1a的一部分的近似放大视图;

23.图2a是根据本公开的实施方案的堆叠图;

24.图2b是图2a的实施方案的一部分的放大视图;

25.图2c是根据本公开的实施方案的用于图2a和图2b的实施方案的材料表;

26.图2d是根据本公开的实施方案的通孔特性表;

27.图2e是示出根据本公开的实施方案的封装堆叠的表;

28.图3a是根据本公开的实施方案的光学引擎的示意性横截面侧视图;

29.图3b是根据本公开的实施方案的图3a的一部分的近似放大视图;

30.图4a是根据本公开的实施方案的堆叠图;

31.图4b是根据本公开的实施方案的用于图4a的实施方案的材料表;

32.图5是根据本公开的实施方案的图3a的一部分的近似放大视图;和

33.图6是根据本公开的实施方案的s21随频率而变的曲线图。

具体实施方式

34.下面结合附图阐述的详细描述旨在作为根据本公开提供的光学引擎的示例性实施方案的描述,而不旨在表示可以构造或利用本公开的仅有形式。所述描述结合所示实施方案阐述本公开的特征。然而,应当理解,相同或等效的功能和结构可以通过不同的实施方案来实现,这些实施方案也旨在涵盖在本公开的范围内。如本文别处所示,相似的元件编号旨在表示相似的元件或特征。

35.参考图1a和图1b,在一些实施方案中,光学引擎包括位于硅光子集成电路115上的扇出晶片级封装110。硅光子集成电路115可以耦合到一个或多个光纤,光学引擎可以使用每个光纤来接收经调制光(携带数据)或传输经调制光。硅光子集成电路115可以包括一个

或多个光电子器件,例如用于将光信号转换成电信号的光电探测器,或者调制器120(例如,作为以倒装焊技术组装在硅光子集成电路115上的单独的iii

‑

v芯片)。每个调制器120可以被配置成接收未调制的光(例如,在光纤之一中被引导到光学引擎的激光),并且执行光的振幅调制。调制器120可以是例如马赫

‑

曾德尔调制器或电致吸收调制器。

36.光电探测器可以直接制作在硅光子集成电路115上(例如,部分由在硅光子集成电路115的晶片上生长的晶体sige形成),或者光电探测器可以是单独的芯片(例如,以倒装焊技术组装在硅光子集成电路115上的单独的iii

‑

v芯片)。硅光子集成电路115还可以包括用于在光纤与光电子器件之间路由光的光波导,以及用于在以下之间转换光模式尺寸的锥体(例如锥形波导):(i)可以在光纤上传播的光模式尺寸,(ii)适合于在硅光子集成电路115的表面(例如顶表面)上有效引导光的光模式尺寸,以及(iii)适合与光电子器件相互作用的光模式尺寸。

37.扇出晶片级封装110可以包括一个或多个电子集成电路(eic)125,其可以作为通向光电探测器和调制器120的接口来操作。例如,电子集成电路125可以包括用于放大来自光电探测器的电信号的互阻抗放大器,以及用于驱动调制器120的驱动器放大器。如图所示,每个电子集成电路125可以位于扇出晶片级封装110的边缘附近,以减少(i)光电探测器和调制器120与(ii)与其对接的电子集成电路125之间的电路径长度。为简单起见,图1a仅示出扇出晶片级封装110一侧上的一个调制器120;在一些实施方案中,诸如光电探测器或调制器120等光电子器件可以存在于扇出晶片级封装110的两侧上或其周边,每个光电子器件在光电子器件附近的边缘处连接到扇出晶片级封装110中的一个或多个电子集成电路125。

38.扇出晶片级封装110可以包括位于扇出晶片级封装110的底表面上的下重分布层(rdl)140。与硅光子集成电路115上的光电子器件的电连接可以通过扇出晶片级封装110的底表面上的多个导体(例如铜柱130)形成。这些导体可以在硅光子集成电路115的顶表面上形成与互连层的连接,所述互连层可以包括一个或多个绝缘层和一层或多层导电(例如金属)迹线。硅光子集成电路115的顶表面上的互连层又可以形成与硅光子集成电路115上的光电子器件的连接。

39.如此,从电子集成电路125之一到光电子器件(例如到调制器120)的电路径可以穿过下重分布层140中的导电迹线延伸到铜柱130,穿过铜柱130延伸到硅光子集成电路115的顶表面上的互连层,并穿过硅光子集成电路115的顶表面上的互连层延伸到光电子器件。分离光电子器件和扇出晶片级封装110的间隙可以是约100微米(如图1a所示),使得当扇出晶片级封装110被放置在硅光子集成电路115上时,扇出晶片级封装110的尺寸的制造变化以及将其放置在硅光子集成电路115上时的误差不会导致扇出晶片级封装110与光电子器件碰撞。光电子器件与电子集成电路125之间的电路径可以具有小于500微米的长度(例如,350微米或更小的长度)。

40.扇出晶片级封装110可以在其顶表面上具有多个导体,例如焊球135,以用于制作与主机板或交换机asic衬底的多个连接。主机板或交换机asic衬底可以包括电子数据处理电路系统,例如cmos分组交换电路。扇出晶片级封装110还可以在其顶表面上具有上重分布层145。如果存在上重分布层145,则焊球135可以连接到上重分布层145中的导电迹线。硅穿孔管芯150在下重分布层140与上重分布层145(如果存在)之间(或者如果不存在上重分布

层145,则在下重分布层140与焊球135之间)形成导电路径。如果不存在上重分布层145,则焊球135可以仅存在于硅穿孔管芯150的顶表面上,或者不在硅穿孔管芯150的顶表面上的任何焊球135可以不连接,或者例如连接到下一个更高级组件上的接地。硅穿孔管芯150可以由高电阻率硅(例如,电阻率为至少30欧姆,例如,电阻率为50欧姆

‑

厘米或更高的硅)形成,使得在通过硅穿孔管芯150中的导体传播时引起的插入损耗不会高得不可接受,如下面进一步详细讨论的。扇出晶片级封装110可以作为电子对接部件来操作,以用于在硅光子集成电路115与主机板(或交换机asic衬底)之间形成接口。环氧树脂包覆膜可以包封电子集成电路125和硅穿孔管芯150。

41.图1b示出图1a的一部分的示意性或近似放大视图(图1b的尺寸和元件与图1a的尺寸和元件有些不同)。

42.图2a和图2b示出针对一些实施方案的图1a和图1b的扇出晶片级封装110的各层的堆叠,包括下重分布层140、上重分布层145和硅穿孔管芯150的堆叠。图2b是硅穿孔管芯150和形成在其上的铜柱凸块210的放大视图。在图2b中,“fsin”是指正面氮化硅,“bo”是指背面氧化物,且“bpi”是指背面聚酰亚胺。对于一些实施方案,尺寸以微米示出。在所示的实施方案中,下重分布层140由绝缘材料层(例如聚酰亚胺)和导电材料层(例如铜,具有rdl通孔215,例如镀铜微通孔via01、via12和via23)组成,以在电子集成电路125与硅光子集成电路115之间形成电连接。上重分布层145类似地由绝缘层和导电层组成,以在硅穿孔管芯150与下一个更高级组件(例如,主机板或交换机asic衬底)之间形成电连接。对于本实施方案,硅穿孔管芯150由在150微米厚的硅中形成的30微米通孔组成,从而得到硅穿孔纵横比为至少6:1。

43.三个互连层和铜柱凸块层形成在硅穿孔管芯150中的硅穿孔205的顶部上。所述三个互连层由绝缘层(例如二氧化硅)和导电层(例如铜,具有镀铜通孔v5和v6)组成,以在硅穿孔205与铜柱凸块210之间形成电互连。50微米高的铜柱凸块210用于在硅穿孔205与上重分布层145之间提供电连接。可以使用平行的硅穿孔205(如图2b中的硅穿孔管芯150的右侧部分所示)来增加电流处理并提高良率。图2a和图2b中的数字(例如,图2a中的“5”、“10”、“12”,以及图2b中的“30”、“35”、“40”、“75”、“150”)分别表示层厚度和横向尺寸。图2c示出材料(由图2c的第一列中的材料id号标识,以及由图2a中的对应注释(例如,“mat id 4”、“mat id 1”)标识)和材料性质,对于列出的绝缘体,包括介电常数(dk)和介电正切(df)。图2d示出rdl通孔215的特性。在图2d中,“开始”和“停止”标识rdl通孔215开始和停止的层(“ubm”是焊球135下面的凸块下金属化层)。在一些实施方案中,图2e是封装堆叠。在图2e中,“1 0 2”表示封装包括1层背面布线和2层正面布线。

44.图3a示出一个实施方案中的光学引擎,其中采用单个硅集成电路310来代替图1a的扇出晶片级封装110,以作为电子对接部件来操作,用于在硅光子集成电路115与主机板(或交换机asic衬底)之间形成接口。硅集成电路310包括一个或多个晶体管电路325(例如,前道工序(feol)有源区),例如用于放大来自光电探测器的电信号的互阻抗放大器和用于驱动调制器120的驱动器放大器。这些晶体管电路可以作为通向光电探测器和调制器120的接口来操作。硅集成电路310可以包括位于其底表面处(例如,恰好在内部)的背面全局互连层340,以及位于其顶表面处(例如,恰好在内部)的正面全局互连层345。

45.类似于图1a的扇出晶片级封装110,图3a的硅集成电路310可以包括:多个导体,例

如铜柱130,其用于形成与硅光子集成电路115的顶表面上的互连层的连接;以及多个导体,例如焊球135,其位于硅集成电路的顶表面上,用于形成与主机板或交换机asic衬底的多个连接。硅集成电路310可以包括中间工序(meol)硅穿孔部分350,其用于以类似于图1a的扇出晶片级封装110的硅穿孔管芯150的方式的方式形成从背面全局互连层340到正面全局互连层345的连接。在制作出晶体管电路325之后,可以在硅集成电路310中制作硅穿孔部分350。

46.硅集成电路310的制作公差可比图1a的扇出晶片级封装110的制作公差显著更严格。如此,可以将光电子器件放置成更靠近硅集成电路310,使得光电子器件与硅集成电路310之间的间隙例如为50微米或更小,并且晶体管电路325与它们所连接的光电子器件之间的电路径可以对应地更短。光电子器件与电子集成电路125之间的电路径可以具有小于250微米的长度(例如,150微米或更小的长度)。

47.图3b示出图3a的一部分的示意性或近似放大视图(图3b的尺寸和元件与图3a的尺寸和元件有些不同)。对于一些实施方案,图4a示出图3a和图3b的硅集成电路310的各层的堆叠,包括正面全局互连层345、背面互连层340和硅穿孔部分350的堆叠。对于一些实施方案,尺寸以微米示出,并且材料(在图4b的表格中列出)由对应的注释(例如,“mat id 19”、“mat id 17”)示出。在一个实施方案中,图5示出硅集成电路310的一部分中的各种元件的尺寸。所示部分包括晶体管电路325的一部分、硅穿孔部分350的一部分和背面全局互连层340的一部分。图5相对于图3a颠倒,使得例如背面全局互连层340在图5的视图中位于硅集成电路310的顶部处。

48.图6示出对于用于形成硅穿孔管芯150或用作形成硅集成电路310的衬底的硅的电阻率的各种值,通过硅穿孔传输的s21(对应于插入损耗)随频率而变的模拟结果。图例中标记为“inf”的最顶部曲线对应于零电导率的假设硅。可以看出,在低于20ghz的频率下,电阻率为50欧姆

‑

厘米的硅的插入损耗小于0.25db,并且其显著低于例如电阻率为10欧姆

‑

厘米的硅的插入损耗。

49.为易于描述起见,本文中可能使用例如“在

……

之下”、“在

……

下方”、“下部”、“在

……

下面”、“在

……

上方”、“上部”等空间相对性术语来描述如图所示的一个元件或特征与另一个元件或特征的关系。应当理解,除了附图中描绘的取向之外,这种空间相对性术语旨在涵盖器件在使用中或操作中的不同取向。例如,如果图中的器件被翻转,则被描述为在其他元件或特征“下方”或“之下”或“下面”的元件将被取向为在其他元件或特征“上方”。因此,示例性术语“在

……

下方”和“在

……

下面”可以涵盖上方和下方的取向。所述器件可以其他方式取向(例如,旋转90度或处于其他取向),并且本文使用的空间相对性描述语应相应地进行解释。

50.尽管本文已经具体描述和示出了光学引擎的示例性实施方案,但是许多修改和变化对于本领域技术人员来说将是显而易见的。因此,应当理解,根据本公开的原理构造的光学引擎可以不同于本文具体描述的方式来实施。本发明也在所附权利要求及其等同物中限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。