1.本技术涉及半导体封装技术领域,尤其涉及一种混合嵌埋封装结构及其制作方法。

技术背景

2.随着电子技术的发展与进步,电子产品朝着短小轻薄的方向演进,而电子产品的功能要求越来越强大,促进了电子产品的封装结构朝着高度集成化、小型化的方向发展,电子器件等元器件嵌埋封装应运而生,呈逐步替代wb封装(引线键合封装)的趋势。但相对而言,对于i/o数较少的电子器件,与嵌埋封装后做rdl(redistribution layer重新布线层)相比,wb封装的成本和加工周期更有优势;而且部分器件的特殊应用,很难通过嵌埋封装的方式来实现,例如led、光电二极管等涉及光源发光或者接收光的器件,传统方式嵌埋封装后,器件的发光、接收光都受到影响。因此在短时间内,wb封装仍将扮演重要的角色。

3.现有技术中,传统的wb封装方式是将电子器件等元器件通过贴装的方式,固定于基板的表面,然后进行打线,将电子器件等元器件与基板进行电性连接,最后注塑封装。该方法的缺点在于:电子器件等元器件贴装于基板表面以及打线的方式都使封装体积变大,无法满足高密度集成、小型化的发展需求。

4.传统的电子器件嵌埋封装方法,是电子器件等元器件贴装于预设空腔的聚合物框架或者core材,使用塑封材料封装后,制作rdl(redistribution layer重新布线层)。该方法的缺点在于:对于i/o数较少的电子器件,嵌埋封装后再做rdl,与wb封装相比,成本更高、加工周期更长;而且由于部分器件的特殊应用,很难通过嵌埋封装的方式来实现,例如led、光电二极管等涉及光源发光或者接收光的器件,传统方式嵌埋封装后,器件的发光、接收光都受到影响。

5.申请内容

6.本技术旨在至少在一定程度上解决相关技术中的技术问题之一。为此,本技术提出一种混合嵌埋封装结构及其制作方法,通过将嵌埋封装和wb封装相结合的混合嵌埋封装,使封装体在实现高度集成化、小型化的同时,可以满足特殊器件的特殊封装需求,以下是对本文详细描述的主题的概述。本概述并非是为了限制权利要求的保护范围。所述技术方案如下:

7.第一方面,本技术实施例提供一种混合嵌埋封装结构制作方法,其特征在于,包括以下步骤:

8.制作基板,所述基板包括第一绝缘层,贯穿所述第一绝缘层的导通铜柱,开设在所述第一绝缘层上的埋芯空腔和与所述导通铜柱电性连接的第一线路层;

9.在所述基板的底部设置支撑件,所述支撑件用于预固定电子器件组件;

10.在所述埋芯空腔对应的所述支撑件内侧预固定所述电子器件组件,所述电子器件组件包括第一电子器件和第二电子器件,所述第二电子器件设置在所述第一电子器件的背面,且所述第一电子器件的端子面朝向所述支撑件,所述第二电子器件的端子面背向所述

第一电子器件;

11.对所述电子器件组件进行封装,并露出局部所述第一线路层以及第二电子器件的端子,形成第二绝缘层;

12.去除所述支撑件;

13.在所述基板的底部制作第二线路层;

14.打线,将所述第二电子器件的端子和所述第一线路层连接。

15.根据本技术第一方面实施例的混合嵌埋封装结构制作方法,至少具有以下有益效果:第一方面,本技术提出的混合嵌埋封装结构制作方法,将嵌埋封装与wb封装相结合,对封装的电子器件等元器件选择性进行嵌埋封装或者wb封装(引线键合)的方式,可以降低生产成本、缩短加工周期;第二方面,可以将传感、光感器件(led、pd等)集成于基板内部,并可实现将传感、光感器件外露,缩小封装体积的同时,不影响传感、光感器件发送/接收信号;第三方面,将要进行wb的第二电子器件固定于嵌埋的第一电子器件的背面,然后打线将wb第二电子器件与基板电性连接。

16.可选地,在本技术的一些实施例中,在所述基板的底部及至少部分所述第二线路层表面制作阻焊层;在所述第一线路层和所述第二线路层表面进行处理形成表面处理层。

17.可选地,在本技术的一些实施例中,还包括在所述基板的顶面施加保护罩。

18.可选地,在本技术的一些实施例中,所述制作基板的具体步骤包括:

19.准备一承载板,所述承载板从下往上依次包含核心层、第一金属层、第二金属层、蚀刻阻挡层和第一金属种子层;

20.在所述第一金属种子层的表面制作第一光阻层,所述第一光阻层设置有导通铜柱开窗和牺牲铜柱开窗;

21.在所述导通铜柱开窗和牺牲铜柱开窗位置分别制作导通铜柱和牺牲铜柱;

22.去除所述第一光阻层,;

23.层压绝缘层,覆盖铜柱,减薄绝缘层,露出所述导通铜柱和所述牺牲铜柱端部,形成所述第一绝缘层;

24.在露出铜柱的表面制作第二金属种子层;

25.在所述第二金属种子层表面施加光阻材料,对光阻材料进行曝光及显影,制作第一线路层图形,形成第二光阻层。

26.线路电镀,去除第二光阻层及外露的第二金属种子层,形成所述第一线路层。

27.将所述第一金属层和所述第二金属层之间进行分离;

28.去除所述第二金属层、蚀刻阻挡层和第一金属种子层;

29.双面施加光阻材料,对光阻材料进行曝光及显影,覆盖所述第一线路层及所述导通铜柱,露出所述牺牲铜柱;

30.去除所述牺牲铜柱,形成所述埋芯空腔。

31.可选地,所述第一电子器件和所述第二电子器件之间通过粘性材料连接。

32.可选地,所述第二电子器件的端子板还设置有传感器。

33.可选地,所述对所述电子器件组件进行封装,并露出局部所述第一线路层503以及第二电子器件的端子,形成第二绝缘层的具体步骤为:

34.使用绝缘材料对电子器件进行封装;

35.对绝缘材料进行处理,露出局部第所述第一线路层、所述第二电子器件的端子及所述传感器,形成第二绝缘层。

36.可选地,所述第二绝缘层采用的绝缘材料为感光型绝缘材料,通过对感光型绝缘材料进行曝光及显影处理,露出局部第所述第一线路层、所述第二电子器件的端子及所述传感器,形成第二绝缘层。

37.可选地,所述在所述基板的底部制作第二线路层的具体步骤为:

38.在所述基板底面制作第三金属种子层;

39.采用贴膜或者涂覆的方式在双面施加光阻材料;

40.对光阻材料进行曝光及显影,顶面整版遮蔽,底面制作第二线路层图形,形成第五光阻层和第六光阻层;

41.电镀第二线路;

42.去除第五光阻层和第六光阻层;

43.蚀刻金属种子层,去除外露的所述第三金属种子层,形成第二线路层。

44.可选地,所述第一绝缘层为纯树脂或者包含树脂和玻纤的有机绝缘材料。

45.第二方面,本技术实施例提供了一种混合嵌埋封装结构制作方法,其特征在于,包括以下步骤:

46.制作基板,所述基板包括第一绝缘层,贯穿所述第一绝缘层的导通铜柱,开设在所述第一绝缘层上的埋芯空腔和与所述导通铜柱电性连接的第一线路层;

47.在所述基板的底部设置支撑件;

48.在所述埋芯空腔对应的所述支撑件内侧预固定第一电子器件,所述第一电子器件的端子面朝向所述支撑件;

49.对所述第一电子器件进行封装,并露出局部所述第一线路层以及第一电子器件的背面,形成第二绝缘层,其中所述第二绝缘层在所述第一电子器件的背面形成至少两个开窗;

50.去除所述支撑件;

51.在所述基板的底部制作第二线路层;

52.在所述第一电子器件背面所述第二绝缘层的所述开窗处设置第二电子器件,所述第二电子器件的端子面背向所述第一电子器件;

53.打线,将所述第二电子器件的端子和所述第一线路层连接。

54.可选地,在本技术的一些实施例中,在所述基板的底部及至少部分所述第二线路层表面制作阻焊层;在所述第一线路层和所述第二线路层表面进行处理形成表面处理层。

55.可选地,在本技术的一些实施例中,还包括在所述基板的顶面施加保护罩。

56.根据本技术第二方面实施例的混合嵌埋封装结构制作方法,至少具有以下有益效果:第一方面,本技术提出的混合嵌埋封装结构制作方法,将嵌埋封装与wb封装相结合,对封装的电子器件等元器件选择性进行嵌埋封装或者wb封装(引线键合)的方式,可以降低生产成本、缩短加工周期;第二方面,可以将传感、光感器件(led、pd等)集成于基板内部,并可实现将传感、光感器件外露,缩小封装体积的同时,不影响传感、光感器件发送/接收信号;第三方面,将要进行wb的第二电子器件固定于嵌埋的第一电子器件的背面,然后打线将wb第二电子器件与基板电性连接;第四方面,将要进行wb的第二电子器件跟进需要可设置多

个,每个电子元器件的类型也可以任意搭配,可相同或者不同,设计非常灵活。

57.第三方面,本技术实施例提供了一种混合嵌埋封装结构,其特征在于,包括:

58.基板500,所述基板包括第一绝缘层,贯穿所述第一绝缘层的导通铜柱,开设在所述第一绝缘层上的埋芯空腔和与所述导通铜柱电性连接的第一线路层;

59.第一电子器件,设置在所述埋芯空腔内部,且所述第一电子器件的端子面朝向基板底面;

60.第二电子器件,设置在所述第一电子器件的背面,且所述第二电子器件的端子面朝向基板顶面;

61.第二绝缘层,覆盖填充所述埋芯空腔和所述基板的上层,并露出局部所述第一线路层以及局部所述第二电子器件或者局部第一电子器件背面;

62.第二线路层,设置在所述基板的底面,所述第二线路层电性连接所述导通铜柱和所述第一电子器件的端子;

63.导线,电性连接所述第一线路层和所述第二电子器件的端子。

64.根据本技术第三方面实施例的混合嵌埋封装结构,至少具有以下有益效果:第一方面,本技术提出的混合嵌埋封装结构制作方法,将嵌埋封装与wb封装相结合,对封装的电子器件等元器件选择性进行嵌埋封装或者wb封装(引线键合)的方式,可以降低生产成本、缩短加工周期;第二方面,可以将传感、光感器件(led、pd等)集成于基板内部,并可实现将传感、光感器件外露,缩小封装体积的同时,不影响传感、光感器件发送/接收信号;第三方面,将要进行wb的第二电子器件固定于嵌埋的第一电子器件的背面,然后打线将wb第二电子器件与基板电性连接;第四方面,将要进行wb的第二电子器件跟进需要可设置多个,每个电子元器件的类型也可以任意搭配,可相同或者不同,设计非常灵活。

65.可选地,所述第二电子器件设置有一个,所述第二绝缘层覆盖填充所述埋芯空腔和所述基板的上层,并露出局部所述第一线路层以及所述第二电子器件的端子。

66.可选地,所述第二电子器件的端子面还设置有传感器,所述第二绝缘层覆盖填充所述埋芯空腔和所述基板的上层,并露出局部所述第一线路层以及所述第二电子器件的端子和所述传感器。

67.可选地,所述第二电子器件设置有至少两个,所述第二绝缘层覆盖填充所述埋芯空腔和所述基板的上层,并露出局部所述第一线路层以及局部所述第一电子器件的背面,且所述第二绝缘层在第一电子器件背面形成至少两个开窗,每个所述第二电子器件设置在对应一个开窗内。

68.可选地,当所述第二电子器件设置有至少两个时,所述至少两个的所述第二电子器件可以采用相同的电子元器件也可以采用不同的电子元器件。

69.可选地,所述第二电子器件通过粘性材料设置在所述第一电子器件601的背面。

70.可选地,还包括阻焊层,所述阻焊层至少局部覆盖所述第二线路层。

71.可选地,还包括保护罩,所述保护罩设置在所述基板的顶面。

72.可选地,所述保护罩采用透光罩。

73.本技术的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本技术而了解。本技术的目的和其他优点可通过在说明书、权利要求书以及附图中所特别指出的结构来实现和获得。

附图说明

74.附图用来提供对本技术技术方案的进一步理解,并且构成说明书的一部分,与本技术的实施例一起用于解释本技术的技术方案,并不构成对本技术技术方案的限制。

75.图1是本技术第一个实施例提供的混合嵌埋封装结构制作方法的步骤流程图;

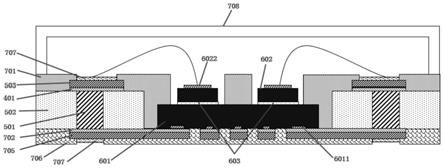

76.图2至图17是本技术第一个实施例提供的封装基板制作方法步骤对应的截面图;

77.图18是本技术第二个实施例提供的混合嵌埋封装结构制作方法的步骤流程图;

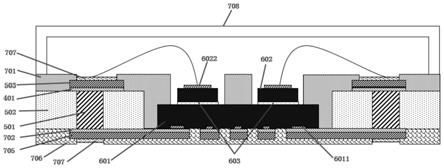

78.图19至图25是本技术第二个实施例提供的封装基板制作方法步骤对应的截面图;

79.图26是本技术第一个实施例提供的封装基板的截面图;

80.图27是本技术第二个实施例提供的封装基板的截面图。

具体实施方式

81.为了使本技术的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本技术进行进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本技术,并不用于限定本技术,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本技术所能产生的功效及所能达成的目的下,均应仍落在本技术所揭示的技术内容得能涵盖的范围内。

82.本部分将详细描述本技术的具体实施例,本技术之较佳实施例在附图中示出,附图的作用在于用图形补充说明书文字部分的描述,使人能够直观地、形象地理解本技术的每个技术特征和整体技术方案,但其不能理解为对本技术保护范围的限制。

83.在申请的描述中,若干的含义是一个或者多个,多个的含义是两个及两个以上,大于、小于、超过等理解为不包括本数,以上、以下、以内等理解为包括本数。如果有描述到第一、第二只是用于区分技术特征为目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量或者隐含指明所指示的技术特征的先后关系。

84.参照图1,本技术的一个实施例提供的一种混合嵌埋封装结构制作方法包括以下步骤:

85.s100,制作基板500,基板包括第一绝缘层502,贯穿第一绝缘层502的导通铜柱501,开设在第一绝缘层502上的埋芯空腔504和与导通铜柱501电性连接的第一线路层503;,具体地,如图2

‑

11所示,

86.进一步参照图2,准备一承载板100,承载板从下往上依次包含核心层101、第一金属层102、第二金属层103、蚀刻阻挡层104和第一金属种子层105;在一些实施例中,第一金属层102、第二金属层103可以采用金属铜层,两者之间通过物理方式结合,可进行分离;后续将第一、第二金属层102、103进行分离后,对第二金属层103进行蚀刻时,蚀刻阻挡层104可以对基板的线路和铜柱进行保护,防止过度蚀刻,蚀刻阻挡层104可选择金属镍;第一金属种子层105可选择铜,厚度为1

‑

3um,作为后续电镀的导通基础。

87.进一步参照图3,在第一金属种子层105的表面制作第一光阻层201,第一光阻层201设置有导通铜柱开窗202和牺牲铜柱开窗203;具体的,在第一金属种子层105的表面施加光阻材料,可选择贴膜或者涂覆的方式,对光阻材料进行曝光及显影,制作铜柱图形,形成第一光阻层201,第一光阻层201包含导通铜柱开窗202、牺牲铜柱开窗203,铜柱不局限于圆柱体,可以为立方体、长方体等。

88.进一步参照图4,铜柱电镀,在导通铜柱开窗202和牺牲铜柱开窗203位置分别制作导通铜柱501和牺牲铜柱302,铜柱501和302的厚度根据实际需求定义,通常低于第一光阻层201的厚度。

89.进一步参照图5,去除第一光阻层,可以通过退膜的方式去除;层压绝缘层,覆盖铜柱,可以通过退膜的方式去除;减薄绝缘层,可以选择等离子蚀刻或者磨板的方式,露出导通铜柱501和牺牲铜柱302端部,形成第一绝缘层502。

90.进一步参照图6,在露出铜柱的表面制作第二金属种子层401,在一些实施例中可以选择化铜或者离子溅射的方式,第二金属种子层401可以为cu或者ti cu。

91.进一步参照图7,在第二金属种子层表面施加光阻材料,在一些实施例中可选择贴膜或者涂覆的方式,对光阻材料进行曝光及显影,制作第一线路层图形,形成第二光阻层402。

92.进一步参照图8,线路电镀,厚度根据实际需求定义,通常低于第二光阻层402厚度,去除第二光阻层402及外露的第二金属种子层401,形成第一线路层503;在一些实施例中可以选择退膜方式去除第二光阻层,通过蚀刻去除外露的第二金属种子层。

93.进一步参照图9,将第一金属层102和第二金属层103之间进行分离;去除第二金属层103、蚀刻阻挡层104和第一金属种子层105;在一些实施例中,分板面的第一金属层去除,通常采用蚀刻的方式,蚀刻阻挡层去除,通常采用特定药水蚀刻的方式,优先采用蚀刻镍药水,第一金属种子层去除,通常采用蚀刻的方式。

94.进一步参照图10,双面施加光阻材料,可选择贴膜或者涂覆的方式,对光阻材料进行曝光及显影,覆盖第一线路层及导通铜柱501,露出牺牲铜柱302,形成第三光阻层404、第四光阻层405;

95.进一步参照图11,去除牺牲铜柱302,形成埋芯空腔504,得到包含导通铜柱501、第一绝缘层502、第一线路层503及埋芯空腔504的基板500,在一些实施例中,采用蚀刻方式牺牲铜柱,可以通过退膜的方式去除第、第四光阻层。

96.s200,参照附图12,在基板500的底部设置支撑件505,支撑件505用于预固定电子器件组件,在一些实施例中,支撑件505可以采用胶带,胶带的粘性面有助于电子器件的预固定;

97.s300,在埋芯空腔504对应的支撑件505内侧预固定电子器件组件,电子器件组件包括第一电子器件601和第二电子器件602,第二电子器件602设置在第一电子器件601的背面,且第一电子器件601的端子面朝向支撑件,第二电子器件的端子面背向第一电子器件601;在一些实施例中,第一电子器件601和第二电子器件602之间可以通过粘性材料603粘合,电子器件的贴合可以是依次贴第一电子器件601、粘性材料603、第二电子器件602,也可以是直接贴第一电子器件601&粘性材料603&第二电子器件602结合的整体,即事先把第一电子器件601&粘性材料&第二电子器件602结合成为一个整体,然后将该整体贴于胶带505上。

98.s400,参照附图13,对电子器件组件进行封装,并露出局部第一线路层503以及第二电子器件的端子,形成第二绝缘层701;在一些实施例中,可采用感光型绝缘材料对芯片进行封装,然后对感光型绝缘材料进行曝光及显影,露出局部第一线路层以及第二电子器件的端子,形成第二绝缘层701;当然也可以采用普通非感光绝缘材料通过真空压合、层压、

涂覆的方式封装,再通过镭射、等离子蚀刻等方式去除绝缘材料形成开窗;还可以通过局部注塑的方式进行封装并形成开窗露出局部端子。

99.s500,参照附图14,去除支撑件505;在一些实施例中,去除支撑件505之后,先在基本500的底面制作第三金属种子层702,为第二线路层的制作做准备,第三金属种子层702,可以选择化铜或者离子溅射的方式,第三金属种子层可以为cu或者ti cu。

100.s600,参照附图15、16和17,在基板500的底部制作第二线路层705、阻焊层706,具体步骤为:

101.在双面施加光阻材料,可选择贴膜或者涂覆的方式;

102.对光阻材料进行曝光及显影,顶面整版遮蔽,底面制作第二线路层图形,形成第五光阻层703、第六光阻层704;

103.第二线路电镀,厚度根据实际需求定义,通常低于第六光阻层厚度;

104.去除第五、第六光阻层,通常可以选择退膜方式;

105.金属种子层蚀刻,去除外露的第三金属种子层,形成第二线路层705;

106.底面制作阻焊层706。其中阻焊层的制作可以根据需要制作。

107.s700,在第一线路层503和第二线路层705表面进行处理形成表面处理层707,可以选择抗氧化、化镍钯金、镀锡、化银等;对表面进行处理时,通常需要对芯片区域开窗位置进行遮蔽;

108.s800,参照附图18,打线,将第二电子器件的端子6021和第一线路层503连接,可以选择打金线、打铜线等;

109.s900,施加保护罩,打线后在顶面施加保护罩708,在一些实施例中可以选择透光的玻璃材质,当第二电子器件具有传感器或者为led等发光器件时,在进行保护封装体的同时,不影响传感器、led等的运作。

110.本技术第一方面实施例的混合嵌埋封装结构制作方法,将嵌埋封装与wb封装相结合,对封装的芯片等元器件选择性进行嵌埋封装或者wb封装(引线键合)的方式。对于i/o数较多的芯片,wb封装难度及成本较高,可以选择嵌埋封装的方式;对于i/o数较少的芯片,嵌埋封装加工周期较长、成本较高,可以选择wb的方式;对于特殊器件的特殊应用,例如led、光电二极管等设计光源发光或者接收光的器件,可以选择wb的方式,使器件外露实现光电感应。同时本技术技术方案中的wb封装结构,是将要进行wb的芯片等电子器件固定于嵌埋芯片等电子器件的背面,然后打线将wb芯片等电子器件与基板电性连接。此结构与传统的将wb器件贴装于基板表面,再打线的方式相比,封装体积得到缩小,可满足封装体高密度集成、小型化的发展需求。

111.在一些实施例中,第二电子器件602的端子板还设置有传感器6022,对电子器件组件进行封装处理后还需要露出传感器。

112.在一些实施例中,第一绝缘层可采用纯树脂或者包含树脂和玻纤的有机绝缘材料。

113.参照图17,本技术的另一个实施例提供的一种混合嵌埋封装结构制作方法,前2个步骤与第一个实施例相同,具体包括以下步骤:

114.s100b,制作基板500,基板包括第一绝缘层502,贯穿第一绝缘层502的导通铜柱501,开设在第一绝缘层502上的埋芯空腔504和与导通铜柱501电性连接的第一线路层503;

115.s200b,在基板500的底部设置支撑件505;

116.s300b,进一步参考图19,在埋芯空腔504对应的支撑件505内侧预固定第一电子器件601,第一电子器件601的端子面6011朝向支撑件;

117.s400b,进一步参考图20,对第一电子器件601进行封装,并露出局部第一线路层503以及第一电子器件的背面,形成第二绝缘层,其中第二绝缘层在第一电子器件的背面形成至少两个开窗;在本实施例中,具体使用感光型绝缘材料对芯片进行封装,对感光型绝缘材料进行曝光及显影,露出局部第一线路层以及局部第一电子元件背面,形成第二绝缘层701,第二绝缘层在第一电子器件背面形成两个开窗,分别为开窗902、开窗903,需要说明的是,开窗的数量可以不局限于两个,可以为多个,根据实际需要定义,本实施案例以两个为例;当然也可以采用普通非感光绝缘材料通过真空压合、层压、涂覆的方式封装,再通过镭射、等离子蚀刻等方式去除绝缘材料形成开窗;还可以通过局部注塑的方式进行封装并形成开窗露出局部端子。

118.s500b,进一步参考图21,去除支撑件505,在基板底面制作第三金属种子层702,可以选择化铜或者离子溅射的方式,第三金属种子层可以为cu或者ti cu;

119.s600b,进一步参考图22、23和24,在基板500的底部制作第二线路层705、阻焊层706,具体为:

120.双面施加光阻材料,可选择贴膜或者涂覆的方式;

121.对光阻材料进行曝光及显影,顶面整版遮蔽,底面制作第二线路层图形,形成第五光阻层703、第六光阻层704;

122.第二线路电镀,厚度根据实际需求定义,通常低于第六光阻层厚度;

123.去除第五、第六光阻层,通常可以选择退膜方式;

124.金属种子层蚀刻,去除外露的第三金属种子层,形成第二线路层705;

125.底面制作阻焊层706;

126.s700b,在第一线路层503和第二线路层705表面进行处理形成表面处理层,即双面进行选择性表面处理,形成表面处理层707,可以选择抗氧化、化镍钯金、镀锡、化银等,对表面进行处理时,通常需要对芯片区域开窗位置进行遮蔽;

127.s800b,进一步参考图25,在第一电子器件背面第二绝缘层的开窗处设置第二电子器件602,第二电子器件的端子面背向第一电子器件601;具体包括:在第一电子器件背面第二绝缘层每一个开窗处,施加粘性材料603,并分别贴第二电子器件602,各个第二电子器件602根据实际情况可以选择相同的电子器件,也可以选择不同的电子器件,本实施例设置2个不同的电子器件,一个为led芯片,另一个为光电二极管pd,两个不同第二电子器件的背面通过粘性材料与第一电子器件背面紧密结合;

128.s900b,打线,将第二电子器件的端子和第一线路层503连接;

129.s1000b,施加保护罩708。

130.参照图26,本技术的一个实施例提供了一种混合嵌埋封装结构,包括:

131.基板,基板包括第一绝缘层502,贯穿第一绝缘层502的导通铜柱501,开设在第一绝缘层502上的埋芯空腔504和与导通铜柱501电性连接的第一线路层503;

132.第一电子器件601,设置在埋芯空腔504内部,且第一电子器件601的端子面朝向基板底面;

133.第二电子器件,设置在所述第一电子器件的背面,且所述第二电子器件的端子面;

134.第二电子器件602,设置在第一电子器件601的背面,且第二电子器件的端子面朝向基板顶面;

135.第二绝缘层503,覆盖填充埋芯空腔504和基板的上层,并露出局部第一线路层503以及局部第二电子器件602或者局部第一电子器件背面;

136.第二线路层705,设置在基板500的底面,第二线路层705电性连接导通铜柱501和第一电子器件601的端子6011;

137.导线,电性连接第一线路层503和第二电子器件602的端子6021。

138.根据本技术实施例的混合嵌埋封装结构,将嵌埋封装与wb封装相结合,对封装的电子器件等元器件选择性进行嵌埋封装或者wb封装(引线键合)的方式,可以降低生产成本、缩短加工周期;可以将传感、光感器件(led、pd等)集成于基板内部,并可实现将传感、光感器件外露,缩小封装体积的同时,不影响传感、光感器件发送/接收信号;将要进行wb的第二电子器件固定于嵌埋的第一电子器件的背面,然后打线将wb第二电子器件与基板电性连接。

139.在一些实施例中,第二电子器件602设置有一个,第二绝缘层503覆盖填充埋芯空腔504和基板的上层,并露出局部第一线路层503以及第二电子器件602的端子。

140.在一些实施例中,第二电子器件602的端子面还设置有传感器,第二绝缘层503覆盖填充埋芯空腔504和基板的上层,并露出局部第一线路层503以及第二电子器件602的端子和传感器。

141.在一些实施例中,还包括第二金属种子层401和第三金属种子层702,第二金属种子层401设置在导通铜柱501与第一线路层503之间,第三金属种子层702设置在导通铜柱501与第二线路层705之间.

142.在一些实施例中,进一步参考图27,第二电子器件602设置有至少两个,第二绝缘层503覆盖填充埋芯空腔504和基板的上层,并露出局部第一线路层503以及局部第一电子器件601的背面,且第二绝缘层503在第一电子器件601背面形成至少两个开窗,每个第二电子器件602设置在对应一个开窗内。将要进行wb的第二电子器件跟进需要可设置多个,每个电子元器件的类型也可以任意搭配,可相同或者不同,设计非常灵活。

143.在一些实施例中,当第二电子器件602设置有至少两个时,至少两个的第二电子器件602可以采用相同的电子元器件也可以采用不同的电子元器件。

144.在一些实施例中,第二电子器件通过粘性材料设置在第一电子器件601的背面。

145.在一些实施例中,还包括阻焊层706,阻焊层706至少局部覆盖第二线路层705;

146.在一些实施例中,还包括保护罩708,设置在基板500的顶面,进一步在保护封装体;为了不影响led、pd等电子器件的运作,保护罩还可以采用透光罩,如玻璃透光罩、塑料透光罩等。

147.以上是对本技术的较佳实施进行了具体说明,但本技术并不局限于上述实施方式,熟悉本领域的技术人员在不违背本技术精神的前提下还可作出种种的等同变形或替换,这些等同的变形或替换均包含在本技术权利要求所限定的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。