1.本公开涉及解决频率合成器的参考时钟信号中存在的周期误差。

背景技术:

2.在电子通信系统中广泛使用的某些类型的振荡器会自然生成正弦波。在无线、有线和光通信链路中,此类振荡器为系统设置时间参考。跟随振荡器的频率合成器生成用于通信链路的特定且不同频率的时钟或本地振荡器信号。频率合成器更喜欢具有锐利边沿的矩形波作为其参考时钟输入,以便不易受到合成器电路中其他噪声源的影响。因此,在振荡器电路和合成器之间经常使用正弦波到矩形波转换器。然而,振荡器输出会被低频加性噪声损坏,这可能是振荡器或正弦波到方波转换器中使用的偏置电路的结果。在通过正弦到方波转换器时,这种可能很重要的低频加性噪声被转换为相位噪声,因为矩形波的边沿被加性噪声调制。这种噪声也出现在频率合成器的输出,影响时钟或本振信号的相位噪声性能,最终影响数据通信链路的性能。

3.参考图1,在示例频率合成器的相位噪声分布中,这种加性噪声的影响被示为“驼峰”101。需要更好的方法来解决噪声以提高频率合成器的性能并最终提高数据通信链路的性能。

技术实现要素:

4.因此,在一个实施例中,本发明提供了一种方法,其包括向锁相环的相位和频率检测器提供具有周期误差的参考时钟信号和反馈时钟信号。该方法还包括使用反馈分频器生成反馈时钟信号,该反馈分频器将提供给反馈分频器的时钟信号在参考时钟信号的奇数周期期间至少除以第一分频值,并在参考时钟信号的偶数周期期间至少除以第二分频值,第一分频值和第二分频值至少部分地基于对应于周期误差的误差项,反馈时钟信号具有基本上等于参考时钟信号的周期误差的反馈周期误差。

5.在另一个实施例中,本发明提供了一种装置,其包括锁相环,其具有相位和频率检测器,其被耦合以接收具有周期误差的参考时钟信号并被耦合以接收反馈时钟信号。相位和频率检测器提供指示参考时钟信号和反馈时钟信号之间的差异的信号。反馈分频器,对耦合到锁相环的振荡器的时钟信号进行分频,反馈分频器用于生成反馈时钟信号。反馈分频器被耦合以在参考时钟信号的奇数周期期间接收至少第一分频值以对时钟信号进行分频,并且在参考时钟信号的偶数周期期间接收至少第二分频值以对时钟信号进行分频。第一分频值和第二分频值至少部分地基于指示参考时钟信号的周期误差的误差项。反馈时钟信号具有反馈时钟周期误差,反馈时钟周期误差基本上等于参考时钟信号的周期误差,这至少部分地是由于在奇数周期期间将时钟信号除以第一分频值并在偶数周期期间将时钟信号除以第二分频值的结果。

6.在另一个实施例中,本发明提供了一种锁相环,其包括:相位和频率检测器被耦合以接收具有周期误差的参考时钟信号并被耦合以接收反馈时钟信号。相位和频率检测器提

供指示参考时钟信号和反馈时钟信号之间的差异的信号。反馈分频器电路对耦合到振荡器的时钟信号进行分频,并用于生成反馈时钟信号。反馈分频器控制电路,其用于在参考时钟信号的奇数周期期间向反馈分频器电路提供至少第一分频值,并且在参考时钟信号的偶数周期期间向反馈分频器电路提供至少第二分频值,从而提供反馈分频器信号。第一分频值和第二分频值至少部分地基于指示周期误差的误差项。反馈分频器控制电路包括δ

‑

∑调制器,其被耦合以在奇数周期和偶数周期期间向反馈分频器电路提供分频值,从而实现时钟信号的小数分频值。反馈时钟信号的反馈周期误差基本上等于参考时钟信号的周期误差。

附图说明

7.通过参考附图,可以更好地理解本发明,并且其众多目的、特征和优点对于本领域技术人员来说是显而易见的。

8.图1示出了参考时钟中的加性噪声对示例频率合成器的相位噪声分布的影响。

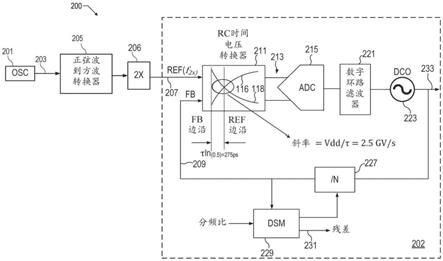

9.图2示出了示例系统的框图,该示例系统通过在参考时钟路径中使用时钟乘法器电路来改进用于参考振荡器的正弦到方波转换器的低频噪声性能。

10.图3示出了由具有不同于50%的占空比的参考振荡器信号引起的2x参考时钟信号中的周期误差。

11.图4示出了占空比变化如何导致倍增时钟信号中的周期误差的具体示例。

12.图5示出了通过使反馈分频器计数参考时钟信号的奇数和偶数周期的不同值来校正周期误差的方法。

13.图6示出了pll实施例的高级框图,该实施例通过向耦合到反馈分频器的δ

‑

∑调制器提供奇数/偶数分频值来调整反馈时钟周期的长度。

14.图7示出了如何计算在没有周期长度校正的情况下提供的反馈时钟信号与具有周期长度校正的反馈时钟信号之间的差异。

15.图8示出了确定适当的反馈分频器值以使得反馈时钟信号具有与参考时钟信号的周期误差匹配的周期误差的实施例。

16.图9示出了用于更新用于消除量化噪声的多项式的系数h1‑

h5并调整比例因子(h5)以调整反馈分频器时钟信号的周期的自适应回路。

17.图10示出了在自适应回路中使用高斯赛德尔迭代。

18.图11a示出了自适应回路中使用的协方差矩阵c

xx

。

19.图11b示出了在自适应回路中使用的协方差矩阵和互相关向量c

ex

。

20.图12示出了一个实施例,其中四个单独的分频比控制反馈分频器信号的四个子相位的持续时间,其为参考时钟信号的频率的4倍。

21.图13a示出了并非反馈分频器时钟信号的所有子相位都需要调整以解决周期误差。

22.图13b示出了在四个子相位的可用性的情况下,相位检测器看到的反馈分频器时钟周期可以不同于用于数字逻辑的数字时钟信号和adc时钟信号的周期。

23.图14示出了实现图13a和图13b中所示时序的反馈分频器控制电路的高级框图。

24.图15示出了调整某些子相位以解决参考时钟信号的周期误差但不影响pll中基于

converter”)中描述的偏置噪声的影响,并且在其相位噪声分布中有驼峰,如图1所示(可以通过随后的2x乘法器去除)。然而,由于无法访问来自xo的正弦波并调整用于生成急剧上升波形的阈值,因此无法使用其中描述的模拟占空比校正。此外,这些外部xo或vcxo的占空比可能会显着偏离理想的50%标记,其值可能在40%至60%的范围内。这意味着倍增参考时钟(multiplied reference clock)波形中可能存在显着的周期误差。图3示出了由与50%显着不同的占空比引起的问题。时序图301显示了具有50%占空比(无周期误差)的1x时钟和由此产生的2x时钟信号(将1x时钟信号的频率乘以2),其中奇数周期(t

odd

)等于偶数周期期间(t

even

)。时序图303示出了具有非50%占空比(具有周期误差)的1x时钟和由此产生的2x时钟信号(将1x时钟信号的频率乘以2),其中奇数周期(t

odd

)不等于偶数周期(t

even

)。

36.当具有显着周期误差的2x时钟信号用作使用高增益相位检测器的pll的参考输入时,周期误差会显着影响pll的vco的输出。在图2的示例实施例中,pll使用具有数百皮秒(ps)的rc时间常数(τ)的高增益相位检测器211,以实现出色的噪声性能。为了使pll的相位检测器适应倍增参考时钟的周期误差,必须降低相位检测器的增益,或者换句话说,τ需要足够大以适应2x时钟波形中的周期误差。图4示出了周期为20ns的50%占空比理想f1x时钟信号的具体示例401。然而,如果f1x的占空比如403处所示为45%/55%,则在405处所示的倍增时钟信号f2x中产生的周期误差导致短周期407和长周期409的重复模式(仅示出其中之一)。与411处所示的理想f2x波形相比,实际波形具有1ns的周期误差t

err

。也就是说,与理想的10ns相比,短周期以9ns结束,从而导致1ns的误差。这总是会导致更差的噪声性能,因为大约50mhz标称频率的45%至55%占空比1x时钟产生的周期误差在纳秒范围内,而τ在数百皮秒范围内。因此,τ将需要增加约5至10倍以适应典型外部参考中的周期误差,从而导致整个pll的噪声性能更差。

37.另一种选择是减慢1x波形(使它们缓慢上升而不是急剧上升)并使用标题为“noise canceling technique for a sine to square wave converter”的美国专利第10,840,897号中描述的模拟占空比校正。然而,降低参考时钟边沿的斜率也总是会导致噪声性能下降,因为缓慢上升的边沿明显更容易受到相位噪声劣化的影响。

38.因此,本文描述的实施例以不需要输入时钟中的慢边沿或高增益相位检测器中的浅斜率的方式来校正倍增参考时钟波形中的周期误差。相反,周期纠错完全发生在数字域中。因此,在校正1x时钟的占空比误差时发生的噪声损失不再是问题,并且在整个pll中实现了卓越的抖动性能。

39.图5示出了一种通过使反馈分频器对参考时钟信号的奇数和偶数周期进行不同值计数,从而为奇数和偶数周期除以不同值来校正周期误差的方法。如图5所示,利用实际参考时钟信号波形501(f2x实际),调整反馈分频器信号(fb)503,使得计数505的vco周期数根据周期误差而变化。因此,在图5所示的示例中,反馈分频器在参考时钟信号f2x实际的偶数周期内计数更多的vco周期,而在f2x实际的奇数周期内计数更少的vco周期。因此,周期误差被引入反馈时钟信号以匹配参考时钟信号的周期误差。由于周期误差,相位检测器将看不到反馈时钟信号和参考时钟信号之间的任何差异。

40.图6示出了pll实施例600的高级框图,该实施例通过向δ

‑

∑调制器229提供奇数/偶数分频值601来调整反馈时钟周期。pll 600的其他元素与图2中所示的pll 202相同。在一个实施例中,如本文进一步描述的,反馈分频器的奇数/偶数分频值是使用协方差矩阵方

法自适应地确定的。在一个这样的实施例中,用于矩阵求逆的高斯赛德尔算法用于确定自适应权重。

41.在其他实施例中,使用其他方法确定反馈分频器的奇数/偶数分频值以使反馈时钟信号具有与参考时钟信号的周期误差匹配的周期误差。例如,在其他实施例中,参考时钟信号的周期误差是通过例如时间到数字转换器来测量的,并且基于测量的周期误差和vco输出时钟信号(或其分频版本)的测量周期值生成奇数/偶数分频值。对应于奇数/偶数周期的奇数/偶数分频值以参考时钟信号为基础逐个周期调整反馈分频器的标称分频值。可以定期测量参考时钟信号的奇数/偶数周期以反映过程、电压和温度(pvt)的变化,或者通过背景校准算法连续测量。例如,假设反馈分频器的标称分频值为n.f,其中n代表整数项,“f”是小数项,n.f可以通过奇数/偶数调整来调整(以重复模式延长和缩短)以匹配参考时钟信号的奇数/偶数周期。

42.图7示出了如何计算在没有周期校正的情况下提供的反馈时钟信号(fb)与具有周期校正的反馈时钟信号(fb)之间的差异。反馈波形701示出了fb波形的奇数/偶数周期,其是为了匹配参考时钟信号的奇数/偶数周期(图7中未示出)而期望的。波形703示出了对反馈时钟信号的奇数/偶数周期求平均的结果。701处的奇数周期结束与703处平均周期结束之差表示为δt 705。奇数波形的周期t

odd

=t

avg

‑

δt,偶数波形的周期t

even

=t

avg

δt。奇数和偶数周期也可以根据来自dco 223的压控振荡器(vco)时钟周期的数量来定义(参见图5)。具体来说,t

odd

=(n1.f1)

×

t

vco

,t

even

=(n2.f2)

×

t

vco

,其中n1.f1是奇数周期的分频值,n2.f2是偶数周期的分频值,t

vco

是vco输出信号233的周期(参见图6)。703处所示的平均反馈时钟周期为t

avg

与奇数和偶数周期之间的差异为并且因此其中δn.δf是n2.f2‑

n1.f1的值。请注意,整数部分的差异不一定是差异的整数部分,小数部分也是如此。

43.找到δt的一种方法是使用自适应引擎来确定适当的反馈分频器值。图8示出了确定适当的反馈分频器值以使得反馈时钟信号具有与参考时钟信号的周期误差匹配的周期误差的实施例。pll 800包括rc时间

‑

电压转换器801,其通过加法器806和低通滤波器808向模数转换器(adc)805提供电压803。时间

‑

电压转换器801包括相位和频率检测器(pfd)和rc充电电路(图8中未单独示出)。电压803是表示参考时钟(ref)807和反馈时钟(fb)809之间的相位差的模拟误差信号。低通滤波器(lpf)808是将rc相位检测器的采样电压传输到adc输入的结果。这是作为电荷从rc相位检测器801(这里也称为时间

‑

电压转换器)的采样电容器转移到adc 805输入的积分电容器来实现的。该电荷转移导致离散时间低通滤波器,其效果在数字域中被逆滤波器812的作用抵消。adc 805将对应于相位差的数字误差信号提供给逆低通滤波器812。求和电路(summing circuit)806从电容器数模转换器(dac)823接收消除信号,以添加或减去消除电压以消除与δ

‑

∑调制器819相关联的量化噪声。在2017年9月12日提交的任命michael h.perrot为发明人,标题为“cancellation of spurious tones within a phase

‑

locked loop with a time

‑

to

‑

digital converter”的美国专利第9,762,250号中描述了电容器dac的一个实施例。在其他实施例中,使用不同类型的dac来增加或减少电荷以消除量化噪声。第二求和电路814基于来自δ

‑

∑调制器831的残差来调整提供给数字环路滤波器811的误差信号841,如在此进一步解释的。数字环路滤波器811控制

dco 815调整dco的输出以匹配参考时钟信号。pll 800包括小数n反馈分频器,该分频器包括在δ

‑

∑调制器819的控制下的多模反馈分频器817。δ

‑

∑调制器(dsm)819接收小数分频值n.f(在加法器820中与抖动信号相加之后)并控制多模反馈分频器817。显着的量化噪声与δ

‑

∑调制器819相关联。另外,δ

‑

∑调制器接收指示要对反馈分频器信号的周期进行调整的信号822。

44.在一个实施例中,δ

‑

∑调制器(dsm)819是传统的二阶dsm并且提供对应于待消除的δ

‑

∑量化噪声的残余序列。δ

‑

∑调制器使用抖动序列来改善量化噪声的加扰。在一个实施例中,在确定表示要消除的噪声的消除多项式之前,从残留信号中去除抖动序列。

45.在加法器826中从积分残留信号824(residue_ph)中减去累积抖动信号823,并且将减法结果x1提供给系数块h1。δ

‑

∑调制器的残留是“频率”残留。那是因为δ

‑

∑调制器的输出控制反馈分频器的瞬时分频值,即分频信号的频率。然而,在相位检测器输入,相位由所有先前反馈分频器值的总和决定。这种固有的积分意味着如果量化噪声在相位检测器输出被消除,则应使用“相位”残留而不是“频率”残留。因此,频率残留被积分以提供相位残留(residue_ph)。请注意,图8中所示的加法器和此处的其他图可以是加法或减法。将表示周期误差x

5 827的方波提供给标度块h5,并将h5x5作为误差项822提供,它代表参考时钟的每个周期的适当δt值,通过该值调整反馈时钟信号的周期以匹配参考时钟信号的周期误差。δ

‑

∑调制器819为反馈分频器817产生分频值828,其表示由周期误差项822调整的标称分频值n.f。

46.加法器826的输出x1与其他项组合以形成多项式,其对应于δ

‑

∑调制器819的残差的待消除噪声,并且基于多项式的消除值被提供给δ

‑

∑调制器831。δ

‑

∑调制器831的输出用于控制电容器dac 832,它向/从模拟误差信号(ref时钟807和fb时钟809之间的相位差)增加或减少电压以消除量化噪声。注意,图8的实施例试图通过数字信号处理来复制模拟相位检测器中发生的情况。pll中的非线性导致量化噪声及其功率出现在相位检测器的输出,通过多项式的“平方”项x2和“立方”项x3以数字方式模拟。

47.使用δ

‑

∑调制器831的一个原因是为电容器dac实现合理的数量(例如4

‑

6位)以使电容器dac实现实用化。然而,δ

‑

∑调制器831的使用导致也需要校正的残余量化噪声误差。可以使用块835中的一阶差和缩放块837中的适当缩放因子h4从δ

‑

∑调制器831的残差833估计电容器dac消除的误差。在提供给数字环路滤波器811之前,在加法器814中从数字误差信号(相位差)中减去残余误差。为了便于说明,图8中所示的高级数字信号处理框图省略了正确对准信号可能需要的延迟块。

48.模拟时间

‑

电压转换器的参数是半导体工艺和温度的函数,而数字信号处理则不是。因此,使用自适应算法来找到系数h1‑

h5,从而使得时间

‑

电压转换器的周期误差和增益和非线性度的数字估计在允许的范围内尽可能接近周期误差和模拟增益和非线性度。图9示出了用于更新系数h1‑

h5的自适应回路(adaptation loop)的实施例。实现自适应回路的自适应引擎可以在编程处理器(诸如微控制器或硬件和编程处理器的组合)上的硬件或软件/固件中实现。c

xx

是信号x1、x2、x3、x4和x5的协方差矩阵(如图8所示),c

ex

是误差与x1‑

x5的互相关向量,其中误差显示在图8中的841处。是列向量,每个表示帧中相应变量的时间序列值。901处生成的c

xx

和c

ex

的逆矩阵的乘积提供了权重与最佳解

的偏差的估计值因此对于模拟抵消,非线性相位误差不可用于确定互相关向量c

ex

。相反,被分布并且作为输入存在于图8中的加法器806和814。因此,在图9中,其输入是的加法器902实际上分布在图8的实施例中的三个地方:即,到加法器806和814,以及δ

‑

∑调制器819。非线性相位误差是x1、x2、x3、x4和x5的线性组合,其中代替误差用于确定与的偏差。当时,误差时,误差最小,其中,是一个向量,其元素为α,β,γ,δ和∈。与的偏差通过在框901中生成的c

xx

和c

ex

的逆矩阵的乘积来估计。自适应回路作用于与的偏差,并将该偏差驱动为零。这是通过图9中的累加器905对该偏差进行积分并让累加器输出控制h个权重来实现的。自适应回路中的增益项k 903用于权衡自适应回路的噪声和带宽。累加器的输出将收敛到所需的系数或权重值h1‑

h5,导致x1‑

x5与误差信号之间的相关性为零。因此,收敛导致c

xx

‑1和c

ex

的乘积为零。累加器905中的累加值然后将保持正确的h1‑

h5值以有效地调整反馈时钟信号的周期以匹配参考时钟信号的周期并消除噪声项,包括rc相位检测器中的非线性效应。随着环境变化(例如电压或温度的变化),非零相关性将再次发生,并且系数值h1‑

h5将通过自适应回路进行调整,直到零相关性返回。

49.在一个实施例中,通过使用高斯赛德尔算法迭代地找到协方差矩阵(c

xx

‑1)的逆矩阵与c

ex

的乘积。图10说明了对的求解,即与的偏差。权重由c

xx

‑1c

ex

确定,并且使用高斯赛德尔迭代迭代地进行矩阵求逆。步骤包括(1)缩放c

xx

和c

ex

,使得c

xx

具有统一对角线;(2)将c

xx

拆分为单位对角线i、下矩阵l和上矩阵u,如图10所示,以及(3)对等式1001进行迭代。其他实施例使用替代算法进行矩阵求逆,例如jacobi或高斯消元法。图11a示出了协方差矩阵c

xx

,其中q是量化噪声。图11b示出了互相关向量c

ex

和协方差矩阵c

xx

。如图11b所示,因此c

ex

=c

xx

h,

50.在偶数边沿和奇数边沿上调整反馈分频器分频比降低了时间数字转换器(tdc)中相位检测器输入的反馈时钟信号与参考时钟信号之间的相位差。tdc包括时间电压转换器801、电容器dac 832和adc 805。为了减小相位差,参考时钟信号中的大周期变化与反馈时钟信号匹配。在实施例中,反馈时钟信号的版本被重新用作adc 805中的adc时钟和数字环路滤波器811中的主时钟。在一个实施例中,adc的增益与adc时钟的瞬时周期成正比因为它计算自上次采样以来的相变次数。这会在时间电压转换器中来自电容器dac的整形量化噪声(集中在高频)与周期变化(时钟频率一半的音调)之间产生混合作用。这种混合动作将一些量化噪声带入信号频带,从而降低了pll的整体相位噪声性能。如果数字时钟具有模拟参考时钟信号的周期变化,则会发生类似的现象。在从反馈时钟域到更高频率时钟的时钟域交叉处,在对vco时钟信号进行恒定分频时,偶数和奇数周期将保持不等量的时间,在某些情况下赋予一个权重。非恒定时钟方案可能还有其他动态影响。

51.为了减轻这种性能下降,反馈时钟信号的控制被调整为提供近似恒定的周期(在实现小数分频比的多模分频器的限制内),以用于adc时钟和数字时钟。那些特定时钟是作为示例,并且其他实施例可能想要使用具有近似恒定周期的其他内部时钟信号。这是可能

的,因为实施例利用四倍于参考时钟信号的频率的反馈时钟信号。4x反馈时钟信号用于在tdc内部生成时钟,用于其开关电容器操作、相位检测和adc时钟。使用4x反馈时钟信号的tdc的一个示例可以在美国专利第9,762,250号中找到,其发表于2017年9月12日,标题为“cancellation of spurious tones within a phase

‑

locked loop with a time

‑

to

‑

digital converter”,任命michael h.perrot为发明人。图12说明了一个实施例,其中存在控制反馈分频器信号1204的四个子相位(enable<0>,enable<1>,enable<2>,enable<3>)的持续时间的四个单独的分频比(div_code_0,div_code_1,div_code_2,div_code_3)。使能逻辑<3:0>选择由多路复用器1201提供给反馈分频器1203的特定分频代码。反馈分频器1203提供具有四倍于参考时钟速率的频率的反馈时钟信号1204。以4x速率计时的两位计数器1205可用于产生与四相时钟的每一相相对应的分频选择值和使能信号。使用图12所示的结构允许子相位有利地用于提供具有与参考时钟信号匹配的可变周期的反馈信号,并且还提供一个或多个具有基本恒定周期的时钟信号供pll内部使用。

52.图13a和图13b示出了,随着四个子相位的可用性,相位检测器看到的反馈时钟信号的分频周期可以不同于数字时钟信号和adc时钟信号的分频周期。这允许对各种子相位进行动态控制,以保持数字和adc时钟恒定,同时仍然跟踪参考时钟信号的周期变化,该信号来自倍频之前f1x时钟中的占空比误差。该控制概念在图13a和图13b中示出。图13a示出了反馈分频器信号的四个时钟子相位enable<0>、enable<1>、enable<2>以及enable<3>。如1303和1305处的水平箭头所示,enable<0>和enable<1>之间的边界发生变化,使得enable<0>相位的长度变长,enable<1>相位的长度变短,或者使得enable<1>相位的长度变长,enable<0>相位的长度变短,这取决于它是反馈时钟信号的奇数还是偶数周期。这允许通过与不同子相位相关联的边界生成内部时钟,从而允许某些内部时钟具有基本恒定的周期,该周期不反映与参考时钟信号相关的周期误差,并允许相位和频率检测器看到的反馈时钟信号与参考时钟信号的周期误差相匹配。

53.参考图13b,示出了三个时钟信号的周期:相位检测器看到的t[k]、环路滤波器数字逻辑使用的t_dig[k]和adc使用的t_adc[k]。在图13b的实施例中,通过使得对应于从enable0到enable1的转换的边沿1307在偶数和奇数周期上改变,仅enable<0>和enable<1>的长度改变,因为该转换对应于仅在tdc中的相位检测器处看到边沿。相位检测器将enable<0>的下降沿(或enable<1>的上升沿)视为反馈时钟信号的有效边沿。因此,例如,相位检测器将enable<1>的上升沿(有效边沿)与参考时钟信号的上升沿(有效边沿)进行比较。在这样的实施例中,相位和频率检测器忽略两个信号的下降沿(无效边沿)。通过配置四个分频比,使得子相位enable<0>和enable<1>的持续时间足够长以适应预期的占空比引起的周期变化,子相位之一的持续时间可以与另一个子相位进行权衡,以保持t_adc[k]和t_dig[k]的周期恒定,同时仍然调整相位检测器边沿和t[k]的周期长度。因此,短t[k]周期之后是长t[k 1]周期,然后是短t[k 2]周期。周期的长度由enable<0>和enable<1>之间的转换位置决定。相比之下,t_dig[k]、t_dig[k 1]和t_dig[k 2]的长度基本恒定并且由enable<3>和enable<0>之间的转换决定。类似地,t_adc[k]和t_adc[k 1]以及t_adc[k 2]的长度基本恒定并且由enable<1>和enable<2>之间的转换决定。

[0054]

因此,可以生成具有随参考时钟信号周期误差而变化的周期误差的反馈时钟信号,并且不跟踪基于子相位的周期误差的其他时钟信号可以被pll中的其他电路使用。请记

住,每个子相位的长度由反馈分频器使用的分频值决定。因此,对于较长的子相位,反馈分频器在发出边沿之前对应较长子相位的长度计数较长的时间,对于较短的子相位,反馈分频器在发出边沿之前对应于短相位边沿计数。在示出的实施例中,除了enable<0>和enable<1>之外的其他子相位的长度保持不变。

[0055]

图14示出了反馈分频器控制电路的高级框图,以实现图13a和图13b中所示的时序并提供使反馈时钟信号具有与参考时钟信号基本相同的周期误差的分频值。请注意,由于电路的限制、舍入误差和环境变化,相位和频率检测器看到的反馈时钟信号与参考时钟信号的周期误差不会完全相同。此外,δ

‑

∑调制器可以改变反馈时钟信号的周期以实现期望的小数分频值。因此,在此描述的各个实施例中的相位和频率检测器看到的反馈时钟信号的周期误差基本上等于参考时钟信号的周期误差但不相同。分频器电路1401接收反馈分频器的标称分频值n.f并将标称分频值分成对应于四个子相位的四个分频值:div_val_0、div_val_1、div_val_2和div_val_3。对应于h5x5(图8中的822)的duty_cycle_adjust[k]信号1402,通过调整div_code_0[k]和div_code_3[k]来调整相位检测器处的偶数/奇数周期变化,其是反馈分频器时钟信号的两个子相位的分频器值。div_code_3[k]信号控制enable<0>子相位,div_code_0[k]信号控制enable<1>子相位。第四个分频比div_code_1是常数,图14中未示出。图14所示电路在1403处对duty_cycle_adjust[k]进行四舍五入并除以2以生成dca_half_int[k]。将dca_half_int[k]乘以(1)生成dca3[k]并将dca3[k]1405添加到加法器1407中的divout3_nom的标称值,生成div_code_3[k]。请注意,divout3_nom对应于由偏移量调整的来自分路器1401的div_val_3,而divout0_nom对应于由偏移量调整的div_val_0。在一个实施例中,偏移量和标称值被选择为使得div_code_2和div_code_1的值尽可能最小并且允许分频比的其余部分在div_code_3和div_code_0之间拆分以用于最大范围的占空比校正。

[0056]

将dca_half_int[k]乘以(

‑

1)产生dca0[k]1406并且将dca0[k]添加到加法器1409中的标称值divout0_nom产生div_code_0[k]。由于duty_cycle_adjusts[k]1401每个周期由正变为负,因此div_code_3[k]和div_code_0[k]在参考时钟信号的每个周期交替反向加长和缩短。加法器1415将duty_cycle_adjust[k]值1402和来自偏移寄存器1416的偏移值相加。在延迟块1412中dca0[k]的延迟之后,两个dca_half_int[k]值在加法器1411中组合以对准这些值,因此它们不会抵消,然后在加法器1415中从duty_cycle_adjust[k](和偏移值)中减去(乘以(

‑

1)并求和)。该减法表示舍入后剩余的占空比调整值(舍入误差),并且加法器1418将舍入误差与具有分频代码div_val_2 1417的偏移量相结合。偏移量设置div_code_2[k]的标称分频比,例如使与div_code_2[k]相关的相位更短。在一个实施例中,偏移量和标称值被编程为使得div_code_1(图14中未示出)和div_code_2[k]是由最大操作频率设置的可能的最小值。其余的分频比在divout0_nom和divout3_nom之间平均分配,以实现最大占空比校正范围。在其他实施例中,div_code_2和div_code_1,即使不是最小值,也至少足够小以允许div_code_3[k]和div_code_0[k]变化到足以反映参考时钟信号的周期误差。注意,尽管反馈分频器接收定义四个子相位的分频器值,但在所示的实施例中,仅div_val_2在通过偏移和舍入误差调整后被提供给多级噪声整形(mash)δ

‑

∑调制器1419,它对应于图8中的δ

‑

∑调制器819。在不需要为t_adc[k]和t_dig[k]提供恒定周期的实施例中,仅控制div_val_2[k],并且dsm的输入是div_val_2[k] duty_cycle_adjust[k]。请注意,反

馈分频器提供的反馈信号与vco的输出边沿对准。

[0057]

图15示出了另一个实施例,其中在δ

‑

∑调制器之后生成四个子相位。加法器1501将反馈分频值n.f 1502与抖动信号1503和相位调整信号h5x

5 1505组合,并将结果提供给δ

‑

∑调制器1507。分路器1509将来自δ

‑

∑调制器的输出n[k]分成四个分频器值d0[k]、d1、d2和d3,其中n[k]=d0[k] d1 d2 d3。注意,在所示实施例中,d1、d2和d3是恒定的,而d0[k]结合了由δ

‑

∑调制器1507做出的改变以实现小数分频。乘法器1511接收奇数/偶数指示1515(0.5

×

[h5/mfs]),其中mfs是dsm量化步长,并产生占空比调整值“x”。然后调整d2和d3的值以表示周期误差:

[0058]

n[k]=d0[k] d1 (d2 x) (d3‑

x);k=odd。

[0059]

n[k]=d0[k] d1 (d2‑

x) (d3 x);k=even。

[0060]

假设相位检测器看到由分频器值d2和d3定义的子相位之间的边界。在其他实施例中,分路器调整d3和d0(或任何两个子相位)以进行周期误差校正,并且将δ

‑

∑调制器变化合并为d2和/或d1以实现小数分频。

[0061]

为了更好地理解使用多相位反馈分频器来校正周期误差,图16至图19使用了示例数字。请注意,图16至图19未按比例绘制。参考图16,假设参考时钟信号具有理想的50%占空比。相位检测器边沿将en0和en1之间的转换视为定义反馈时钟信号周期,adc将en1和en2之间的转换视为定义adc时钟周期。在没有周期误差的情况下,adc时钟和相位检测器时钟都有一个由4个50vco周期组成的200vco周期。图17说明当反馈时钟信号被调整以匹配参考时钟信号的周期误差但没有对反馈时钟信号产生的其他时钟进行周期补偿时,pd时钟在230vco周期的1701处有一个长周期,在170vco周期的1703处有一个短周期。在没有补偿的情况下,adc时钟还分别在1705处和1707处看到230vco周期和170vco周期的长周期和短周期。如前所述,adc的长周期和短周期会在pll中引起不希望有的噪声。

[0062]

图18示出了adc时钟的周期补偿方案的结果。在图18的实施例中,需要补偿的周期误差的值从自适应算法导出,并且非常缓慢地变化以跟踪跨温度的周期误差变化(例如跟踪带宽~20hz)。因此,出于图17至图19的目的,假设周期误差是准静态的。相位检测器时钟信号的周期由en0和en1之间的转换定义。请注意,en0

‑

en3对应于子相位enable<0>到enable<3>。adc时钟信号的周期由en1和en2之间的转换定义。相位检测器时钟信号在1801处的长周期为230,在1803处的短周期为170。通过使用如图14和图15所示的电路进行补偿,adc时钟在1805和1807处保持200个单位周期。图19示出了通过使子相位en2和en3比图18的实施例中更短的具有更大校正范围的周期误差补偿。具体而言,在所示示例中,en2和en3仅是10个单位,而en0和en1利用在105和75之间变化的180个单位。

[0063]

由大周期误差引起的另一个问题发生在启动时(或每当pll试图获取锁定时)。在存在大的占空比引起的周期变化的情况下,pll可能难以锁定。为了解决这个问题,在实施例中,pll最初锁定参考时钟信号的偶数或奇数周期的一组边沿,以通过对提供给相位检测器的样本进行下采样来隐藏锁定过程中的周期变化。一旦实现锁定并且粗量化噪声消除(qnc)适应完成(特别是h5收敛),环路滤波器将停止下采样以全速率运行并实现所需的性能。图20示出了为实现锁定序列而进行的排序的实施例的高级流程图。在2001处,pll控制禁用自适应并在初始化状态中等待,同时pll被配置为在2003处锁定到参考时钟信号的奇数时钟边沿或偶数时钟边沿。pll继续尝试实现锁定,直到失锁(lol)检测器表明在2005处

实现频率锁定。然后在2007处,pll进入等待状态以等待一段定义的时间,从而允许附加的pll稳定。在一个实施例中,一旦实现锁定,并且在等待期之后,自适应步骤提供自适应以确定h5。在锁定和第一次自适应期间,相位和频率检测器以及环路滤波器被下采样,因此只能观察到偶数边沿或奇数边沿。请注意,在初始锁定期间,可以使用粗略的相位和频率检测器。一旦实现锁定并且适应已经收敛,pll可以返回到在参考时钟信号的两个边沿上的锁定,并且自适应回路继续运行以更新h5。

[0064]

如图21所示,在一个实施例中,粗相位检测器基本上使用4x速率反馈分频器时钟信号量化参考时钟信号。如果参考时钟在enable3或enable0期间到达,则认为参考时钟信号较早,tdc输出反映参考时钟较早。如果参考时钟在enable2期间到达,那么它较晚。如果它在enable1期间到达,则认为参考时钟信号是及时的。粗频率检测器接收下采样信号。与粗相位检测器相关联的控制逻辑还寻找相位在早和晚之间直接回绕的情况,从而在发生这种回绕时导致更大的频率误差校正。环路滤波器的下采样发生在量化噪声消除信号处理之后,因此仍然可以基于偶数和奇数周期进行自适应以校正占空比,但在控制到达vco之前。粗pfd和环路滤波器的下采样控制保持同步,因此它们都可以查看偶数边沿或奇数边沿,但不会出现失配。在至少一个实施例中,是锁定到偶数参考时钟周期还是奇数参考时钟周期是任意的并且不受控制。

[0065]

因此,已经描述了各种方法来解决参考时钟信号中的周期误差。此处阐述的本发明的描述是说明性的,并不旨在限制如以下权利要求中阐述的本发明的范围。在不脱离所附权利要求中阐述的本发明的范围的情况下,可以基于在此阐述的描述对本文公开的实施例进行其他变化和修改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。