用于控制阻变随机存取存储器器件中的形成电压的方法

1.相关申请的交叉引用

2.本技术要求于2019年5月31日提交的标题为“method for controlling the forming voltage in resistive random access memory devices”“用于控制阻变随机存取存储器器件中的形成电压的方法”的美国专利申请号16/428,554的优先权,该申请的全文通过引用并入本文。

技术领域

3.本发明涉及半导体处理和半导体器件、并且更特别地涉及阻变随机存取存储器(reram)器件及制造方法。

背景技术:

4.reram器件是一类储存存储器器件,其由于对于高密度/低成本/低功耗非易失性存储器的潜在付出(potential payout)而备受关注。reram器件背后的基本思想为使通常绝缘的介电薄膜可以通过细丝或传导通路(在该厚度薄膜上施加足够高的电压(称为形成电压)后形成)来传导电流。传导通路可以由不同机制产生,包括空位或金属缺陷迁移。一般来说,形成电压随着介电薄膜的厚度的减少而线性递减,但是在不改变介电薄膜厚度的情况下很难调节形成电压。另外,改变介电薄膜厚度可能会导致其他的器件性能问题,或需要转变成不同的介电材料。因此,需要不显著影响介电薄膜的厚度而调节形成电压的方法。

技术实现要素:

5.本发明的实施例提供了一种通过介电薄膜的后沉积处理来控制介电薄膜的形成电压的方法。例如,该介电薄膜可以形成reram器件的一部分。

6.根据一个实施例,形成reram器件的方法包括:在基板上沉积含有本征缺陷的介电薄膜,形成等离子体激发的含h2气的处理气体,以及将该介电薄膜暴露于该等离子体激发的处理气体中以在该介电薄膜中产生附加缺陷而不会显著改变该介电薄膜的物理厚度,其中该附加缺陷降低了在该介电薄膜上产生导电细丝所需的形成电压。在一个实例中,介电薄膜包含金属氧化物介电薄膜并且暴露包括使用微波等离子体源来激发处理气体。在一些实例中,处理气体由h2气、或h2气和ar气组成。

7.根据另一个实施例,描述了包括含有本征缺陷和附加缺陷的介电薄膜的reram器件,该附加缺陷是将该介电薄膜暴露于等离子体激发的含h2气的处理气体中产生的,其中该介电薄膜中产生该附加缺陷而不会显著改变该介电薄膜的物理厚度,并且其中该附加缺陷降低了在该介电薄膜上产生导电细丝所需的形成电压。在一个实例中,介电薄膜包括可以选自由以下各项组成的组的金属氧化物薄膜:hfo2、zro2、tio2、nio、al2o3、ta2o5、及其叠层膜。

附图说明

8.结合在此说明书中并且构成其一部分的附图展示了本发明的实施例,并且连同以上给出的本发明的总体描述以及以下给出的详细描述来解释本发明。

9.图1a和图1b示意性地示出了根据本发明的一个实施例的一种用于控制薄膜结构的形成电压的方法;

10.图2a至图2c示意性地示出了根据本发明的另一实施例的一种用于控制薄膜结构的形成电压的方法;

11.图3a和图3b示出了根据本发明的实施例的reram器件的形成步骤、复位(reset)步骤、和置位(set)步骤;

12.图4示出了根据本发明的实施例的在面积为10

×

10微米的金属

‑

绝缘体

‑

金属电容器中的被等离子体处理改性的hfo2介电薄膜的测量形成电压;

13.图5至图7是含rlsa

tm

等离子体源的微波等离子体处理系统的示意图;

14.图8示出了微波等离子体处理系统的电子温度对间隙距离;以及

15.图9示出了微波等离子体处理系统的电子密度对间隙距离。

具体实施方式

16.本发明的实施例提供了一种通过介电薄膜的后沉积处理来控制介电薄膜的形成电压的方法。例如,介电薄膜可以形成reram器件的一部分,reram器件包括第一电极薄膜(如tin)、介电薄膜和第二电极薄膜(如tin)的叠层膜。后沉积处理包括对介电薄膜进行等离子体处理,其中等离子体处理提供高度可控的形成电压的控制而不显著减少介电薄膜的厚度或改变其它重要的介电参数。在reram器件中,通过介电薄膜中传导细丝的形成和消失来控制阻变。对于金属氧化物介电薄膜而言,其阻变机制归因于充当局部掺杂物的带电氧空位的位移。

17.根据一个实施例,描述了形成reram器件的方法,其中该方法包括:在基板上沉积含有本征缺陷的介电薄膜,形成等离子体激发的含h2气的处理气体,以及将该介电薄膜暴露于该等离子体激发的处理气体中以在该介电薄膜中产生附加缺陷,其中该附加缺陷降低了在该介电薄膜上产生导电细丝所需的形成电压。

18.根据另一个实施例,该方法包括:在基板上沉积含有本征缺陷的介电薄膜,形成等离子体激发的含h2气的处理气体,将该介电薄膜暴露于该等离子体激发的处理气体中以在该介电薄膜中产生附加缺陷,以及在该介电薄膜上施加形成电压以产生导电细丝。

19.图1a和图1b示意性地示出了根据本发明的一个实施例的一种用于控制薄膜结构的形成电压的方法。图1a示出了包括基板100和在基板100上的介电薄膜102的薄膜结构1。基板100可以包括在基底材料(如层间介电薄膜)上的第一电极薄膜(如tin)。介电薄膜102可以通过气相沉积(如原子层沉积(ald))或化学气相沉积(cvd)沉积而来。介电薄膜102含有本征缺陷104(也称作非化学计量缺陷),在介电薄膜102的沉积或形成过程中形成的离子位错和/或离子空位可以引起该缺陷。在一个实例中,沉积态的金属氧化物介电薄膜可以包括例如氧空位、氧位错、或这二者的本征缺陷。例如,介电薄膜102可以包括选自由以下各项组成的组的金属氧化物薄膜:hfo2、zro2、tio2、nio、al2o3、ta2o5、及其叠层膜。在一些实例中,介电薄膜102的厚度可以在约2nm和约20nm之间、在约2nm和约10nm之间、在约2nm和约

5nm之间、在约5nm和约20nm之间、或在约10nm和约20nm之间。

20.图1b示出了气态暴露于等离子体激发的处理气体中的薄膜结构1。在一些实例中,处理气体106可以含有或由h2气、或h2气和惰性气体(如ar)组成。等离子体暴露将附加缺陷108引入到介电薄膜102中而不显著改变介电薄膜102的物理厚度。所产生的介电薄膜102含有本征缺陷104和附加缺陷108。另外,当仅使用h2气、或h2气和ar气时,仅有h2(或h)、或h2(或h)和ar被等离子体暴露引入到介电薄膜102中。等离子体暴露和形成电压的降低是高度可控的并且处理条件(如等离子体源功率、暴露时间、和基板温度)可以选择,如此引入到介电薄膜102中的附加缺陷108的数量是可控的。根据一个实施例,微波等离子体源可以用于等离子体激发。图5至图7描述了示例性的微波等离子体源。微波等离子体源产生具有低电子温度和高电子密度的等离子体来有效地将附加缺陷108引入到介电薄膜102中而不显著改变介电薄膜102的厚度或对介电薄膜102造成严重破坏。因而微波等离子体非常适合高度可控地将附加缺陷108引入到介电薄膜102中。根据另一个实施例,电容耦合等离子体(ccp)源或电感耦合等离子体(icp)源可以用于等离子体激发。

21.在一些实例中,介电薄膜102的等离子体暴露可以在基板温度为约200℃或更高时进行,如在约200℃和约500℃之间、在约200℃和约300℃之间、在约300℃和约400℃之间、在约300℃和约500℃之间、在约400℃和约500℃之间。在一个实例中,基板温度可以是约400℃。

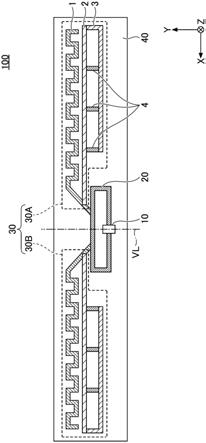

22.根据一个实施例,在等离子体暴露过程中,处理条件可以包括基板温度为约400℃,处理室压力为约0.95托,以及微波功率为约1700w。

23.根据一个实施例,介电薄膜的沉积和后沉积处理可以通过这样进行:至少中断一次介电薄膜的沉积并且在继续介电薄膜的沉积之前进行等离子体暴露。这在图2a至图2c中示意性地示出。

24.图2a至图2c示意性地示出了根据本发明的一个实施例的一种用于控制薄膜结构的形成电压的方法。薄膜结构2与图1a中的薄膜结构1类似,并且包括基板200和沉积在或形成在基板200上的介电薄膜202。基板200可以包括在基底材料(如层间介电薄膜)上的第一电极薄膜(如tin)。介电薄膜202可以比图1a中的介电薄膜102更薄,并且含有本征缺陷204。例如,介电薄膜202可以包括选自由以下各项组成的组的高k金属氧化物:hfo2、zro2、tio2、nio、al2o3、ta2o5、及其叠层膜。在一些实例中,介电薄膜202的厚度可以在约1nm和约10nm之间、在约2nm和约10nm之间、在约2nm和约5nm之间、在约5nm和约10nm之间、或在约5nm和约20nm之间。

25.图2b示出了气态暴露于等离子体激发的处理气体206中的薄膜结构2。在一些实例中,处理气体206可以含有或由h2气、或h2气和惰性气体(如ar)组成。等离子体暴露将附加缺陷208引入到介电薄膜202中而不显著改变介电薄膜202的物理厚度。所产生的介电薄膜202含有本征缺陷204和附加缺陷208。另外,当仅使用h2气、或h2气和ar气时,仅h2(或h)、或h2(或h)和ar通过等离子体暴露引入到介电薄膜102中。等离子体暴露和形成电压的降低是高度可控的并且处理条件(如等离子体源功率、暴露时间、和基板温度)可以进行选择,使得引入到介电薄膜202中可控数量的附加缺陷208。根据一个实施例,微波等离子体源可以用于等离子体激发。根据另一个实施例,ccp源或icp源可以用于等离子体激发。

26.图2c示出了将附加的介电薄膜210沉积在介电薄膜202上之后的薄膜结构2,其中

附加的介电薄膜210含有本征缺陷212。在一个实例中,附加的介电薄膜210可以含有与介电薄膜202相似的介电材料。在另一个实例中,附加的介电薄膜210可以含有与介电薄膜202不同的介电材料。根据一个实施例,在附加的介电薄膜210上进行的附加的等离子体暴露在附加的介电薄膜210中引入另外的附加缺陷。

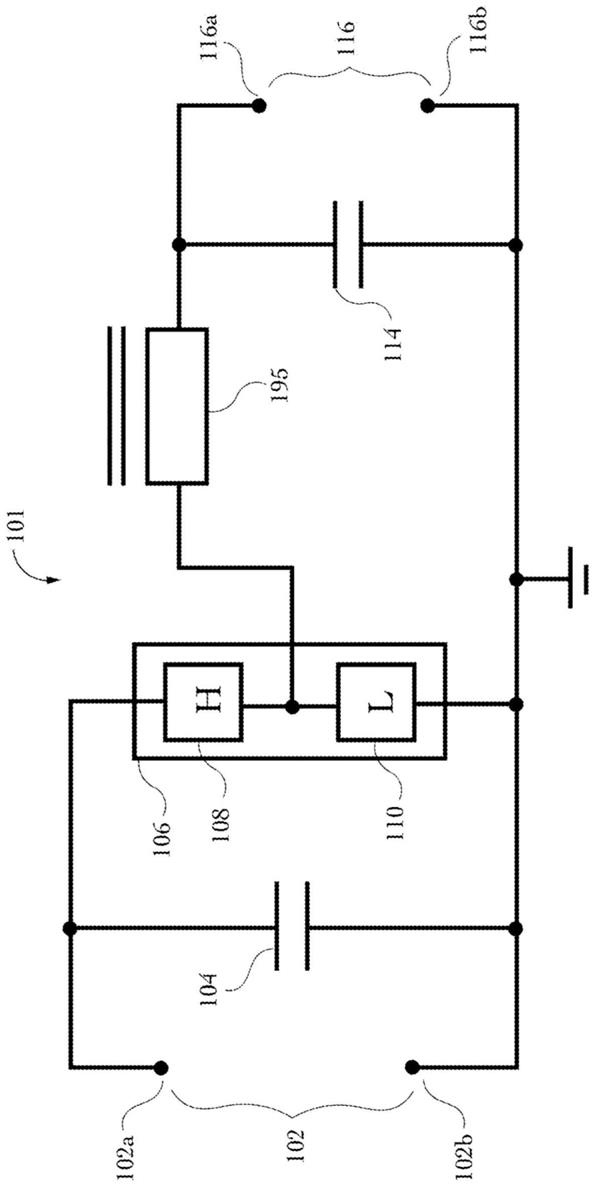

27.图3a和图3b示出了根据本发明的实施例的reram器件的形成步骤、复位步骤和置位步骤。图3a示出了在reram器件的介电薄膜中形成导电细丝的实验结果。在形成步骤中,通过reram堆栈的初始泄露电流较低,但是随着介电薄膜上施加的偏压增大,泄露电流突然增加。泄露电流达到了由外部器件(如晶体管)设定的顺应电流。在图3a的实例中,顺应电流为约100μa。

28.图3b示出了reram器件的复位步骤和置位步骤的实验结果。在图3a的形成步骤中,形成了导电细丝并且器件被转换为低阻态。在朝向极性相反的后续电压扫描期间,在特定阈值电压处发生向高阻态的转变,如图3b所示。此操作被称为复位并且其破坏了细丝。然后,通过扫描朝向极性相反的电压,器件阻态从复位转换为低阻态。此操作被称为置位。置位步骤中所需的施加偏压小于形成步骤中所需的施加偏压,这是因为置位步骤不需要产生整个细丝,只需重新建立连接。

29.图4示出了根据本发明的实施例的被等离子体处理改性的hfo2介电薄膜的测量形成电压。所有的hfo2介电薄膜的厚度为约5nm并且金属

‑

绝缘体

‑

金属电容器的面积是10

×

10微米。对于hfo2介电薄膜而言,当氧空位在hfo2介电薄膜上排成一行时,本征缺陷和通过后沉积处理引入的附加缺陷形成传导细丝并且形成电压受到本征缺陷和附加缺陷总数量的强烈影响。

30.在图4中,hfo2介电薄膜102、104、106、和108被如图1a和图1b中所描述的方法处理,并且hfo2介电薄膜101和103被如图2a至图2c中所描述的方法处理。在热ald处理中使用hf(netme)4和h2o的交替气体暴露在约300℃的基板温度下沉积hfo2介电薄膜。

31.hfo2介电薄膜100是没有进行后沉积处理的沉积态的参考样品并且其测量形成电压为约3.4v。hfo2介电薄膜102至108被暴露于微波等离子体激发的由h2气和ar气组成的处理气体中。hfo2介电薄膜102、104、106、和108的等离子体暴露分别进行30sec、40sec、50sec、和60sec。hfo2介电薄膜102至108的测量形成电压从约3.1v至约2.85v单调递减。

32.通过在基板上沉积4nm的第一hfo2介电薄膜,将该第一hfo2介电薄膜在微波等离子体激发的由h2气和ar气组成的处理气体中暴露30sec以及,之后在该第一hfo2介电薄膜上沉积附加的1nm的第二hfo2介电薄膜来制备hfo2介电薄膜101。通过在基板上沉积2nm的第一hfo2介电薄膜,将该第一介电hfo2材料在微波等离子体激发的由h2气和ar气组成的处理气体中暴露30sec以及,之后在该第一hfo2介电薄膜上沉积附加的3nm的第二hfo2介电薄膜来制备hfo2介电薄膜103。在等离子体处理和沉积第二hfo2介电薄膜后,hfo2介电薄膜101和103的测量形成电压分别为约3.0v和约2.8v。

33.图4的实验结果示出了使用在30sec和60sec之间的等离子体暴露,5nm厚的hfo2介电薄膜的形成电压可控地从约3.4v降低到约2.8v。另外,当第一hfo2介电薄膜达到初始厚度时中断hfo2介电材料的沉积,对第一hfo2介电薄膜进行等离子体暴露,以及沉积第二hfo2介电薄膜直至达到期望的厚度(即5nm)更有效地降低了形成电压。观察得知,第一hfo2介电薄膜的厚度越薄,形成电压越能有效地被降低。

34.与参考样本相比,等离子体处理的hfo2介电薄膜的二次离子质谱(sims)深度剖特征(profile)出了氢(h)浓度的明显增加。

35.在等离子体处理中基板温度的影响显示基板温度在高于约300℃时比温度等于或小于约300℃时更有效地降低了hfo2介电薄膜的形成电压。例如,基板温度为约350℃时比基板温度为约300℃时更有效,以及基板温度为约400℃时比基板温度为约350℃时更有效。

36.图5至图7是含rlsa

tm

等离子体源的微波等离子体处理系统(可从东京电子有限公司,赤坂,日本获得)的示意图。如图5所示,等离子体处理系统10包括等离子体处理室20(真空室)、天线单元50、和基板支架21。在等离子体处理室20内部大致分为位于等离子体气体供应单元30之下的等离子体产生区ri、和位于基板支架21之上的等离子体扩散区r2。等离子体产生区r1中产生的等离子体的电子温度可以为几电子伏特(ev)。当等离子体被扩散至等离子体扩散区r2(在那里进行薄膜处理)时,靠近基板支架21的等离子体的电子温度可能下降到在约1ev和约2ev之间的值。图8示出了这个低的电子温度是处理气体供应单元40与基板支架21之间的间隙距离的函数。此外,如图9所示,在间隙距离小于约70mm时,等离子体扩散区r2中的电子密度大于约1.0e 12cm

‑1。

37.基板支架21位于等离子体处理室20的底部中央并且作为基板支架来支撑基板w。在基板支架21内部,提供了绝缘构件21a、冷却套21b、和用于控制基板温度的温度控制单元(未示出)。

38.等离子体处理室20的顶部是开放式的。等离子体气体供应单元30相对于基板支架21放置并且经由密封构件如o形环(未示出)与等离子体处理室20的顶部附接。等离子体气体供应单元30(也可以用作介电窗)可以由氧化铝或石英材料制成并且具有平坦表面。在等离子体气体供应单元30的平坦表面上设置了多个与基板支架21相对的气体供应孔31。多个气体供应孔31通过气流通道32与等离子体气体供应口33连通。等离子体气体供应源34提供等离子体气体(如ar气、h2气、或ar和h2二者、或其他气体)至等离子体气体供应口33。等离子体气体然后经由多个气体供应孔31均匀地被提供至等离子体产生区r1。

39.等离子体处理系统10进一步包括处理气体供应单元40,其位于等离子体处理室20的等离子体产生区r1和等离子体扩散区r2之间的中央位置。处理气体供应单元40可以由导电材料(例如包括镁(mg)的铝合金或不锈钢)制成。与等离子体气体供应单元30类似,多个气体供应孔41设置在处理气体供应单元40的平坦表面上。处理气体供应单元40的平坦表面与基板支架21相对。

40.等离子体处理室20进一步包括与等离子体处理室20的底部相连接的排气管路26、将排气管路26与压力控制阀28和真空泵29相连接的真空管路27。压力控制阀28可以用来实现等离子体处理室20中期望的气体压力。

41.图6示出了处理气体供应单元40的俯视图。如此图中所示,处理气体供应单元40中形成了网格状的气流通道42。网格状的气流通道42与在竖直方向上形成的多个气体供应孔41的上端连通。多个气体供应孔41的下部是面向基板支架21的开口。多个气体供应孔41经由网格状的气流通道42与处理气体供应口43连通。

42.另外,处理气体供应单元40中形成了多个开口44,使得该多个开口44在竖方向上穿过处理气体供应单元40。多个开口44将等离子体气体(如ar、h2、或其他气体)引入到基板支架21上的等离子体扩散区r2。如图6所示,多个开口44在相邻的气流通道42之间形成。处

理气体可以从三个独立的处理气体供应源45至47供应至处理气体供应口43。处理气体供应源45至47可以供应h2气、n2气、和ar气。

43.处理气体流过网格状的气流通道42并且经由多个气体供应孔41被均匀地供应至等离子体扩散区r2。等离子体处理系统10进一步包括四个阀(v1

‑

v4)和四个用于控制处理气体供应的质量流量控制器(mfc1

‑

mfc4)。

44.外部微波发生器55经由同轴波导54将预定频率的微波提供给天线单元50。同轴波导54可以包括内部导体54b和外部导体54a。来自微波发生器55的微波在等离子体产生区ri中的等离子体气体供应单元30的正下方产生电场,这继而引起等离子体处理室20内的处理气体的激发。例如,微波功率可以在约0.5w/cm2和约4w/cm2之间。替代地,微波功率可以在约0.5w/cm2和约3w/cm2之间。微波辐射包含的微波频率可以是约300mhz至约10ghz,例如2.45ghz。

45.图7展示了天线单元50的局部截面图。如此图所示,天线单元50可以包括平面天线主体51、辐射线槽板52、和缩短微波波长的介电板53。平面天线主体51可以是具有开放式底面的圆形。平面天线主体51和辐射线槽板52可以由导电材料制成。

46.多个槽56设置在辐射线槽板52上来产生圆极化波。多个槽56以大致呈t形的形式排列,其中每个槽之间具有小的间隙。多个槽56沿圆周方向排列成同心圆图案或螺旋图案。由于槽56a和56b互相垂直,所以包含两个正交极化分量的圆极化波作为平面波从辐射线槽板52辐射。

47.位于辐射线槽板52和平面天线主体51之间的介电板53可以由低损耗的介电薄膜(如氧化铝(al2o3)或氮化硅(si3n4))制成。可以使用密封构件(未示出)将辐射线槽板52安装在等离子体处理室20上,如此使辐射线槽板52与盖板23紧密接触。盖板23位于等离子体气体供应单元30的上表面上并且由微波透射介电薄膜(例如氧化铝(al2o3))形成。

48.外部高频电源22经由匹配网络25电连接到基板支架21。外部高频电源22产生预定频率(如13.56mhz)的rf偏压功率,用于控制等离子体中被吸引到基板w的离子的能量。电源22进一步被配置为可选地提供rf偏压功率的脉冲。脉冲频率可以高于1hz、例如2hz、4hz、6hz、8hz、10hz、20hz、30hz、50hz、或更高。电源22被配置为提供在0w和100w之间、在100w和200w之间、在200w和300w之间、在300w和400w之间、或在400w和500w之间的rf偏压功率。本领域技术人员将理解电源22的功率电平与被处理的基板的大小相关。例如,在处理过程中,300mm的si晶片需要比200mm的晶片更高的能耗。等离子体处理系统10进一步包括能为基板支架21供应在

‑

5kv和 5kv之间的dc偏压的dc电压发生器35。

49.已经描述了通过等离子体暴露于处理气体来控制reram器件的形成电压的多个实施例。为了说明和描述的目的,已经呈现了对本发明的实施例的前述描述。并不旨在穷举或将本发明限制于所披露的确切形式。本说明书和所附权利要求包括仅用于描述目的并且不应解释为进行限制的术语。相关领域的技术人员可以理解,根据以上教导,许多修改和变化是可能的。本领域技术人员将认识附图中示出的各种部件的各种等效组合和替代。因此,意图是本发明的范围不受该具体实施方式限制,而是由与其所附的权利要求限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。