1.本发明属于半导体芯片的设计技术领域,具体涉及一种低压带隙基准电压产生电路。

背景技术:

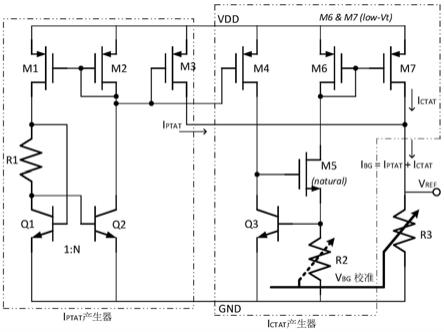

2.随着半导体芯片技术的发展进步和应用的不断拓宽,高性能、低成本的设计技术越来越重要。带隙基准电压是最基本、最重要的芯片模块。由它产生的基准电压具有很高的稳定性和精确度。如图1所示,高精度、低噪声的带隙电压或与其成比例的基准电压,是高精度的模数及数模转换器、电压检测、电源管理,等芯片和模块中必不可少的。

3.既有的适用于低电源电压的带隙基准电压产生器,如图2,基本上都需要一个误差放大器(ea:error amplifier)来实现反馈控制。放大器的输入失调,以及反馈环路的噪声放大、低带宽、频率补偿等问题,都时既有芯片设计方法的缺点和不足。另外,该电路不便产生正温度系数(ptat:proportional to absolute temperature))和负温度系数(ctat:complementary to absolute temperature)的电流输出。

技术实现要素:

4.本发明的目的在于提供一种低压带隙基准电压产生电路,以简洁的方式分别产生ptat和ctat电流,然后产生与带隙电压成比例的基准电压;而且,整个电路适合于低电源电压下工作,不需要误差放大器和频率补偿,大大简化了芯片设计,也减少了面积和功耗,可以解决上述背景技术中提出的问题。

5.为实现上述目的,本发明提供如下技术方案:一种低压带隙基准电压产生电路,该电路包括i

ptat

产生器、i

ptat

电流镜和i

ctat

产生器;

6.所述i

ptat

产生器,包括三极管q1、三极管q2、电阻r1、pmos管m1和m2,用于产生i

ptat

;

7.其中,电阻r1两端的电压差/三极管q1与q2的电压差为δv

be

,三极管q2和q1的尺寸比例为n,忽略基极电流,则流过q2和q1的电流相同;

8.所述i

ptat

电流镜,连接到所述i

ptat

产生器上,包括pmos管m1、m2、m3及m4,用于对ptat电流进行偏置,生成偏置电流;

9.所述i

ctat

产生器,连接到i

ptat

电流镜上,包括pmos管m4和m6、nmos管m5、三极管q3、以及电阻r2,用于产生i

ctat

。

10.优选地,所述v

be

为三极管的基极(base)和发射极(emitter)之间的压降具有负温度系数,电阻r1两端的电压差/三极管q1与q2的电压差为δv

be

具有正的温度系数。

11.优选地,所述电阻r1两端的电压差:

[0012][0013]

其中,k为玻尔兹曼常数,q为电子的电荷值常数,t为绝对温度,in(n)是n的自然对数,kt/q在常温下大约为26mv,v

be

为三极管的基极(base)和发射极(emitter)之间的压降;

[0014]

此时,和绝对温度成正比例的电流为:

[0015][0016]

和绝对温度成负比例的电流为:

[0017][0018]

让

[0019]

便得到叠加后的基本消除温度系数的带隙电流为:

[0020][0021]

最后,该电路产生的基准电压v

ref

,与带隙电压v

bg

成正比:

[0022][0023]

优选地,所述nmos管m5采用自然阈值的nmos管,pmos管m6与m7采用低阈值的pmos管。

[0024]

与现有技术相比,本发明的有益效果是:

[0025]

(1)本发明简化了低电源电压下带隙基准电压电路的设计,省去了反馈环路放大器及其频率补偿。

[0026]

(2)本发明消除了反馈放大器输入失调电压的问题。

[0027]

(3)本发明消除了反馈放大器额外的噪声和噪声放大的问题。

[0028]

(4)本发明提出了带隙基准电压温度漂移最小化的校正方法。

[0029]

(5)本发明的电路兼具输出ptat和ctat电流的便利。

[0030]

(6)本发明提高了芯片的性能和可靠性,也减少了面积和功耗。

附图说明

[0031]

图1是带隙基准电压在芯片的应用示意图;

[0032]

图2是传统的低压带隙基准电压产生电路;

[0033]

图3是本发明的低压带隙基准电压产生电路;

[0034]

图4是本发明的低压带隙基准电压在典型工艺下的仿真结果;

[0035]

图5是本发的基准电压在极端工艺角落无校正的仿真结果;

[0036]

图6是本发明的基准电压在极端工艺角落只校正r3的仿真结果;

[0037]

图7是本发明的基准电压在极端工艺角落同时校正r2与r3的仿真结果。

具体实施方式

[0038]

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0039]

如图3所示,一种低压带隙基准电压产生电路,该电路包括i

ptat

产生器、i

ptat

电流镜和i

ctat

产生器;

[0040]

所述i

ptat

产生器,包括三极管q1、三极管q2、电阻r1、pmos管m1和m2,用于产生i

ptat

;

[0041]

其中,电阻r1两端的电压差/三极管q1与q2的电压差为δv

be

,三极管q2和q1的尺寸比例为n,忽略基极电流,则流过q2和q1的电流相同;

[0042]

所述i

ptat

电流镜,连接到所述i

ptat

产生器上,包括pmos管m1、m2、m3及m4,用于对ptat电流进行偏置,生成偏置电流;

[0043]

所述i

ctat

产生器,连接到i

ptat

电流镜上,包括pmos管m4和m6、nmos管m5、三极管q3、以及电阻r2,用于产生i

ctat

。

[0044]

作为本发明的一个实施例,所述v

be

为三极管的基极(base)和发射极(emitter)之间的压降具有负温度系数,电阻r1两端的电压差/三极管q1与q2的电压差为δv

be

具有正的温度系数。

[0045]

作为本发明的一个实施例,所述电阻r1两端的电压差:

[0046][0047]

其中,k为玻尔兹曼常数,q为电子的电荷值常数,t为绝对温度,in(n)是n的自然对数,kt/q在常温下大约为26mv,v

be

为三极管的基极(base)和发射极(emitter)之间的压降;

[0048]

此时,和绝对温度成正比例的电流为:

[0049][0050]

和绝对温度成负比例的电流为:

[0051][0052]

让

[0053]

便得到叠加后的基本消除温度系数的带隙电流为:

[0054][0055]

最后,该电路产生的基准电压v

ref

,与带隙电压v

bg

成正比:

[0056][0057]

作为本发明的一个实施例,所述nmos管m5采用自然阈值的nmos管,pmos管m6与m7采用低阈值的pmos管。

[0058]

图4所示,输出的基准电压名义值约为614mv,从

‑

40℃到125℃温度范围内的电压变化小于0.6mv,即

±

0.05%。

[0059]

图5所示,考虑了三极管和电阻的工艺变化,输出基准电压的温度漂移范围小于23mv,约

±

2%。

[0060]

图6所示,在常温30℃下,通过校准电阻r2的阻值,使输出的基准电压vref达到名

义值614mv。校正后,输出基准电压的温度漂移范围大约4.8mv,小于

±

0.4%。

[0061]

图7所示,在常温30℃下,通过同时、同比例地校准电阻r2和r3,使输出的基准电压vref达到名义值6114mv。校正后,输出基准电压的温度漂移范围大约2.3mv,小于

±

0.2%。

[0062]

尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。