基于fpga的irig

‑

b直流码解码及对时自动切换方法

技术领域

1.本发明属于导航控制技术领域,尤其是基于fpga的irig

‑

b直流码解码及对时自动切换方法。

背景技术:

2.irig

‑

b直流码由于其相对简单的串行输入格式,携带丰富的编码信息,并且每秒一帧的格式符合时间的使用习惯已经成各个国家通用的时间同步标准。随着集成电路技术的不断发展,采用fpga芯片的解码电路具有电路器件少、成本低且准确度高等优点逐渐成为irig

‑

b直流码解码的主流趋势。

3.而如何保证各个设备之间时间的统一,需要对设备进行对时校正,保证设备的日常运行以及对时校正后的正常运行十分重要,而目前尚未出现针对此问题的解决方法。

技术实现要素:

4.本发明的目的在于克服现有技术的不足,提出基于fpga的irig

‑

b直流码解码及对时自动切换方法,能够在设定的时间基础上进行准确计时并能够在外界有校正对时时自动切换到校正时钟的时间,而当外部对时校正时钟停止后能够在此时间基础上继续准确计时,并将时钟信息用串口输出。

5.本发明解决其技术问题是采取以下技术方案实现的:

6.1、基于fpga的irig

‑

b直流码解码及对时自动切换方法,其特征在于:包括以下步骤:

7.步骤1、fpga上电后进行预设模式,按照预先设定的时钟进行计时;

8.步骤2、判断是否有对时时钟接入,若有对时时钟接入则进行对时模式并输出对时时钟,并进行步骤3,若无对时时钟接入则仍然按照预设时钟计时,并将时钟信号输出;

9.步骤3、通过fpga解码部分进行irig

‑

b直流码解码;

10.步骤4、判断对时时钟是否断开,若未断开,则返回步骤3,并将解码后的时钟信号作为输出,否则进行步骤5;

11.步骤5、自动切换到计时模式,按照断开前最后一刻的时钟作为计时开始进行循环计时并输出;

12.步骤6、将fpga解码及计算得到的时钟信号转换报文并以一定的发送频率用串口输出;

13.所述计时模式为上电后按照设定的预设时钟进行计时,

14.对时模式为当外部对时信号输入时输出对时信号,

15.计时模式为当外部信号断开后按照断开时刻的时钟继续计时。

16.而且,所述步骤1中判断是否有对时时钟接入的具体实现方法为:fpga检测irig

‑

b直流码的输入情况,以移位寄存器的形式检测irig

‑

b直流码中的参考码元p0是否全为0,若全为0则判断为对时时钟未输入,若不为全0则判断为对时时钟输入。

17.而且,所述步骤2中解码部分包括:检测模块、时钟分频模块、解码模块、转换模块、秒脉冲输出模块和100hz频标输出模块,其中时钟分频模块分别连接检测模块和解码模块,检测模块分别连接解码模块、秒脉冲输出模块和100hz频标输出模块,转换模块连接转换模块。

18.而且,所述步骤3中irig

‑

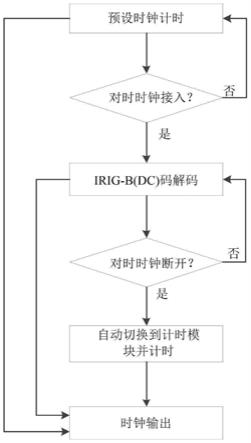

b直流码解码包括以下步骤:

19.步骤3.1、时钟分频模块通过fpga中的锁相环将晶振时钟25mhz分频为1khz作为检测模块和解码模块,并将1khz倍频为50mhz作为解码模块的时钟输入,并将分频为8*9600hz作为串口输出模块的时钟输入;

20.步骤3.2、将参考标志和位置识别标志两个码元作为一个检测标志,以1khz的时钟作为解码模块的时钟采样频率,设置移位寄存器存储20位数据,当寄存器的值达到指定数值时判断为irig

‑

b直流码的帧头,并开始对秒”、“分”、“时”和“天”信息解码;

21.步骤3.3、以1khz时钟作为解码模块的时钟输入,设置移位寄存器存储10位数据,以检测到帧头开始计数,判断移位寄存器中码元的值为“p”码、“1”码或“0”码,并得到“秒”、“分”、“时”和“天”各个时间信息的百位、十位和个位的二进制值;

22.步骤3.4、将步骤3.3中得到的二进制值结合其位权值转换为相应的十进制值,同时将“天”的信息根据平年和闰年中各个月份天数计算出月和日的信息;

23.步骤3.5、秒脉冲输出模块检测到参考标志p0后输出秒脉冲信号;

24.步骤3.6、100hz频标输出模块检测到码元输入时作为标志输出一个100hz的脉冲信号。

25.而且,所述步骤4的具体实现方法为:当外部对时时钟接入时,fpga中存储“秒”信息的寄存器的值跟随对时系统的变化每秒变化一次,而当外部对时时钟断开时则“秒”信息寄存器保持在最后时刻的“秒”信号,判断寄存器中间隔一秒的值是否相等,若相等则判断为外部对时时钟断开,否则外部对时时钟未断开。

26.而且,所述步骤5的具体实现方法为:当检测到外部对时时钟断开时,fpga自动切换到计时模式。

27.而且为,所述步骤6的具体实现方法为:将步骤1至步骤5计算得到的时钟信号转化为串行输出,按照发送协议以一定的波特率和发送周期通过串口输出。

28.本发明的优点和积极效果是:

29.本发明利用fpga芯片构建预设模式、对时模式和计时模式的启动顺序,实现了预设模式、对时模式和计时模式之间自动切换,能够在设定的时间基础上进行准确计时并在外界有校正对时时自动切换到校正时钟的时间,而当外部对时校正时钟停止后能够在此时间基础上继续准确计时,并将时钟信息用串口输出。

30.本发明将“秒”、“分”、“时”和“天”进行解码,得到月、日、时、分、秒等时间信号,同时以串口形式输出,更新频率为1s,方便直观判断时间正确与否。

31.本发明主要通过fpga芯片为主要控制芯片,代码移植性强,实现较为简单单。

附图说明

32.图1为本发明的流程图;

33.图2为本发明的irig

‑

b(dc)码解码及对时自动切换示例图;

34.图3为irig

‑

b(dc)码一帧示意图;

35.图4为irig

‑

b(dc)码的三种基本码字;

36.图5为本发明的irig

‑

b(dc)码解码流程图。

具体实施方式

37.以下结合附图对本发明做进一步详述。

38.基于fpga的irig

‑

b直流码解码及对时自动切换方法,如图1所示,包括以下步骤:

39.步骤1、fpga上电后进行预设模式,按照预先设定的时钟进行计时。

40.如图2所示,在系统程序中预设一个时间,预设时间为2020年12月31日23时59分59秒,当没有检测到外界对时时钟接入时,程序按照会按照预设时间进行计时并输出,即下一秒钟输出为2021年1月1日0时0分0秒,再下一秒钟为2021年1月1日0时0分1秒,以此类推。

41.步骤2、判断是否有对时时钟接入,若有对时时钟接入则进行对时模式并输出对时时钟,并进行步骤3,若无对时时钟接入则仍然按照预设时钟计时,并将时钟信号输出。

42.如图3所示,irig

‑

b(dc)码是一种串行的时间格式,其一帧的时间为1s,一帧数据由100个码元组成。如图4所示,irig

‑

b(dc)码由位置识别标志、参考码元、码字和索引标志4种码元组成,其中包括“p”码、“1”码和“0”码。

43.fpga检测irig

‑

b直流码的输入情况,以移位寄存器的形式检测irig

‑

b直流码中的参考码元p0是否全为0,若全为0则判断为对时时钟未输入,若不为全0则判断为对时时钟输入。

44.步骤3、通过fpga解码部分进行irig

‑

b(dc)码解码。

45.如图5所示,解码部分包括:检测模块、时钟分频模块、解码模块、转换模块、秒脉冲输出模块和100hz频标输出模块,其中时钟分频模块分别连接检测模块和解码模块,检测模块分别连接解码模块、秒脉冲输出模块和100hz频标输出模块,转换模块连接转换模块。

46.irig

‑

b直流码解码包括以下步骤:

47.步骤3.1、每个码元的长度是10ms,当以采样时钟频率为1khz时“1”码为1111100000、“0”码为1100000000和p码分别为1111111100,时钟分频模块通过fpga中的锁相环将晶振时钟25mhz分频为1khz作为检测模块和解码模块,并将1khz倍频为50mhz作为解码模块的时钟输入,并将分频为8*9600hz作为串口输出模块的时钟输入。

48.步骤3.2、完整的一帧irig

‑

b(dc)码的时钟信息以“秒”、“分”、“时”和“天”的顺序输入,由于参考码元和位置识别标志的脉宽都为8ms,将参考标志和位置识别标志两个码元作为一个检测标志,以1khz的时钟作为解码模块的时钟采样频率,设置移位寄存器存储20位数据,当寄存器的值为11111111001111111100时判断为irig

‑

b(dc)码的帧头,并开始对秒”、“分”、“时”和“天”信息解码。

49.步骤3.3、以1khz时钟作为解码模块的时钟输入,设置移位寄存器存储10位数据,以检测到帧头开始计数,判断移位寄存器中第1、2、3、4、6、7、8、10、11、12、13、15、16、17、20、21、22、23、25、26、30、31、32、33、35、36、37、38、40、41个码元的值,当移位寄存器的值与1111111100相等时判定为“p”码,当移位寄存器的值为1111100000相等时判定为“1”码,当移位寄存器的值与1100000000相等时判定为“0”码。

50.步骤3.4、将步骤3.3中得到的“秒”、“分”、“时”和“天”各个时间信息的百位、十位

和个位的二进制值结合其位权值转换为相应的十进制值,并且由于irig

‑

b(dc)码中只包含当年的天数信息而没有月份的信息,因此需要将“天”的信息根据平年和闰年中各个月份天数计算出月和日的信息。例,解码输出后秒信号的二进制表示为01011001,按照b码的输入顺序,则个位是9,十位是5,因此结合其位权值计算可得5*10 9=59,即59秒。

51.步骤3.5、irig

‑

b(dc)码的准秒时刻是在位置识别标志p

r

脉冲的上升沿时刻,因此当检测到参考标志p0后输出秒脉冲信号;

52.步骤3.6、100hz频标输出模块检测到码元输入时作为标志输出一个100hz的脉冲信号。

53.步骤4、判断对时时钟是否断开,若未断开,则返回步骤3,并将解码后的时钟信号作为输出,否则进行步骤5。

54.当外部对时时钟接入时,转换模块中存储“秒”信息的寄存器的值跟随对时系统的变化每秒变化一次,而当外部对时时钟断开时则“秒”信息寄存器保持在最后时刻的“秒”信号,判断寄存器中间隔一秒的值是否相等,若相等则判断为外部对时时钟断开,否则外部对时时钟未断开。

55.步骤5、自动切换到计时模式,按照断开前最后一刻的时钟作为计时开始进行循环计时并输出。步骤3中转换模块中设置寄存器存储在外部对时时钟断开时会存储断开前最后时刻的完整信号,因此以此时寄存器中的存储时间信息作为计时起始值,由此继续循环计时。以图2中为例,上电时系统的预设时间为2020年12月31日23时59分59秒,系统在此基础上进行计时,而检测到外部对时时钟输入时,系统时间校正为对时时钟为2021年6月15日1时2分15秒,在对时时钟接入期间以对时时钟时间为输出,当在17秒时外部对时时钟断开,系统检测到断开信号后切换到计时模式继续计时。

56.步骤6、将fpga解码及计算得到的时钟信号转换报文并以一定的发送频率用串口输出。

57.将步骤1至步骤5计算得到的时钟信号转化为串行输出,按照发送协议输出一帧报文数据,波特率设置为9600bps,发送周期为1s,并以串口的形式输出。

58.计时模式为上电后按照设定的预设时钟进行计时,对时模式为当外部对时信号输入时能够输出对时信号,计时模式为当外部信号断开后按照断开时刻的时钟继续计时,fpga芯片为xc6slx25

‑

2ftg256i。

59.需要强调的是,本发明所述的实施例是说明性的,而不是限定性的,因此本发明包括并不限于具体实施方式中所述的实施例,凡是由本领域技术人员根据本发明的技术方案得出的其他实施方式,同样属于本发明保护的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。