技术特征:

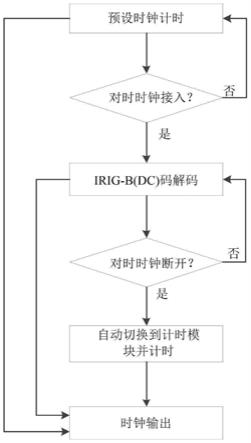

1.基于fpga的irig

‑

b直流码解码及对时自动切换方法,其特征在于:包括以下步骤:步骤1、fpga上电后进行预设模式,按照预先设定的时钟进行计时;步骤2、判断是否有对时时钟接入,若有对时时钟接入则进行对时模式并输出对时时钟,并进行步骤3,若无对时时钟接入则仍然按照预设时钟计时,并将时钟信号输出;步骤3、通过fpga解码部分进行irig

‑

b直流码解码;步骤4、判断对时时钟是否断开,若未断开,则返回步骤3,并将解码后的时钟信号作为输出,否则进行步骤5;步骤5、自动切换到计时模式,按照断开前最后一刻的时钟作为计时开始进行循环计时并输出;步骤6、将fpga解码及计算得到的时钟信号转换报文并以一定的发送频率用串口输出;所述计时模式为上电后按照设定的预设时钟进行计时,对时模式为当外部对时信号输入时输出对时信号,计时模式为当外部信号断开后按照断开时刻的时钟继续计时。2.根据权利要求1所述的基于fpga的irig

‑

b直流码解码及对时自动切换方法,其特征在于:所述步骤1中判断是否有对时时钟接入的具体实现方法为:fpga检测irig

‑

b直流码的输入情况,以移位寄存器的形式检测irig

‑

b直流码中的参考码元p0是否全为0,若全为0则判断为对时时钟未输入,若不为全0则判断为对时时钟输入。3.根据权利要求1所述的基于fpga的irig

‑

b直流码解码及对时自动切换方法,其特征在于:所述步骤2中解码部分包括:检测模块、时钟分频模块、解码模块、转换模块、秒脉冲输出模块和100hz频标输出模块,其中时钟分频模块分别连接检测模块和解码模块,检测模块分别连接解码模块、秒脉冲输出模块和100hz频标输出模块,转换模块连接转换模块。4.根据权利要求1或3所述的基于fpga的irig

‑

b直流码解码及对时自动切换方法,其特征在于:所述步骤3中irig

‑

b直流码解码包括以下步骤:步骤3.1、时钟分频模块通过fpga中的锁相环将晶振时钟25mhz分频为1khz作为检测模块和解码模块,并将1khz倍频为50mhz作为解码模块的时钟输入,并将分频为8*9600hz作为串口输出模块的时钟输入;步骤3.2、将参考标志和位置识别标志两个码元作为一个检测标志,以1khz的时钟作为解码模块的时钟采样频率,设置移位寄存器存储20位数据,当寄存器的值达到指定数值时判断为irig

‑

b直流码的帧头,并开始对秒”、“分”、“时”和“天”信息解码;步骤3.3、以1khz时钟作为解码模块的时钟输入,设置移位寄存器存储10位数据,以检测到帧头开始计数,判断移位寄存器中码元的值为“p”码、“1”码或“0”码,并得到“秒”、“分”、“时”和“天”各个时间信息的百位、十位和个位的二进制值;步骤3.4、将步骤3.3中得到的二进制值结合其位权值转换为相应的十进制值,同时将“天”的信息根据平年和闰年中各个月份天数计算出月和日的信息;步骤3.5、秒脉冲输出模块检测到参考标志p0后输出秒脉冲信号;步骤3.6、100hz频标输出模块检测到码元输入时作为标志输出一个100hz的脉冲信号。5.根据权利要求1所述的基于fpga的irig

‑

b直流码解码及对时自动切换方法,其特征在于:所述步骤4的具体实现方法为:当外部对时时钟接入时,fpga中存储“秒”信息的寄存器的值跟随对时系统的变化每秒变化一次,而当外部对时时钟断开时则“秒”信息寄存器保

持在最后时刻的“秒”信号,判断寄存器中间隔一秒的值是否相等,若相等则判断为外部对时时钟断开,否则外部对时时钟未断开。6.根据权利要求1所述的基于fpga的irig

‑

b直流码解码及对时自动切换方法,其特征在于:所述步骤5的具体实现方法为:当检测到外部对时时钟断开时,fpga自动切换到计时模式。7.根据权利要求1所述的基于fpga的irig

‑

b直流码解码及对时自动切换方法,其特征在于:所述步骤6的具体实现方法为:将步骤1至步骤5计算得到的时钟信号转化为串行输出,按照发送协议以一定的波特率和发送周期通过串口输出。

技术总结

本发明涉及基于FPGA的IRIG

技术研发人员:马文霞 肖泉建 孙文超 王言畅

受保护的技术使用者:中国船舶重工集团公司第七0七研究所

技术研发日:2021.07.02

技术公布日:2021/12/13

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。