1.本发明的实施例是涉及一种半导体器件的制造方法。

背景技术:

2.半导体行业已经由于多种电子组件(例如,晶体管、二极管、电阻器、电容器等)的集成密度的持续改进而经历快速增长。主要来说,最小特征尺寸的反复减小已经带来集成密度的改进,这允许将更多组件集成到给定区域中。随着对缩小的电子器件的需求的增长,对半导体管芯的更小和更有创造性的封装技术的需求也已经出现。这些封装系统的实例是叠层封装(package

‑

on

‑

package;pop)技术。在pop器件中,顶部半导体封装堆叠在底部半导体封装的顶部上以提供高水平的集成和组件密度。pop技术通常能够在印刷电路板(printed circuit board;pcb)上生产功能性增强和小占据面积的半导体器件。

技术实现要素:

3.本发明实施例提供一种制造半导体器件的方法,所述方法包括:将聚合物材料放置在衬底上方,图案化聚合物材料以及在200℃到300℃的范围内的温度下固化聚合物材料。聚合物材料包含聚合物前体、光敏剂以及溶剂。所述聚合物前体包含

[0004][0005]

其中r表示

[0006]

附图说明

[0007]

当结合附图阅读时从以下详细描述最好地理解本公开的各方面。应注意,根据业界中的标准惯例,各种特征未按比例绘制。实际上,为了论述清楚起见,可任意增大或减小各种特征的尺寸。

[0008]

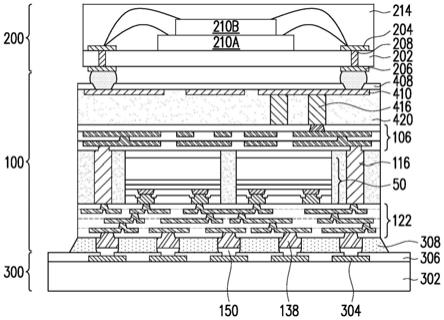

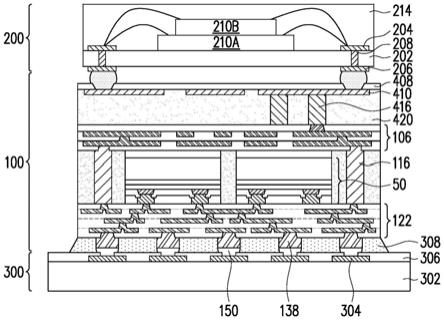

图1示出根据一些实施例的集成电路管芯的横截面视图。

[0009]

图2到图7示出根据一些实施例的在用于形成封装组件的工艺期间的中间步骤的横截面视图。

[0010]

图8示出根据一些实施例的介电层的形成。

[0011]

图9a到图9d进一步示出根据一些实施例的介电层的形成。

[0012]

图10a到图10e示出根据一些实施例的介电层的图案化。

[0013]

图11到图24示出根据一些实施例的在用于形成封装组件的工艺期间的中间步骤的横截面视图。

[0014]

图25和图26示出根据一些实施例的器件堆叠的形成和实施的横截面视图。

具体实施方式

[0015]

以下公开内容提供用于实现本发明的不同特征的许多不同实施例或实例。下文描述组件和布置的具体实例以简化本公开。当然,这些组件和布置只是实例且并不意欲为限制性的。举例来说,在以下描述中,第一特征在第二特征上方或第二特征上的形成可包含第一特征与第二特征直接接触地形成的实施例,且还可包含额外特征可在第一特征与第二特征之间形成以使得第一特征与第二特征可不直接接触的实施例。另外,本公开可在各种实例中重复图式元件符号和/或字母。这种重复是出于简化和清楚的目的且本身并不指示所论述的各种实施例和/或配置之间的关系。

[0016]

另外,为易于描述,本文中可使用如“在

…

之下(beneath)”、“在

…

下方(below)”、“下部(lower)”、“在

…

之上(above)”、“上部(upper)”以及类似术语的空间相对术语来描述如各图中所示出的一个元件或特征与另一(一些)元件或特征的关系。除图中所描绘的定向以外,空间相对术语意欲涵盖器件在使用或操作中的不同定向。装置可以其它方式定向(旋转90度或处于其它定向),且本文中所使用的空间相对描述词同样可相应地进行解释。

[0017]

现将针对利用聚酰亚胺材料在半导体器件内形成介电层的特定实施例来描述实施例。然而,所描述的实施例并不旨在限于本文中所描述的实施例,而是可用于广泛多种实施例中。

[0018]

图1示出根据一些实施例的集成电路管芯50的横截面视图。集成电路管芯50将在后续处理中封装以形成集成电路封装。集成电路管芯50可以是逻辑管芯(例如,中央处理单元(central processing unit;cpu)、图形处理单元(graphics processing unit;gpu)、系统芯片(system

‑

on

‑

a

‑

chip;soc)、应用处理器(application processor;ap)、微控制器等)、存储器管芯(例如,动态随机存取存储器(dynamic random access memory;dram)管芯、静态随机存取存储器(static random access memory;sram)管芯等)、功率管理管芯(例如,功率管理集成电路(power management integrated circuit;pmic)管芯)、射频(radio frequency;rf)管芯、传感器管芯、微机电系统(micro

‑

electro

‑

mechanical

‑

system;pmic)管芯、信号处理管芯(例如,数字信号处理(digital signal processing;dsp)管芯)、前端管芯(例如,模拟前端(analog front

‑

end;afe)管芯)、类似物或其组合。

[0019]

集成电路管芯50可形成于晶片中,所述晶片可包含在后续步骤中单体化以形成多个集成电路管芯的不同器件区。集成电路管芯50可根据可适用的制造工艺进行处理,以形成集成电路。举例来说,集成电路管芯50包含半导体衬底52,如掺杂或未掺杂的硅,或绝缘体上半导体(semiconductor

‑

on

‑

insulator;soi)衬底的有源层。半导体衬底52可包含:其它半导体材料,如锗;化合物半导体,包含碳化硅、砷化镓、磷化镓、磷化铟、砷化铟和/或锑化铟;合金半导体,包含sige、gaasp、alinas、algaas、gainas、gainp和/或gainasp;或其组合。也可使用其它衬底,如多层或梯度衬底。半导体衬底52具有有源表面(例如,图1中面朝上的表面),有时称为前侧,以及非有源表面(例如,图1中面朝下的表面),有时称为背侧。

[0020]

器件(由晶体管表示)54可形成于半导体衬底52的前表面处。器件54可以是有源器件(例如,晶体管、二极管等)、电容器、电阻器等。层间介电质(inter

‑

layer dielectric;ild)56在半导体衬底52的前表面上方。ild 56包围且可覆盖器件54。ild 56可包含由如磷

硅酸盐玻璃(phospho

‑

silicate glass;psg)、硼硅酸盐玻璃(boro

‑

silicate glass;bsg)、硼掺杂磷硅酸盐玻璃(boron

‑

doped phospho

‑

silicate glass;bpsg)、未掺杂硅酸盐玻璃(undoped silicate glass;usg)或类似物的材料形成的一或多个介电层。

[0021]

导电插塞58延伸穿过ild 56从而以电气和物理方式耦合器件54。举例来说,当器件54是晶体管时,导电插塞58可耦合晶体管的栅极和源极/漏极区。导电插塞58可由钨、钴、镍、铜、银、金、铝、类似物或其组合形成。内连线结构60在ild 56和导电插塞58上方。内连线结构60互连器件54,以形成集成电路。内连线结构60可通过例如ild 56上的介电层中的金属化图案来形成。金属化图案包含形成在一或多个低k介电层中的金属线和通孔。内连线结构60的金属化图案通过导电插塞58电耦合到器件54。

[0022]

集成电路管芯50更包含与其进行外部连接的衬垫62,如铝衬垫。衬垫62在集成电路管芯50的有源侧上,如在内连线结构60中和/或上。一或多个钝化膜64在集成电路管芯50上,如在部分内连线结构60和部分衬垫62上。开口穿过钝化膜64延伸到衬垫62。如导电柱(例如,由如铜的金属形成)的管芯连接件66延伸穿过钝化膜64中的开口,且以物理和电气方式耦合到相应一个衬垫62。管芯连接件66可通过例如镀覆或类似方法形成。管芯连接件66电耦合集成电路管芯50的相应集成电路。

[0023]

任选地,焊料区(例如,焊料球或焊料凸块)可安置在衬垫62上。焊料球可用于对集成电路管芯50执行芯片探针(chip probe;cp)测试。可对集成电路管芯50执行cp测试以确定集成电路管芯50是否是已知良好管芯(known good die;kgd)。因此,仅作为kgd的集成电路管芯50经历后续处理且进行封装,且未通过cp测试的管芯不进行封装。在测试之后,可在后续处理步骤中去除焊料区。

[0024]

介电层68可(或可不)在集成电路管芯50的有源侧上,如在钝化膜64和管芯连接件66上。介电层68横向密封管芯连接件66,且介电层68与集成电路管芯50横向相连。首先,介电层68可掩埋管芯连接件66,以使得介电层68的最顶部表面在管芯连接件66的最顶部表面上方。在其中焊料区安置在管芯连接件66上的一些实施例中,介电层68也可掩埋焊料区。可替代地,可在形成介电层68之前去除焊料区。

[0025]

介电层68可以是聚合物,如pbo、聚酰亚胺、bcb或类似物;氮化物,如氮化硅或类似物;氧化物,如氧化硅、psg、bsg、bpsg或类似物;类似物;或其组合。介电层68可例如通过旋转涂布、层压、化学气相沉积(chemical vapor deposition;cvd)或类似操作而形成。在一些实施例中,在集成电路管芯50的形成期间,管芯连接件66外露于介电层68。在一些实施例中,管芯连接件66保持掩埋,且在用于封装集成电路管芯50的后续工艺期间暴露。暴露管芯连接件66可去除管芯连接件66上可能存在的任何焊料区。

[0026]

在一些实施例中,集成电路管芯50是包含多个半导体衬底52的堆叠器件。举例来说,集成电路管芯50可以是包含多个存储器管芯的存储器器件,如混合存储器立方体(hybrid memory cube;hmc)模块、高带宽存储器(high bandwidth memory;hbm)模块或类似物。在这类实施例中,集成电路管芯50包含通过衬底穿孔(through

‑

substrate via;tsv)互连的多个半导体衬底52。每一个半导体衬底52可(或可不)具有内连线结构60。

[0027]

图2到图20示出根据一些实施例的在用于形成第一封装组件100的工艺期间的中间步骤的横截面视图。示出第一封装区100a和第二封装区100b,且一或多个集成电路管芯50被封装以在每一个封装区100a和每一个封装区100b中形成集成电路封装。集成电路封装

也可称为集成扇出型(integrated fan

‑

out;info)封装。

[0028]

在图2中,提供载体衬底102,且在载体衬底102上形成释放层104。载体衬底102可以是玻璃载体衬底、陶瓷载体衬底或类似物。载体衬底102可以是晶片,以使得多个封装可同时形成在载体衬底102上。

[0029]

释放层104可由聚合物类材料形成,所述材料可连同载体衬底102一起从将在后续步骤中形成的上覆结构去除。在一些实施例中,释放层104是环氧树脂类热释放材料,所述材料在加热时失去其粘合属性,如光到热转换(light

‑

to

‑

heat

‑

conversion;lthc)释放涂层。在其它实施例中,释放层104可以是紫外线(ultra

‑

violet;uv)胶,所述紫外线胶在暴露于uv光时失去其粘合属性。释放层104可以液体形式分配且固化,可以是层压到载体衬底102上的层压膜,或可以是类似物。释放层104的顶部表面可齐平且可具有高度的平面性。

[0030]

在图3中,在释放层104上可形成介电层408。介电层408的底部表面可与释放层104的顶部表面接触。在一些实施例中,介电层408由聚合物形成,如聚苯并恶唑(polybenzoxazole;pbo)、聚酰亚胺、苯环丁烷(benzocyclobutene;bcb)或类似物。在其它实施例中,介电层408由以下形成:氮化物,如氮化硅;氧化物,如氧化硅、磷硅酸盐玻璃(phosphosilicate glass;psg)、硼硅酸盐玻璃(borosilicate glass;bsg)、硼掺杂磷硅酸盐玻璃(boron

‑

doped phosphosilicate glass;bpsg)或类似物;或类似物。介电层408可通过任何可接受的沉积工艺形成,如旋转涂布、cvd、层压、类似工艺或其组合。

[0031]

在图4中,在介电层408上可形成金属化图案410。作为形成金属化图案410的实例,晶种层形成在介电层408上方。在一些实施例中,晶种层是金属层,所述金属层可以是单个层或包括由不同材料形成的多个子层的复合层。在一些实施例中,晶种层包括钛层和在钛层上方的铜层。晶种层可使用例如物理气相沉积(physical vapor deposition;pvd)或类似操作而形成。随后,在晶种层上形成光刻胶(未绘示)且图案化光刻胶。光刻胶可通过旋转涂布或类似操作而形成,且可暴露于光以用于图案化。光刻胶的图案对应于金属化图案410。图案化形成穿过光刻胶的开口以暴露晶种层。导电材料形成在光刻胶的开口中和晶种层的暴露部分上。导电材料可通过镀覆(如电镀或化学镀)或类似方法形成。导电材料可包括金属,如铜、钛、钨、铝或类似物。随后,去除光刻胶和晶种层上不形成导电材料的部分。可通过可接受的灰化或剥离工艺(如使用氧等离子或类似工艺)去除光刻胶。一旦将光刻胶去除,那么如通过使用可接受的刻蚀工艺(如通过湿式或干式刻蚀)来去除晶种层的暴露部分。晶种层和导电材料的剩余部分形成金属化图案410。

[0032]

在一些实施例中,将如集成电路管芯的管芯(未示出)附接到介电层408和/或金属化图案410。管芯可大体上类似于下文关于图14所描述的集成电路管芯50。如下文关于集成电路管芯50的图14所描述的方法,管芯可附接到介电层408和/或金属化图案410。

[0033]

在图5中,在金属化图案410上形成穿孔416。作为形成穿孔416的实例,在金属化图案410上形成光刻胶且图案化光刻胶。光刻胶可通过旋转涂布或类似操作而形成,且可暴露于光以用于图案化。光刻胶的图案对应于导通孔。图案化形成穿过光刻胶的开口以暴露晶种层。在光刻胶的开口中和在金属化图案410的暴露部分上形成导电材料,从而形成穿孔416。导电材料可通过镀覆(如电镀或化学镀)或类似方法形成。导电材料可包括金属,如铜、钛、钨、铝或类似物。如通过可接受的灰化或剥离工艺(如使用氧等离子或类似工艺)去除光刻胶。

[0034]

在图6中,将密封体420形成在各种组件上和周围。在形成之后,密封体420密封穿孔416。密封体420可以是模制化合物、环氧树脂或类似物。密封体420可通过压缩模制、转移模制或类似方法来涂覆,且可形成在载体衬底102上方,使得掩埋或覆盖穿孔416。密封体420进一步形成在金属化图案410上方且可延伸以覆盖介电层408的部分。在一些实施例中,密封体420进一步密封附接到介电层408和/或金属化图案410的管芯(未示出)。密封体420可以液体或半液体形式涂覆且随后相继固化。

[0035]

在图7中,对密封体420执行平坦化工艺以暴露穿孔416。平坦化工艺也可去除穿孔416的材料。在工艺变化内的平坦化工艺之后,穿孔416和密封体420的顶部表面大体上共面。平坦化工艺可以是例如化学机械抛光(chemical

‑

mechanical polish;cmp)、研磨工艺或类似工艺。在一些实施例中,例如,如果穿孔416已暴露,那么可省略平坦化。在一些实施例中,平坦化还暴露附接到介电层408和/或金属化图案410的管芯(未示出)上的管芯连接件。

[0036]

在图8到图12中,可在密封体420和穿孔416的顶部表面上形成背侧重布线结构106(未在图8中完全示出,但在下文关于图12完全示出)。在所绘示的实施例中,背侧重布线结构106包含介电层108、包含延伸穿过介电层108的导通孔的金属化图案110(有时称为重布线层或重布线线路)、介电层112、金属化图案422以及介电层425。可在背侧重布线结构106中形成更多或更少介电层和金属化图案,如两个到五个介电层和一个到四个金属化图案。如果将形成更少介电层和金属化图案,那么可省略下文论述的步骤和工艺。如果将形成更多介电层和金属化图案,那么可重复下文论述的步骤和工艺。

[0037]

现参考图8,在密封体420和穿孔416上形成介电层108。在一些实施例中,介电层108可由聚合物材料形成,所述聚合物材料包括溶剂、聚合物前体500、交联剂510以及光敏剂。混合物可进一步包括一或多种添加剂。

[0038]

在一些实施例中,聚合物前体500可以是聚合物,所述聚合物设计成与剩余组分一起起作用以便形成介电层108。可选择聚合物前体500以产生具有更少酰亚胺环的聚酰亚胺主链,这可降低聚合物材料的耗散因子(dissipation factor;df)且减少器件插入损耗。如此,在一些实施例中,聚合物前体500可以是包括具有下式的多个单体的聚酰胺酸酯:

[0039][0040]

其中r具有下式:

[0041][0042]

在一些实施例中,混合物包括约20重量%到约40重量%的聚酰胺酸酯,如约25%到约35%。

[0043]

图9a和图9b示出,在利用上文所描述的聚酰胺酸酯形成介电层108的实施例中,可使用一系列反应物制备聚合物前体500。例如且首先参见图9a,第一反应物502和第二反应物504可一起反应以获得第一中间产物506。在一实施例中,第一反应物502可包括芳香族酸

酐,如3,3,4,4

‑

联苯四甲酸二酐(3,3,4,4

‑

biphenyltetracarboxylic dianhydride;bpda)、4,4'

‑

氧双苯二甲酸酐(4,4

’‑

oxydiphthalic anhydride)或4,4'

‑

(4,4'

‑

亚异丙基二苯氧基)双(邻苯二甲酸酐)(4,4

’‑

(4,4

’‑

isopropylidenediphenoxy)bis(phthalic anhydride)),而第二反应物504可包括如甲基丙烯酸2

‑

羟基乙酯(2

‑

hydroxyethyl methacrylate)的化学物质。然而,可利用任何合适的反应物。

[0044]

图9b示出,一旦已获得第一中间产物506,那么第一中间产物506可与第三反应物508反应以获得所需聚合物前体500。在一实施例中,第三反应物508可以是芳香族胺,如2,2

‑

双[4

‑

(4

‑

氨基苯氧基)苯基]丙烷(4,4

‑

(4,4

‑

isopropylidenediphenyl

‑

1,1

‑

diyldioxy)dianiline;bapp)、4,4'

‑

(1,1'

‑

联二苯

‑

4,4'

‑

二基二氧基)二苯胺(4,4

’‑

(1,1

’‑

biphenyl

‑

4,4

’‑

diyldioxy)dianiline)或4,4'

‑

(1,4

‑

亚苯基二异亚丙基)双苯胺(4,4

’‑

(1,4

‑

phenylenediisopropylidene)bisaniline)。然而,可利用任何合适的反应物。

[0045]

图9c到图9d示出可形成的替代中间前体。举例来说,图9c示出可在形成聚合物前体500之前产生的第一中间聚合物前体500',而图9d示出也可在形成聚合物前体500之前产生的第二中间聚合物前体500”。可形成任何合适的中间聚合物前体,且所有这些前体完全意欲包含在实施例的范围内。

[0046]

在一些实施例中,溶剂包括可用于混合、运输以及分散聚合物材料的剩余组分的有机溶剂。如此,在一些实施例中,有机溶剂可包括1

‑

甲基

‑2‑

吡咯烷酮(1

‑

methyl

‑2‑

pyrrolidone;nmp)、γ

‑

丁内酯(gamma

‑

butyrolactone;gbl)、四氢呋喃(tetrahydrofuran;thf)或二甲亚砜(dimethyl sulfoxide;dmso)。然而,可利用任何合适的有机溶剂。在一些实施例中,聚合物材料包括约30重量%到约60重量%的溶剂。

[0047]

在额外实施例中,溶剂不仅可额外包括如上文所描述的有机溶剂,而且也可包括第二溶剂以实现更好的溶解度。在这类实施例中,溶剂可不仅包括1

‑

甲基

‑2‑

吡咯烷酮(nmp),而且也可包括第二有机溶剂,如乳酸乙酯(ethyl lactate;el)、二甲基甲酰胺(dimethylformamide;dmf)或二甲亚砜(dmso)。然而,任何合适的有机溶剂可用于第二有机溶剂。

[0048]

在一些实施例中,聚合物材料包括约45重量%到约55重量%的nmp。使用约45重量%到约55重量%的nmp可用于实现合适的粘度以便产生所需膜厚度。使用小于约45重量%的nmp可以是不利的,因为它可导致高粘度和差的溶解度。使用大于约55重量%的nmp可以是不利的,因为它可导致低粘度和不合期望的薄膜。

[0049]

在一些实施例中,聚合物材料包括约10重量%到约15重量%的el。使用约10重量%到约15重量%的el可用于实现所需溶解度。使用小于约10重量%的el可以是不利的,因为它可导致非所需的沉淀。使用大于约15重量%的el可以是不利的,因为它可导致溶液中的非所需空隙的形成。

[0050]

交联剂510(未在图9a到图9d中示出,但在下文关于图10b示出)可形成在聚合物材料的曝光期间将一个聚合物链连接到另一个聚合物链的键(参见下文的图10b)。所得组合物可具有比没有交联时更大的刚性。在一些实施例中,交联剂510包括任何合适的交联剂,如四乙二醇二甲基丙烯酸酯(丙烯酸酯)。聚合物材料可包括约1重量%到约5重量%的交联剂510。在其它实施例中,在混合物中不使用交联剂以形成聚合物材料,且聚合物材料不包括交联剂510。

[0051]

光敏剂或光活性组分(photoactive component;pac)可以是光活性组分,如光酸产生剂、光碱产生剂、自由基产生剂或类似物,且光敏剂可以是正性作用的或负性作用的。在其中光敏剂是光酸产生剂的实施例中,光敏剂可包括卤代三嗪、鎓盐、重氮盐、芳香族重氮盐、磷鎓盐、硫鎓盐、碘鎓盐、酰亚胺磺酸盐、肟磺酸盐、二砜、邻硝基苄基磺酸盐、磺化酯、卤代磺酰基氧基二甲酰亚胺、重氮二砜、α

‑

氰基氧基胺

‑

磺酸酯、酰亚胺磺酸酯、酮重氮砜、磺酰基重氮酯、1,2

‑

二(芳基磺酰基)肼、硝基苄基酯以及均三嗪衍生物、这些的合适的组合以及类似物。

[0052]

可使用的光酸产生剂的具体实例包含α.

‑

(三氟甲基磺酰氧基)

‑

双环[2.2.1]庚

‑5‑

烯

‑

2,3

‑

二甲酰亚胺(mdt)、n

‑

羟基

‑

萘二甲酰亚胺(ddsn)、安息香甲苯磺酸酯、叔丁基苯基

‑

α

‑

(对甲苯磺酰基氧基)

‑

乙酸酯和叔丁基

‑

α

‑

(对甲苯磺酰基氧基)

‑

乙酸酯、六氟锑酸三芳基硫鎓盐和六氟锑酸二芳基碘鎓盐、六氟砷酸盐、三氟甲烷磺酸盐、全氟辛烷磺酸碘鎓盐、n

‑

樟脑磺酰氧基萘二甲酰亚胺、n

‑

五氟苯基磺酰氧基萘二甲酰亚胺、离子碘鎓磺酸盐(如二芳基碘鎓(烷基或芳香基)磺酸盐和双

‑

(二叔丁基苯基)碘鎓莰基磺酸盐)、全氟烷磺酸酯(如全氟戊烷磺酸酯、全氟辛烷磺酸酯、全氟甲烷磺酸酯)、芳香基(例如,苯基或苄基)三氟甲磺酸酯(如三苯基硫鎓三氟甲磺酸盐或双

‑

(叔丁基苯基)碘鎓三氟甲磺酸盐);连苯三酚衍生物(例如,连苯三酚的三甲磺酸酯)、羟基酰亚胺的三氟甲烷磺酸酯、α,α'

‑

双

‑

磺酰基

‑

重氮甲烷、硝基取代的苄醇的磺酸酯、萘醌

‑4‑

二叠氮、烷基二砜以及类似物。

[0053]

在其中光敏剂是自由基产生剂的实施例中,光敏剂可包括正苯基甘氨酸、芳香族酮(如二苯甲酮、n,n'

‑

四甲基

‑

4,4'

‑

二氨基二苯甲酮、n,n'

‑

四乙基

‑

4,4'

‑

二氨基二苯甲酮、4

‑

甲氧基

‑

4'

‑

二甲基氨基苯并

‑

苯酮、3,3'

‑

二甲基

‑4‑

甲氧基二苯甲酮、p,p'

‑

双(二甲基氨)苯并

‑

苯酮、p,p'

‑

双(二乙基氨)

‑

二苯甲酮、蒽醌、2

‑

乙基蒽醌、萘醌以及菲醌)、安息香(如安息香、安息香甲基醚、安息香乙基醚、安息香异丙醚、安息香

‑

正

‑

丁基醚、安息香

‑

苯醚、甲基安息香以及乙基安息香)、苄基衍生物(如二苄基、苄基二苯基二硫化物以及苄基二甲基缩酮)、吖啶衍生物(如9

‑

苯基吖啶和1,7

‑

双(9

‑

吖啶基)庚烷)、噻吨酮(如2

‑

氯噻吨酮、2

‑

甲基噻吨酮、2,4

‑

二乙基噻吨酮、2,4

‑

二甲基噻吨酮以及2

‑

异丙基噻吨酮)、苯乙酮(如1,1

‑

二氯苯乙酮、对叔丁基二氯

‑

苯乙酮、2,2

‑

二乙氧基苯乙酮、2,2

‑

二甲氧基

‑2‑

苯基苯乙酮以及2,2

‑

二氯

‑4‑

苯氧基苯乙酮)、2,4,5

‑

三芳基咪唑二聚体(如2

‑

(邻氯苯基)

‑

4,5

‑

二苯基咪唑二聚体、2

‑

(邻氯苯基)

‑

4,5

‑

二(间甲氧基苯基咪唑二聚体、2

‑

(邻氟苯基)

‑

4,5

‑

二苯基咪唑二聚体、2

‑

(邻甲氧基苯基)

‑

4,5

‑

二苯基咪唑二聚体、2

‑

(对甲氧基苯基)

‑

4,5

‑

二苯基咪唑二聚体、2,4

‑

二(对甲氧基苯基)

‑5‑

苯基咪唑二聚体、2

‑

(2,4

‑

二甲氧基苯基)

‑

4,5

‑

二苯基咪唑二聚体以及2

‑

(对甲基巯基苯基)

‑

4,5

‑

二苯基咪唑二聚体)、这些的合适的组合或类似物。

[0054]

在其中光敏剂是光碱产生剂的实施例中,光敏剂可包括季铵二硫代氨基甲酸盐、α氨基酮、含有分子的肟

‑

尿烷(如二二苯甲酮肟六亚甲基二尿烷)、四有机基硼酸铵盐以及n

‑

(2

‑

硝基苄氧基羰基)环胺,这些的合适的组合或类似物。在一实施例中,正型光敏剂(如二苯甲酰基甲烷)或负型光敏剂(如2,2'

‑

(苯基亚氨基)二乙醇)可用作光敏剂。然而,如本领域的普通技术人员将认识到,在本文中所列的化学化合物仅旨在作为光敏剂的所示出实例且并不旨在将实施例仅限制为具体描述的那些光敏剂。更确切而言,可利用任何合适的光敏剂,且所有这些光敏剂完全意欲包含在本发明的实施例的范围内。聚合物材料可包括约1

重量%到8重量%的光敏剂。在其它实施例中,在混合物中不使用光敏剂来形成聚合物材料,且聚合物材料不包括光敏剂。

[0055]

除光敏剂之外,混合物也可包括添加剂。添加剂有助于降低用于固化的温度。确切地说,添加剂可用于增大混合物的自由体积。添加剂的高极性和/或高位阻可用于(例如通过降低偶极矩)克服在曝光期间和曝光之后形成的聚合物的极性。因此,如下文所论述,可使用较低的曝光能量。聚合物的反应性部分上的降低的极性允许分子的分支链出现在一起以形成环,且由此改进在较低温度下固化期间的环化。添加剂可充当反应的催化剂,且因此在固化之前和之后与聚合物保持分离,但在固化之后,最终聚合物层或介电层可包括原始添加剂中的一些或全部。

[0056]

添加剂可包括适合于增大聚合物材料或聚合物混合物的自由体积的任何分子。如上文所论述,添加剂可具有高极性和/或高位阻。为增大混合物的自由体积,可选择添加剂且添加剂可具有与所选择的交联剂510类似的结构。举例来说,添加剂可以是聚醚,如聚乙二醇(polyethylene glycol;peg)(例如,分子量为600且包括5重量%的聚合物材料)、聚丙二醇(polypropylene glycol;ppg)、这些的组合或类似物。类似地,在其中将四乙二醇二甲基丙烯酸酯(tetraethylene glycol dimethacrylate)用作交联剂510的实施例中,例如,添加剂可以是上文所列的化合物、下文所示出的以下化合物或具有类似化学结构的化合物中的一种。举例来说,添加剂可包括如下的含有醚基或端基的长烷基链:

[0057][0058]

其中r1可包括

‑

h、烷基链、甲基或叔丁基,r2可包括

‑

h、

‑

烷基链、甲基、叔丁基、

‑

oh、

‑

nh2、

‑

sh、

‑

f、

‑

cl、

‑

br、

‑

i或

‑

so3h,且其中n在约4到约200之间,但可使用任何合适的数目。

[0059]

在图10a中,一旦已放置介电层108,那么使用例如光刻掩模和刻蚀工艺来图案化介电层108以形成暴露部分穿孔416的开口424,或如果介电层108的材料是光敏的,则是曝光和显影介电层108的材料。

[0060]

在一些实施例中,能量来源将能量(如光)供应到介电层108以便诱发光敏剂的反应,所述光敏剂的反应又与第一重布线钝化层聚合物树脂反应以化学地改变能量撞击到介电层108的那些部分。在一实施例中,能量可以是电磁辐射,如g射线(具有约436纳米的波长)、i射线(具有约365纳米的波长)、紫外辐射、远紫外辐射、x射线、电子束或类似物。能量来源可以是电磁辐射的来源,且可以是krf准分子激光(具有248纳米的波长)、arf准分子激光(具有193纳米的波长)、f2准分子激光(具有157纳米的波长)或类似物,但也可利用任何其它合适的能量源,如汞蒸气灯、氙灯、碳弧灯或类似物。

[0061]

图案化掩模位于能量源与介电层108之间,以便在能量实际撞击在介电层108上之前阻挡能量的部分以形成图案化能量。在一实施例中,图案化掩模可包括一系列层(例如,

衬底、吸收层、抗反射涂层、屏蔽层等)以反射、吸收或以其它方式阻挡能量的部分到达不希望照射的介电层108的那些部分。通过以所希望的照射形状形成穿过图案化掩模的开口,可在图案化掩模中形成所需图案。

[0062]

在一些实施例中,介电层108放置在支撑板上。一旦图案已与介电层108对准,那么能量源产生所需能量(例如,光),所述能量在其到达介电层108的途中穿过图案化掩模。撞击在介电层108的部分上的图案化能量诱发介电层108内的光敏剂的反应。在一些实施例中,小于约250毫焦的曝光能量可用于诱发介电层108内的光敏剂的反应。这种减小的曝光能量可用于实现临界尺寸(如随后在重布线层中形成的导电特征的宽度)的较高分辨率。举例来说,为形成具有约7微米的宽度的开口424,可使用在约175毫焦到约225毫焦的范围内的曝光能量。光敏剂吸收图案化能量的化学反应产物(例如,酸/碱/自由基)随后与第二重布线钝化层聚合物树脂反应,在通过图案化掩模照射的那些部分中化学地更改介电层108。

[0063]

图10b示出根据一些实施例的聚合物前体500(如聚酰胺酸酯)与交联剂510之间的反应,所述反应可在曝光已经引发与光敏剂的反应之后发生。交联剂510形成将一个聚合物链连接到另一个聚合物链的键,例如在图10b中所示出的聚酰胺酸酯500的链,从而产生交联聚合物链520。所得交联聚合物链520可具有比没有交联时更大的刚性。

[0064]

在介电层108已曝光之后,可使用第一曝光后烘烤(post

‑

exposure bake;peb)以便辅助在曝光期间由能量对光敏剂的撞击所产生的酸/碱/自由基的产生、分散以及反应。这种辅助有助于产生或增强化学反应,所述化学反应在受能量撞击的那些区与不受能量撞击的那些区之间产生化学差异和不同的极性。这些化学差异还导致受能量撞击的区与不受能量撞击的那些区之间的溶解度的差异。在一些实施例中,可在约180毫焦到约350毫焦的范围内在一段时期将介电层108的温度升高到在约70℃到约120℃的范围内。

[0065]

一旦介电层108已曝光和烘烤,那么可使用显影剂对介电层108进行显影。在其中介电层108是低温固化的聚酰亚胺的实施例中,第一显影剂可以是如有机溶剂或临界流体的负型显影剂,所述负型显影剂可用于去除介电层108的未暴露于能量且由此保持它们的原始溶解度的那些部分。可利用的材料的具体实例包含烃类溶剂、醇溶剂、醚溶剂、酯溶剂、临界流体、这些的组合或类似物。可用于负型溶剂的材料的具体实例包含环戊酮(a515)、己烷、庚烷、辛烷、甲苯、二甲苯、二氯甲烷、氯仿、四氯化碳、三氯乙烯、甲醇、乙醇、丙醇、丁醇、临界二氧化碳、乙醚、二丙醚、二丁醚、乙基乙烯基醚、二恶烷、环氧丙烷、四氢呋喃、溶纤剂、甲基溶纤剂、丁基溶纤剂、甲基卡必醇、二乙二醇单乙醚、丙酮、甲基乙基酮、甲基异丁基酮、异佛尔酮、环己酮、乙酸甲酯、乙酸乙酯、乙酸丙酯、乙酸丁酯、吡啶、甲酰胺、n,n

‑

二甲基甲酰胺或类似物。

[0066]

可使用例如旋涂工艺将第一显影剂涂覆到介电层108。在这种工艺中,在旋转介电层108的同时,将第一显影剂从介电层108上方涂覆到介电层108。在一实施例中,第一显影剂可处于约20℃到约30℃的范围内的温度下,且显影可在约50秒到约70秒的范围内持续,这可有利于增加产量。

[0067]

然而,虽然本文中所描述的旋涂方法是用于在曝光之后显影介电层108的一种合适的方法,但其意欲是说明性的且不意欲限制实施例。更确切而言,可使用用于显影的任何合适的方法,包含浸渍方法、覆液方法、喷涂方法、这些的组合或类似方法。所有这些显影方法完全意欲包含在实施例的范围内。

[0068]

一旦介电层108已显影,那么可冲洗介电层108。在一实施例中,可用冲洗液体(如丙二醇单甲基醚乙酸酯)冲洗介电层108,但可使用任何合适的冲洗溶液,如水。

[0069]

在显影之后,可利用显影后烘烤工艺以帮助在显影工艺之后聚合和稳定介电层108。在一实施例中,可在约80℃到约200℃之间或在约80℃到约170℃之间的温度下执行显影后烘烤工艺约60秒到约300秒之间(如约2分钟)的时间。

[0070]

在显影后烘烤之后,可固化介电层108。在其中介电层108包括低温固化的聚酰亚胺的一些实施例中,可在约200℃到约300℃的范围内的温度下执行固化工艺。在其它实施例中,可在大于约300℃的温度下执行固化工艺。介电层108可固化约10分钟到约180分钟的范围内的时间。然而,可利用任何合适的温度和时间。

[0071]

图10c示出,热固化可将如上文关于图10b所示出的交联聚合物链520转换为聚酰亚胺链530。在一个实施例中,聚酰亚胺链530可最终具有具有下式的单体:

[0072][0073]

在一些实施例中,上述聚酰亚胺链530具有在约30000到约60000的范围内的分子量,这对于改进膜属性(如强度和抗分层性)可以是有利的。由于具有较小强度且对分层的敏感性更高,具有小于约30000的分子量的聚酰亚胺链可以是不利的。由于溶解度较差,具有大于约80000的分子量的聚酰亚胺链可以是不利的。聚酰亚胺链530可具有有更少酰亚胺环的聚酰亚胺主链,这可降低聚合物材料的耗散因子(df)且减少器件插入损耗。

[0074]

在一些实施例中,介电层108可包括额外的单体,而不是具有如上文关于聚酰亚胺链530所呈现的精确化学结构,所述额外的单体具有聚酰亚胺链530的单体或另外代替所呈现的精确单体。举例来说,在一些实施例中,介电层108可包括由以下化学式描述的一或多种单体:

[0075][0076]

在其它实施例中,介电层108可包括由式nh2‑

a

‑

nh2描述的一或多种单体,其中a表示单体的核心。由式nh2‑

a

‑

nh2描述的单体可包含以下化学结构:

[0077]

[0078]

[0079][0080]

在其中介电层108的聚合物材料在约230℃下固化的一些实施例中,介电层124的聚合物材料(如聚酰亚胺链530)在固化工艺之后具有有利的属性。聚合物材料在约60千兆赫时可具有约2.9的介电常数(dk),且在约60千兆赫时可具有在约0.007到约0.01的范围内的耗散因子(df)。可通过使用具有更少酰亚胺环的聚酰亚胺主链(如上文关于图10d所示出的聚酰亚胺链530)将聚合物材料的df降低到约0.007。具有在约0.003到约0.015的范围内的df可有益于减少器件插入损耗。在一些实施例中,可实现约100%的聚酰亚胺环化。

[0081]

聚合物材料可具有在约206℃到约216℃的范围内的热机械分析玻璃转化(thermomechanical analysis glass transition;tma

‑

tg)温度。聚合物材料可具有在约46百万分率/℃(ppm/℃)到约53ppm/℃或约48ppm/℃到约49ppm/℃的范围内的线性热膨胀系数(coefficient of linear thermal expansion;cte1)。如在约46ppm/℃到约53ppm/℃的范围内的较低cte1可有益于减少随后形成的重布线层(redistribution layers;rdl)中的断开的线,如下文关于图11所描述的金属化图案110。聚合物材料可具有在约157兆帕到约181兆帕或约168兆帕到约177兆帕的范围内的拉伸强度。聚合物材料可具有在约500牛顿每米到约800牛顿每米的范围内的粘合力。

[0082]

聚合物材料可具有在约3.7吉帕到约3.8吉帕的范围内的杨氏模量。如上文关于图10d所示出,可通过使用例如聚酰亚胺链530的聚酰亚胺主链在聚合物材料中实现约3.8吉帕的杨氏模量。具有约3.8吉帕的杨氏模量的较大刚性的聚合物材料可由于聚合物材料的增大的分子平坦度(molecular flatness)而有益于减小衬底应力。举例来说,管芯拐角上的焊点的衬底应力可从约1.0(其可引起不利分层)降低到约0.9。在随后形成的金属化层(如下文关于图11所描述的金属化图案110)的导电特征上的分层可通过聚合物材料的强度和刚性来降低,所述强度和刚性由约3.8吉帕的杨氏模量来显现。

[0083]

聚合物材料可具有在约74%到约86%或约80%到约85%的范围内的伸长百分比。介电层108可收缩到在约5微米到约20微米的范围内的厚度。

[0084]

图10d示出如图10a所示出的区400的详细视图,其绘示在图案化介电层108之后的开口424。在一些实施例中,可用约250毫焦的曝光能量、约10微米的深度、小于10微米的宽度w1(如在约3.9微米到约9.2微米的范围内)来图案化开口424。聚焦深度(depth of focus;dof)可大于约20微米。较低曝光能量可允许形成开口424的法线轮廓,以使得开口424的侧壁与介电层108的顶部表面之间所测量的角度α在小于约90

°

(如约80

°

到约90

°

)的范围内,这对于良好的晶种层覆盖可以是有利的。大于约90

°

的角度α可以是不利的,因为其可导致较差晶种层覆盖。

[0085]

图10e提供质量分析结果,所述质量分析结果示出在聚合物材料(例如聚酰亚胺)

中包含聚酰胺酸酯500的实施例的一个结果。在一些实施例中,在包括聚酰胺酸酯500的聚合物材料固化之后,图10e示出使用第三单体508(例如bapp)和第二反应物504以便形成在质子核磁共振谱中作为峰的聚合物材料。

[0086]

在图11中,随后形成金属化图案110。金属化图案110包含沿着介电层108的主表面延伸且延伸穿过介电层108从而以物理和电气方式耦合到穿孔416的导电元件。作为形成金属化图案110的实例,在介电层108上方和延伸穿过介电层108的开口中形成晶种层。在一些实施例中,晶种层是金属层,所述金属层可以是单个层或包括由不同材料形成的多个子层的复合层。在一些实施例中,晶种层包括钛层和在钛层上方的铜层。晶种层可使用例如pvd或类似操作来形成。随后在晶种层上形成光刻胶且图案化光刻胶。光刻胶可通过旋转涂布或类似操作而形成,且可暴露于光以用于图案化。光刻胶的图案对应于金属化图案146。图案化形成穿过光刻胶的开口以暴露晶种层。随后在光刻胶的开口中且在晶种层的暴露部分上形成导电材料。导电材料可通过镀覆(如电镀或化学镀)或类似方法形成。导电材料可包括金属,如铜、钛、钨、铝或类似物。

[0087]

导电材料和晶种层的下伏部分的组合形成金属化图案110,所述金属化图案110包含形成在开口424中的导通孔426。金属化图案110可具有约10微米的分辨率,如金属化图案110的导电特征具有约10微米或小于10微米的宽度和厚度。举例来说,导通孔426可具有约7微米的宽度,其通过使用约175毫焦到约225毫焦的范围内的较低曝光能量来实现。导通孔426可以物理和电气方式耦合到穿孔416。在一些实施例中,如上文关于图4所描述,一些导通孔426形成在附接到介电层408和/或金属化图案410的管芯(未示出)的管芯连接件上方且以物理和电气方式耦合到所述管芯连接件。去除光刻胶和晶种层上不形成导电材料的部分。可通过可接受的灰化或剥离工艺(如使用氧等离子或类似工艺)去除光刻胶。一旦将光刻胶去除,那么如通过使用可接受的刻蚀工艺(如通过湿式或干式刻蚀)来去除晶种层的暴露部分。

[0088]

金属化图案110也可包括如导电线的导电特征。介电层108的聚合物材料可提供较低cte1和较高粘合力,这可用于减少断开的导电线。这可将良率损失从约100%降低到约0%。

[0089]

在图12中,介电层112可形成在金属化图案110和介电层108上。如上文关于图8到图10所描述,可以与介电层108类似的方式形成和图案化介电层112。图案化形成暴露部分金属化图案110的开口。图案化可通过可接受的工艺形成,如通过当介电层112是光敏材料时将介电层112暴露于光或通过使用例如各向异性刻蚀进行刻蚀。如果介电层112是光敏材料,那么可在曝光之后使介电层112显影。

[0090]

出于说明性目的,图12示出具有两层单个金属化图案110和金属化图案422的重布线结构106。在一些实施例中,背侧重布线结构106可包含任何数目的介电层和金属化图案。如果将形成更多介电层和金属化图案,那么可重复上文论述的步骤和工艺。金属化图案可包含一或多个导电元件。导电元件可在金属化图案形成期间通过在下伏介电层的表面上方和在下伏介电层的开口中形成金属化图案的晶种层和导电材料来形成,由此互连和电耦合各种导电线。

[0091]

在图13中,将穿孔116形成在开口114中且远离背侧重布线结构106的最顶部介电层(例如,介电层425)延伸。作为形成穿孔116的实例,在背侧重布线结构106上方,例如在介

电层425和由开口114所暴露的金属化图案422的部分上形成晶种层(未绘示)。在一些实施例中,晶种层是金属层,所述金属层可以是单个层或包括由不同材料形成的多个子层的复合层。在特定实施例中,晶种层包括钛层和在钛层上方的铜层。晶种层可使用例如pvd或类似操作来形成。在晶种层上形成光刻胶且图案化光刻胶。光刻胶可通过旋转涂布或类似操作而形成,且可暴露于光以用于图案化。光刻胶的图案对应于导通孔。图案化形成穿过光刻胶的开口以暴露晶种层。导电材料形成在光刻胶的开口中和晶种层的暴露部分上。导电材料可通过镀覆(如电镀或化学镀)或类似方法形成。导电材料可包括金属,如铜、钛、钨、铝或类似物。去除光刻胶和晶种层上不形成导电材料的部分。可通过可接受的灰化或剥离工艺(如使用氧等离子或类似工艺)去除光刻胶。一旦将光刻胶去除,那么如通过使用可接受的刻蚀工艺(如通过湿式或干式刻蚀)来去除晶种层的暴露部分。晶种层和导电材料的剩余部分形成穿孔116。

[0092]

在图14中,将集成电路管芯50(例如,第一集成电路管芯50a和第二集成电路管芯50b)通过粘合剂118粘合到介电层425。所需类型和数量的集成电路管芯50粘合在封装区100a和封装区100b中的每一个中。在所绘示的实施例中,多个集成电路管芯50彼此相邻地粘合,所述多个集成电路管芯50包含第一封装区100a和第二封装区100b中的每一个中的第一集成电路管芯50a和第二集成电路管芯50b。第一集成电路管芯50a可以是逻辑器件,如中央处理单元(cpu)、图形处理单元(gpu)、系统芯片(soc)、微控制器或类似物。第二集成电路管芯50b可以是存储器器件,如动态随机存取存储器(dram)管芯、静态随机存取存储器(sram)管芯、混合存储器立方体(hmc)模块、高带宽存储器(hbm)模块或类似物。在一些实施例中,集成电路管芯50a和集成电路管芯50b可以是相同类型的管芯,如soc管芯。第一集成电路管芯50a和第二集成电路管芯50b可在相同技术节点的工艺中形成,或可在不同技术节点的工艺中形成。举例来说,第一集成电路管芯50a可具有比第二集成电路管芯50b更高级的工艺节点。集成电路管芯50a和集成电路管芯50b可具有不同尺寸(例如,不同高度和/或表面积),或可具有相同尺寸(例如,相同高度和/或表面积)。在第一封装区100a和第二封装区100b中的可用于穿孔116的空间可能是有限的,特别是当集成电路管芯50包含具有大占据面积的器件(如soc)时。当第一封装区100a和第二封装区100b具有可用于穿孔116的有限空间时,使用背侧重布线结构106可以改进内连线布置。

[0093]

粘合剂118位于集成电路管芯50的背侧上,且将集成电路管芯50粘合到背侧重布线结构106,如粘合到介电层425。粘合剂118可以是任何合适的粘合剂、环氧树脂、管芯贴合膜(die attach film;daf)或类似物。粘合剂118可涂覆到集成电路管芯50的背侧,如果不利用背侧重布线结构106,那么可涂覆在载体衬底102的表面上方,或如果可适用,那么可涂覆到背侧重布线结构106的上部表面。举例来说,可在单体化以分离集成电路管芯50之前将粘合剂118涂覆到集成电路管芯50的背侧。

[0094]

在图15中,将密封体120形成在各种组件上和周围。在形成之后,密封体120密封穿孔116和集成电路管芯50。密封体120可以是模制化合物、环氧树脂或类似物。密封体120可通过压缩模制、转移模制或类似方法来涂覆,且可形成在载体衬底102上方,以使得掩埋或覆盖穿孔116和/或集成电路管芯50。密封体120进一步形成在集成电路管芯50之间的间隔区中。密封体120可以液体或半液体形式涂覆且随后相继固化。

[0095]

在图16中,对密封体120执行平坦化工艺以暴露穿孔116和管芯连接件66。平坦化

工艺也可去除穿孔116、介电层68和/或管芯连接件66的材料,直到暴露管芯连接件66和穿孔116。在工艺变化内的平坦化工艺之后,穿孔116、管芯连接件66、介电层68以及密封体120的顶部表面大体上共面。平坦化工艺可以是例如化学机械抛光(cmp)、研磨工艺或类似工艺。在一些实施例中,例如,如果穿孔116和/或管芯连接件66已暴露,那么可省略平坦化。

[0096]

在图17到图20中,将前侧重布线结构122(参见图20)形成在密封体120、穿孔116以及集成电路管芯50上方。前侧重布线结构122包含介电层124、介电层128、介电层132以及介电层136;以及金属化图案126、金属化图案130以及金属化图案134。金属化图案也可称为重布线层或重布线线路。将前侧重布线结构122绘示为具有三层金属化图案的实例。更多或更少介电层和金属化图案可形成在前侧重布线结构122中。如果将形成更少介电层和金属化图案,那么可省略下文论述的步骤和工艺。如果将形成更多介电层和金属化图案,那么可重复下文论述的步骤和工艺。

[0097]

在图17中,将介电层124沉积在密封体120、穿孔116以及管芯连接件66上。在一些实施例中,介电层124由可使用光刻掩模来图案化的光敏材料形成,所述光敏材料如pbo、聚酰亚胺、bcb或类似物。介电层124可通过旋转涂布、层压、cvd、类似方法或其组合形成。随后图案化介电层124。图案化形成暴露部分穿孔116和部分管芯连接件66的开口。图案化可通过可接受的工艺来进行,如通过当介电层124是感光性材料时曝光和显影介电层124或通过使用例如各向异性刻蚀进行刻蚀。

[0098]

随后形成金属化图案126。金属化图案126包含沿着介电层124的主表面延伸且延伸穿过介电层124从而以物理和电气方式耦合到穿孔116和集成电路管芯50的导电元件。作为形成金属化图案126的实例,在介电层124上方和延伸穿过介电层124的开口中形成晶种层。在一些实施例中,晶种层是金属层,所述金属层可以是单个层或包括由不同材料形成的多个子层的复合层。在一些实施例中,晶种层包括钛层和在钛层上方的铜层。晶种层可使用例如pvd或类似操作来形成。随后在晶种层上形成光刻胶且图案化光刻胶。光刻胶可通过旋转涂布或类似操作而形成,且可暴露于光以用于图案化。光刻胶的图案对应于金属化图案126。图案化形成穿过光刻胶的开口以暴露晶种层。随后在光刻胶的开口中且在晶种层的暴露部分上形成导电材料。导电材料可通过镀覆(如电镀或化学镀)或类似方法形成。导电材料可包括金属,如铜、钛、钨、铝或类似物。晶种层的导电材料和下伏部分的组合形成金属化图案126。去除光刻胶和晶种层上不形成导电材料的部分。可通过可接受的灰化或剥离工艺(如使用氧等离子或类似工艺)去除光刻胶。一旦将光刻胶去除,那么如通过使用可接受的刻蚀工艺(如通过湿式或干式刻蚀)来去除晶种层的暴露部分。

[0099]

在图18中,将介电层128沉积在金属化图案126和介电层124上。介电层128可以与介电层124类似的方式来形成,且可由与介电层124类似的材料形成。

[0100]

随后形成金属化图案130。金属化图案130包含位于介电层128的主表面上且沿着所述主表面延伸的部分。金属化图案130更包含延伸穿过介电层128从而以物理和电气方式耦合金属化图案126的部分。金属化图案130可以与金属化图案126类似的方式和类似的材料形成。在一些实施例中,金属化图案130具有与金属化图案126不同的尺寸。举例来说,金属化图案130的导电线和/或通孔可比金属化图案126的导电线和/或通孔更宽或更厚。另外,金属化图案130可形成为比金属化图案126更大的间距。

[0101]

在图19中,介电层132沉积在金属化图案130和介电层128上。介电层132可以与介

电层124类似的方式来形成,且可由与介电层124类似的材料形成。

[0102]

随后形成金属化图案134。金属化图案134包含位于介电层132的主表面上且沿着所述主表面延伸的部分。金属化图案134更包含延伸穿过介电层132从而以物理和电气方式耦合金属化图案130的部分。金属化图案134可以与金属化图案126类似的方式和类似的材料形成。金属化图案134是前侧重布线结构122的最顶部金属化图案。如此,前侧重布线结构122的所有中间金属化图案(例如金属化图案126和金属化图案130)安置在金属化图案134与集成电路管芯50之间。在一些实施例中,金属化图案134具有与金属化图案126和金属化图案130不同的尺寸。举例来说,金属化图案134的导电线和/或通孔可比金属化图案126和金属化图案130的导电线和/或通孔更宽或更厚。另外,金属化图案134可形成为比金属化图案130更大的间距。

[0103]

在图20中,将介电层136沉积在金属化图案134和介电层132上。介电层136可以与介电层124类似的方式来形成,且可由与介电层124相同的材料形成。介电层136是前侧重布线结构122的最顶部介电层。如此,前侧重布线结构122的所有金属化图案(例如,金属化图案126、金属化图案130以及金属化图案134)安置在介电层136与集成电路管芯50之间。另外,前侧重布线结构122的所有中间介电层(例如,介电层124、介电层128、介电层132)安置在介电层136与集成电路管芯50之间。

[0104]

在图21中,形成ubm 138以用于与前侧重布线结构122的外部连接。ubm 138具有在介电层136的主表面上且沿着所述主表面延伸的凸块部分,且具有延伸穿过介电层136从而以物理和电气方式耦合金属化图案134的通孔部分。因此,ubm 138电耦合到穿孔116和集成电路管芯50。ubm 138可由与金属化图案126相同的材料形成。在一些实施例中,ubm 138具有与金属化图案126、金属化图案130以及金属化图案134不同的尺寸。

[0105]

在图22中,导电连接件150形成在ubm 138上。导电连接件150可以是球栅阵列(ball grid array;bga)连接件、焊料球、金属柱、受控塌陷芯片连接(controlled collapse chip connection;c4)凸块、微凸块、无电镀镍钯浸金技术(electroless nickel

‑

electroless palladium

‑

immersion gold technique;enepig)形成的凸块或类似物。导电连接件150可包含导电材料,如焊料、铜、铝、金、镍、银、钯、锡、类似物或其组合。在一些实施例中,导电连接件150首先通过蒸镀、电镀、印刷、焊料转移、植球或类似方法形成焊料层来形成。一旦已在结构上形成焊料层,便可执行回焊以便使材料成形为所需凸块形状。在另一实施例中,导电连接件150包括通过溅镀、印刷、电镀、化学镀、cvd或类似操作形成的金属柱(如铜柱)。金属柱可无焊料且具有大体上竖直侧壁。在一些实施例中,在金属柱的顶部上形成金属顶盖层。金属顶盖层可包含镍、锡、锡铅、金、银、钯、铟、镍钯金、镍金、类似物或其组合,且可通过镀覆工艺形成。

[0106]

在图23中,执行载体衬底剥离以将载体衬底102与背侧重布线结构106(例如,介电层108)分离(或“剥离”)。根据一些实施例,剥离包含在释放层104上投射光(如激光或uv光),以使得释放层104在光的热量下分解,且可去除载体衬底102。随后将结构翻转且放置在胶带(未绘示)上。

[0107]

在图24中,形成导电连接件152以延伸穿过介电层408,进而接触金属化图案410。形成开口以穿过介电层408,进而暴露出部分金属化图案410。开口可例如使用激光钻孔、刻蚀或类似方法形成。将导电连接件152形成在开口中。在一些实施例中,导电连接件152包括

助焊剂且在助焊剂浸渍工艺中形成。在一些实施例中,导电连接件152包括如焊膏、银膏或类似物的导电膏,且在印刷工艺中分配。在一些实施例中,导电连接件152以与导电连接件150类似的方式形成,且可由与导电连接件150类似的材料形成。

[0108]

图25和图26示出根据一些实施例的器件堆叠的形成和实施。器件堆叠由形成在第一封装组件100中的集成电路封装形成。器件堆叠也可称为叠层封装(package

‑

on

‑

package;pop)结构。

[0109]

在图25中,第二封装组件200耦合到第一封装组件100。第二封装组件200中的一个在封装区100a和封装区100b中的每一个中耦合以在第一封装组件100的每个区中形成集成电路器件堆叠。

[0110]

第二封装组件200包含例如衬底202和耦合到衬底202的一或多个堆叠管芯210(例如,210a和210b)。虽然示出一组堆叠管芯210(210a和210b),但在其它实施例中,可将多个堆叠管芯210(各自具有一或多个堆叠管芯)并排安置成耦合到衬底202的同一表面。衬底202可由半导体材料制成,如硅、锗、金刚石或类似物。在一些实施例中,也可使用化合物材料,如硅锗、碳化硅、砷化镓、砷化铟、磷化铟、碳化硅锗、磷化镓砷、磷化镓铟、这些的组合以及类似物。此外,衬底202可以是绝缘体上硅(silicon

‑

on

‑

insulator;soi)衬底。一般来说,soi衬底包含如外延硅、锗、硅锗、soi、绝缘体上硅锗(silicon germanium on insulator;sgoi)或其组合的半导体材料层。在一个替代实施例中,衬底202基于绝缘芯,如玻璃纤维增强的树脂芯。一种实例芯材料是玻璃纤维树脂,如fr4。芯材料的替代物包含双马来酰亚胺

‑

三嗪(bismaleimide

‑

triazine;bt)树脂,或替代地,其它印刷电路板(printed circuit board;pcb)材料或膜。如味之素堆积膜(ajinomoto build

‑

up film;abf)的堆积膜或其它层压体可用于衬底202。

[0111]

衬底202可包含有源器件和无源器件(未绘示)。如晶体管、电容器、电阻器、这些的组合以及类似物的广泛多种器件可用于产生第二封装组件200的设计的结构和功能要求。可使用任何合适的方法来形成器件。

[0112]

衬底202也可包含金属化层(未绘示)和导通孔208。金属化层可形成在有源器件和无源器件上方,且设计成连接各种器件以形成功能电路。金属化层可由具有使导电材料层互连的通孔的介电材料(例如,低k介电材料)和导电材料(例如,铜)的交替层形成,且可通过任何合适的工艺(如沉积、镶嵌、双重镶嵌或类似工艺)形成。在一些实施例中,衬底202大体上不含有源器件和无源器件。

[0113]

衬底202可在衬底202的第一侧上具有接合衬垫204以耦合到堆叠管芯210,且在衬底202的第二侧上具有接合衬垫206以耦合到导电连接件152,第二侧与衬底202的第一侧相对。在一些实施例中,通过在衬底202的第一侧和第二侧上的介电层(未绘示)中形成凹部(未绘示)来形成接合衬垫204和接合衬垫206。可形成凹部以允许接合衬垫204和接合衬垫206嵌入到介电层中。在其它实施例中,由于可在介电层上形成接合衬垫204和接合衬垫206,因此省略凹部。在一些实施例中,接合衬垫204和接合衬垫206包含由铜、钛、镍、金、钯、类似物或其组合制成的薄晶种层(未绘示)。接合衬垫204和接合衬垫206的导电材料可沉积在薄晶种层上方。导电材料可通过电化学镀覆工艺、化学镀工艺、cvd、原子层沉积(atomic layer deposition;ald)、pvd、类似工艺或其组合来形成。在一实施例中,接合衬垫204和接合衬垫206的导电材料是铜、钨、铝、银、金、类似物或其组合。

[0114]

在一些实施例中,接合衬垫204和接合衬垫206是包含导电材料的三个层(如钛层、铜层以及镍层)的ubm。材料和层的其它布置(如铬/铬铜合金/铜/金的布置、钛/钛钨/铜的布置或铜/镍/金的布置)可用于形成接合衬垫204和接合衬垫206。可用于接合衬垫204和接合衬垫206的任何合适的材料或材料层完全意欲包含在本技术的范围内。在一些实施例中,导通孔208延伸穿过衬底202且将接合衬垫204中的至少一个耦合到接合衬垫206中的至少一个。

[0115]

在所示出的实施例中,堆叠管芯210通过线接合(wire bonds)212耦合到衬底202,但可使用其它连接,如导电凸块。在一实施例中,堆叠管芯210是堆叠存储器管芯。举例来说,堆叠管芯210可以是存储器管芯,如低功率(low

‑

power;lp)双数据速率(double data rate;ddr)存储器模块,如lpddr1、lpddr2、lpddr3、lpddr4或类似存储器模块。

[0116]

堆叠管芯210和线接合212可由模制材料214密封。模制材料214可例如使用压缩模制在堆叠管芯210和线接合212上模制。在一些实施例中,模制材料214是模制化合物、聚合物、环氧树脂、氧化硅填充物材料、类似物或其组合。可执行固化工艺以固化模制材料214;固化工艺可以是热固化、uv固化、类似工艺或其组合。

[0117]

在一些实施例中,堆叠管芯210和线接合212掩埋在模制材料214中,且在模制材料214固化之后,执行如研磨的平坦化步骤以去除模制材料214的多余部分且为第二封装组件200提供大体上平坦表面。

[0118]

在形成第二封装组件200之后,借助于导电连接件152、接合衬垫206以及背侧重布线结构106的金属化图案将第二封装组件200以机械和电气方式接合到第一封装组件100。在一些实施例中,堆叠管芯210可通过线接合212、接合衬垫204和接合衬垫206、导通孔208、导电连接件152、金属化图案410、穿孔416、背侧重布线结构106、穿孔116以及前侧重布线结构122耦合到集成电路管芯50a和集成电路管芯50b。

[0119]

在一些实施例中,在衬底202的与堆叠管芯210相对的侧上形成阻焊剂(未绘示)。导电连接件152可安置在阻焊剂中的开口中,从而以电气和机械方式耦合到衬底202中的导电特征(例如,接合衬垫206)。阻焊剂可用于保护衬底202的区域免受外部损坏。

[0120]

在一些实施例中,在用将第二封装组件200附接到第一封装组件100之后所剩余的环氧树脂助焊剂的环氧树脂部分中的至少一些进行回焊之前,导电连接件152可具有形成于其上的环氧树脂助焊剂(未绘示)。

[0121]

在一些实施例中,在第一封装组件100与第二封装组件200之间形成底部填充物(未绘示)从而包围导电连接件152。底部填充物可减小应力且保护由对导电连接件152的回焊而产生的接合部。底部填充物可在附接第二封装组件200之后通过毛细流动工艺形成,或可在附接第二封装组件200之前通过合适的沉积方法形成。在形成环氧树脂助焊剂的实施例中,其可充当底部填充物。

[0122]

在图26中,通过沿着切割道区(例如,在第一封装区100a与第二封装区100b之间)锯切来执行单体化工艺。锯切将第一封装区100a与第二封装区100b单体化。所得的单体化器件堆叠来自第一封装区100a或第二封装区100b中的一个。在一些实施例中,在第二封装组件200耦合到第一封装组件100之后,执行单体化工艺。在其它实施例(未绘示)中,在第二封装组件200耦合到第一封装组件100之前(如在剥离载体衬底102且形成导电连接件152之后)执行单体化工艺。

[0123]

随后可使用导电连接件150将每一单体化第一封装组件100安装到封装衬底300。封装衬底300包含衬底芯302和在衬底芯302上方的接合衬垫304。衬底芯302可由如硅、锗、金刚石或类似物的半导体材料制成。替代地,也可使用化合物材料,如硅锗、碳化硅、砷化镓、砷化铟、磷化铟、碳化硅锗、磷化镓砷、磷化镓铟、这些的组合以及类似物。此外,衬底芯302可以是soi衬底。一般来说,soi衬底包含如外延硅、锗、硅锗、soi、sgoi或其组合的半导体材料层。在一个替代实施例中,衬底芯302基于绝缘芯,如玻璃纤维增强的树脂芯。一种实例芯材料是玻璃纤维树脂,如fr4。芯材料的替代物包含双马来酰亚胺

‑

三嗪bt树脂,或替代地,其它pcb材料或膜。如abf的堆积膜或其它层压体可用于衬底芯302。

[0124]

衬底芯302可包含有源器件和无源器件(未绘示)。如晶体管、电容器、电阻器、这些的组合以及类似物的广泛多种器件可用于产生器件堆叠的设计的结构和功能要求。可使用任何合适的方法来形成器件。

[0125]

衬底芯302也可包含金属化层和通孔(未绘示),其中接合衬垫304以物理和/或电气方式耦合到金属化层和通孔。金属化层可形成在有源器件和无源器件上方,且设计成连接各种器件以形成功能电路。金属化层可由具有使导电材料层互连的通孔的介电材料(例如,低k介电材料)和导电材料(例如,铜)的交替层形成,且可通过任何合适的工艺(如沉积、镶嵌、双重镶嵌或类似工艺)形成。在一些实施例中,衬底芯302大体上不含有源器件和无源器件。

[0126]

在一些实施例中,对导电连接件150进行回焊以将第一封装组件100附接到接合衬垫304。导电连接件150将封装衬底300(包含衬底芯302中的金属化层)以电气和/或物理方式耦合到第一封装组件100。在一些实施例中,阻焊剂(solder resist)306形成在衬底芯302上。导电连接件150可安置在阻焊剂306中的开口中,从而以电气和机械方式耦合到接合衬垫304。阻焊剂306可用于保护衬底芯302的区域免受外部损坏。

[0127]

在用将第一封装组件100附接到封装衬底300之后所剩余的环氧树脂助焊剂的环氧树脂部分中的至少一些进行回焊之前,导电连接件150可具有形成于其上的环氧树脂助焊剂(未绘示)。这一剩余环氧树脂部分可充当底部填充物以减小应力且保护由对导电连接件150进行回焊所产生的接合部。在一些实施例中,底部填充物308可在第一封装组件100与封装衬底300之间形成且包围导电连接件150。底部填充物308可在附接第一封装组件100之后通过毛细流动工艺形成,或可在附接第一封装组件100之前通过合适的沉积方法形成。

[0128]

在一些实施例中,无源器件(例如,表面安装器件(surface mount device;smd),未绘示)也可附接到第一封装组件100(例如,附接到ubm 138)或附接到封装衬底300(例如,附接到接合衬垫304)。举例来说,无源器件可接合到第一封装组件100或封装衬底300的与导电连接件150相同的表面。无源器件可在将第一封装组件100安装在封装衬底300上之前附接到封装组件100,或者可在将第一封装组件100安装在封装衬底300上之前或之后附接到封装衬底300。

[0129]

第一封装组件100可在其它器件堆叠中实现。举例来说,绘示pop结构,但第一封装组件100也可在倒装芯片球栅阵列(flip chip ball grid array;fcbga)封装中实施。在此类实施例中,第一封装组件100安装到如封装衬底300的衬底,但省略第二封装组件200。替代地,可将封盖或散热器附接到第一封装组件100。当省略第二封装组件200时,也可省略金属化图案410、穿孔416、背侧重布线结构106以及穿孔116。

[0130]

虽然将聚合物材料形成和图案化工艺描述为形成和图案化介电层108的一个可能实施例,但用于介电层108的聚合物材料形成和图案化工艺的实例意欲为说明性的且不旨在限制。更确切而言,聚合物材料形成和图案化工艺可用于形成和/或图案化的任何合适的介电层,如如上文关于图3所描述的介电层408和如上文关于图20所描述的前侧重布线结构122的介电层124。所有这些工艺完全旨在包含在实施例的范围内。

[0131]

还可包含其它特征和工艺。举例来说,可包含测试结构以辅助对3d封装或3dic器件的校验测试。测试结构可包含例如形成在重布线层中或衬底上的测试衬垫,所述测试衬垫允许对3d封装或3dic的测试、对探针和/或探针卡的使用以及类似操作。可对中间结构以及最终结构执行校验测试。另外,本文中所公开的结构和方法可与并有已知良好管芯的中间校验的测试方法结合使用以增大良率且降低成本。

[0132]

实施例可实现优势。如低温固化的聚酰亚胺的聚合物材料可用于形成器件的介电层,如集成扇出型(info)封装。可通过使用具有更少酰亚胺环的聚酰亚胺主链来降低聚合物材料的耗散因子(df),这可用于减少器件插入损耗。由于具有较高杨氏模量,聚酰亚胺主链可减少焊点对衬底的应力,如在管芯拐角处。聚合物材料可提供较低热膨胀系数和较高粘合力,这可用于减少断开的导电线且减少所得的良率损失。聚合物材料可在较低曝光能量下显影,这可用于实现临界尺寸(如重布线层中的导电特征的宽度)的较高分辨率。聚合物材料可在更短时间间隔内显影,这可用于增加产量。

[0133]

根据实施例,制造半导体器件的方法包含在衬底上方放置聚合物材料,图案化聚合物材料以及在200℃到300℃的范围内的温度下固化聚合物材料。聚合物材料包含聚合物前体,所述聚合物前体包含

[0134][0135]

其中r表示

[0136][0137]

光敏剂和溶剂。在一实施例中,聚合物材料包含在20重量%到40重量%的范围内的聚合物前体。在一实施例中,聚合物材料包含在1重量%到8重量%的范围内的光敏剂。在一实施例中,光敏剂包含二苯甲酰基甲烷。在一实施例中,光敏剂包含2,2'

‑

(苯基亚氨基)二乙醇。在一实施例中,聚合物材料更包含在1重量%到5重量%的范围内的交联剂。在一实施例中,交联剂包含四乙二醇二甲基丙烯酸酯。在一实施例中,溶剂包含1

‑

甲基

‑2‑

吡咯烷酮(nmp),聚合物材料包含在45重量%到55重量%的范围内的nmp。在一实施例中,溶剂包含乳酸乙酯(el),聚合物材料包含在10重量%到15重量%的范围内的el。

[0138]

根据另一实施例,制造半导体器件的方法包含:形成聚合物前体;形成聚合物混合物,聚合物混合物包含聚合物前体和溶剂;将聚合物混合物施加在衬底上方;曝光和显影聚合物混合物的至少一部分以形成显影的介电质;固化显影的介电质以形成介电层;以及在介电层上方形成导电特征。形成聚合物前体包含使3,3,4,4

‑

联苯四甲酸二酐与第一反应物反应以形成第二反应物,且使第二反应物与2,2

‑

双[4

‑

(4

‑

氨基苯氧基)苯基]丙烷(bapp)反

应以形成聚合物前体。在一实施例中,聚合物混合物更包含交联剂。在一实施例中,在曝光和显影聚合物混合物的至少部分期间,交联剂与聚合物前体反应以形成交联聚合物链。在一实施例中,固化介电层包含热固化,热固化将交联聚合物链转换为具有以下结构的聚酰亚胺

[0139][0140]

在一实施例中,介电层在约60千兆赫时的耗散因子在0.007到0.01的范围内。在一实施例中,介电层的杨氏模量(young's modulus)在3.7吉帕到3.8吉帕的范围内。在一实施例中,介电层的介电常数约为2.9。在一实施例中,介电层的拉伸强度在157兆帕到181兆帕的范围内。

[0141]

根据又另一实施例,半导体封装包含:第一密封体,位于第一介电层上,所述第一密封体密封第一穿孔;以及第一重布线结构,位于第一密封体和第一穿孔上方。第一重布线结构包含:第二介电层,所述第二介电层在60千兆赫时的耗散因子在0.007到0.01的范围内的耗散因子且所述第二介电层的杨氏模量在3.7吉帕到3.8吉帕的范围内;以及第一金属化图案,位于第二介电层上,所述第一金属化图案以物理和电气方式耦合第一穿孔。在一实施例中,半导体封装更包含:管芯,位于第一重布线结构上;第二穿孔,位于第一重布线结构上;第二密封体,位于第一重布线结构上,第二密封体密封管芯和第二穿孔;以及第二重布线结构,位于第二密封体、管芯以及第二穿孔上方。第二重布线结构包含:第三介电层和在第三介电层上的第二金属化图案,第二金属化图案以物理和电气方式耦合管芯和第二穿孔。在一实施例中,第二介电层包含以下结构

[0142][0143]

前文概述若干实施例的特征,以使得本领域的技术人员可更好地理解本公开的各方面。本领域的技术人员应了解,其可容易地将本公开用作设计或修改用于实施本文中所引入的实施例的相同目的和/或实现相同优势的其它工艺和结构的基础。本领域的技术人员还应认识到,此类等效构造并不脱离本公开的精神和范围,且其可在不脱离本公开的精神和范围的情况下在本文中进行各种改变、替代以及更改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。