1.所公开的实施例一般地涉及半导体存储器器件,更具体地涉及具有低编程和擦除电压以及改善的可靠性的非易失性存储器。

背景技术:

2.即使关闭电源,非易失性存储器器件仍能保留所存储的数据。非易失性存储器目前有若干种形式,其中包括电可擦可编程只读存储器(eeprom)和闪速eeprom。当前的闪速存储器架构利用存储器晶体管,该存储器晶体管具有位于半导体衬底上方的栅电极以及位于栅电极与半导体衬底之间的电介质层。衬底中的漏极区可以邻近存储器晶体管的电介质层,并且衬底中的源极区可以邻近电介质层的与漏极区相反的一侧。栅电极可以是浮栅。可使用耦接到栅电极的n阱电容器来偏置浮栅。

3.对存储器器件进行编程可导致电子存储在浮栅中,并且擦除存储器器件可以排出存储在浮栅中的电子。在编程期间,可将高于9v的高电压施加到n阱电容器和存储器晶体管的漏极。可将较低电压施加到存储器晶体管的源极,并且可以使半导体衬底接地。可以在源极与漏极之间的沟道区中产生垂直取向的强电场,从而导致热电子从沟道区注入到浮栅的边缘部分。在擦除期间,可将高于9v的高电压施加到漏极。n阱电容器、源极和衬底可以接地。可通过带间隧穿(btb)在漏极区中产生电子空穴对。所产生的空穴可通过横向电场朝着源极与漏极之间的沟道区加速,并且这些空穴中一些可获得高能量。热空穴可通过电介质层注入到浮栅中,并且与存储在浮栅中的电子复合。

4.由于编程和擦除操作需要高电压,因此低电压器件(例如3v或5v器件)会面临挑战,因为高电压通常由电荷泵电路产生,而电荷泵电路由低电压器件(例如3v或5v器件)构成。由于n阱电容器接地,因此擦除机制效率很低。n阱电容器可以邻近p衬底。无法向n阱电容器施加负电压以提高擦除效率,因为这样做可能会在n阱电容器与相邻的p衬底之间引起不希望的正向偏置电流。因此,迫切需要一种改进的闪速存储器器件结构来克服上述挑战。

技术实现要素:

5.在本公开的一方面,提供了一种非易失性存储器器件。所述器件包括存储器晶体管。第一电容器被耦接到所述存储器晶体管。第二电容器被耦接到所述存储器晶体管。所述第二电容器包括第一电极和第二电极。所述第二电容器的所述第二电极连接到输入端子。

6.在本公开的另一方面,提供了一种非易失性存储器器件。所述器件包括存储器晶体管,所述存储器晶体管包括栅电极。第一电容器被耦接到所述存储器晶体管的所述栅电极;第二电容器被耦接到所述存储器晶体管的所述栅电极。所述第二电容器包括第一电极、邻近所述第一电极的绝缘层和邻近所述绝缘层的第二电极。所述第二电容器的所述第二电极连接到输入端子。

7.在本公开的又一方面,提供了一种制造非易失性存储器器件的方法。所述方法包括提供存储器晶体管。提供耦接到所述存储器晶体管的第一电容器。提供耦接到所述存储

器晶体管的第二电容器。所述第二电容器包括第一电极和第二电极。所述第二电容器的所述第二电极连接到输入端子。

8.从下面描述的实施例中可以获得许多优点。第二电容器允许独立地控制施加到存储器晶体管的栅电极的电压,并且允许提高编程和擦除效率。栅电极可以是浮栅。在擦除操作期间向第二电容器施加负电压可降低擦除偏压并提高擦除效率。在编程操作期间向第二电容器施加正电压可降低编程偏压并提高编程效率。第二电容器通过增大存储器器件的耦合比来提高编程效率。术语“浮栅”可以指被绝缘体围绕的栅电极。术语“耦合比”可以指示从n阱电容器和第二电容器到浮栅的电压传输能力。第二电容器可被定位在浮栅上方,从而形成紧凑的非易失性存储器器件。

附图说明

9.通过阅读结合附图进行的以下详细描述,将更好地理解所公开的实施例:

10.图1a是根据本公开的实施例的非易失性存储器器件的示意图。

11.图1b是根据本公开的实施例的非易失性存储器器件的电路图。

12.图2是根据本公开的实施例的非易失性存储器器件的阵列的俯视图。

13.图3a是根据本公开的另外实施例的非易失性存储器器件的阵列的俯视图。

14.图3b是根据本公开的另外实施例的沿图3a的剖面线x

‑

x’截取的非易失性存储器器件的一部分的截面图。

15.图4是根据本公开的另外实施例的沿图3a的剖面线x

‑

x’截取的非易失性存储器器件的截面图。

16.图5和图6示出了根据本公开的实施例的图2所示的非易失性存储器器件的制造工艺流程。

17.图7至图10示出了根据本公开的另外实施例的图4所示的非易失性存储器器件的制造工艺流程。

18.为了图示的简单和清楚,附图图示了一般的构造方式,并且可以省略公知的特征和技术的特定描述和细节,以避免不必要地使所描述的器件的实施例的讨论模糊不清。另外,附图中的元素不一定按比例绘制。例如,附图中的一些元素的尺寸可能相对于其他元素被放大,以帮助提高对器件的实施例的理解。不同附图中的相同参考标号表示相同的元素,而相似的参考标号可以但不一定表示相似的元素。

具体实施方式

19.以下详细描述本质上是示例性的,并非旨在限制器件或者器件的应用和用途。此外,不旨在受到这些器件的先前背景或以下详细描述中提出的任何理论的束缚。

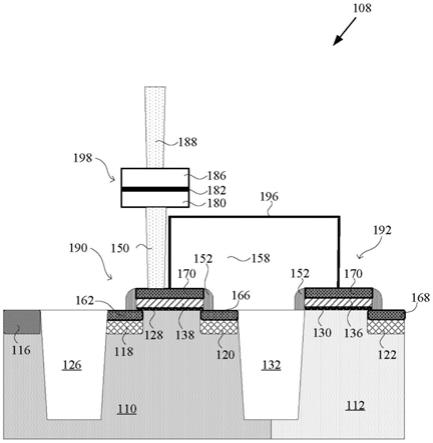

20.图1a是根据本公开的实施例的非易失性存储器器件108的示意图。在实施例中,非易失性存储器器件108可以是eeprom器件或闪速存储器eeprom器件。参考图1a,存储器器件108包括存储器晶体管190和第一电容器192。包括栅电极138的存储器晶体管190通过电连接196而耦接到第一电容器192,如图1a中的简化线所示。作为非限制性示例,第一电容器192可以是n阱电容器,该n阱电容器可以耦接到存储器晶体管190的栅电极138。第二电容器198可以耦接到存储器晶体管190。第二电容器198包括第一电极180、邻近第一电极180的绝

缘层182和邻近绝缘层182的第二电极186。第二电容器198的第一电极180可以通过第一导电接触150而耦接到存储器晶体管190的栅电极138。第二电容器198的第二电极186可以通过第二导电接触188连接到输入端子。第一电容器192和第二电容器198可以连接到分隔开的输入端子,以独立地控制存储器晶体管190。

21.在实施例中,第二电容器198的第一电极180和第二电极186可以包括金属材料,例如氮化钛(tin)或铜(cu)。绝缘层182可以由二氧化硅、氮化硅、高介电常数材料(例如二氧化铪((hfo2)、氧化铝(al2o3)),任何其他合适的绝缘材料或其组合制成。第二电容器198的第一电极180和第二电极186可以形成在存储器晶体管190的栅电极138上方。硅化物层170可以形成在第一导电接触150与栅电极138之间。存储器晶体管190的栅电极138可以是浮栅。在实施例中,栅电极138可以由掺杂的多晶硅制成。

22.存储器晶体管190可以包括位于存储器晶体管190的栅电极138下方的半导体衬底110。半导体衬底110可以是p掺杂的并且包括p阱。可以将存储器晶体管190的电介质层128置于栅电极138与半导体衬底110之间。存储器晶体管190的漏极120可以形成在半导体衬底110中,邻近电介质层128。存储器晶体管190的源极118可以形成在半导体衬底110中,邻近电介质层128的与存储器晶体管190的漏极120相反的一侧。可以在存储器晶体管190的源极118上方形成硅化物层162,并且可以在存储器晶体管190的漏极120上方形成硅化物层166。可以在硅化物层162、166上方形成导电接触(未示出),并且可以将导电接触连接到外部输入端子以偏置源极118和漏极120。在一个实施例中,外部输入端子可以与电容器198的输入端子不同。包括衬底端子116的p 掺杂的半导体区域可以形成在半导体衬底中,并且通过浅沟槽隔离(sti)结构126而与源极区118分隔开。

23.n阱电容器192可以包括邻近半导体衬底110的n阱112。可以在n阱112与半导体衬底110之间形成sti结构132。n阱电容器电极136可以形成在n阱112上方,并且可以电连接到存储器晶体管190的栅电极138。线196指示n阱电容器电极136与存储器晶体管190的栅电极138之间的电连接。n阱电容器电极136和存储器晶体管190的栅电极138可以由包括单层多晶硅的单个浮栅制成。可以在n阱电容器电极136与n阱112之间形成n阱电介质130。可以在n阱112中邻近n阱电介质130形成n 掺杂的半导体区域122。可以在n 掺杂的半导体区域122上方形成硅化物层168。n 掺杂的半导体区域122可以连接到外部输入端子以偏置n阱电容器192。在一个实施例中,用于偏置n阱电容器192的外部输入端子可以与连接到第二电容器198的第二导电接触188的输入端子不同。

24.图1b是根据本公开的实施例的非易失性存储器器件108的电路图。参考图1b,n阱电容器192可以耦接到存储器晶体管190。第二电容器198可以耦接到存储器晶体管190。n阱电容器192和第二电容器198可以连接到分隔开的输入端子。

25.图2是根据本公开的实施例的非易失性存储器器件108的阵列的俯视图。由剖面线xy

‑

xy’指示的截面图在图5中示出,并且在描述图5时更详细地讨论。参考图2,第二电容器198可以形成在存储器晶体管190和n阱电容器192上方。第二电容器198的第一电极180可以与构成存储器晶体管190的栅电极138的浮栅以及n阱电容器电极136重叠。浮栅以虚线轮廓指示。尽管未示出,但是第二电容器198的第二电极186可以与第二电容器198的第一电极180重叠。第二电容器198的第一电极180和第二电极186的长度和宽度可以等于或大于浮栅的长度和宽度。

26.存储器晶体管190的栅电极138可以覆盖在半导体衬底110上方,并且n阱电容器电极136可以覆盖在n阱112上方。尽管未示出,但是半导体衬底110和n阱112可以通过隔离结构分隔开。源极118可以形成在半导体衬底110中,邻近存储器晶体管190的栅电极138。漏极120可以形成在半导体衬底110中,邻近存储器晶体管190的栅电极138的与源极118相反的一侧。衬底端子116可以形成在半导体衬底110的一部分中。尽管未示出,但是衬底端子116可以通过隔离结构与源极118分隔开。n 掺杂的半导体区域122可以形成在n阱112中,邻近n阱电容器电极136。

27.用于图1所示的非易失性存储器器件108的实施例的一组示例性偏置条件在表1中列出。在编程期间,可以将约五到八伏(5到8v)的电压施加到n阱电容器192和漏极120。可以将约3v的偏置电压施加到源极118,并且可以使衬底端子116接地。可以将约5.5v的正电压施加到第二电容器198的输入端子。偏置条件在源极118与漏极120之间的沟道区中产生垂直取向的强电场,从而导致热电子从沟道区注入到存储器晶体管190的栅电极138的边缘部分。

28.表1

[0029] n阱电容器漏极源极衬底第二电容器编程~5到8v~5到8v3v0v5.5v擦除0v~5到8v0v0v

‑

5.5v读取2.5v1v0v0v0v/浮置

[0030]

由于在向第二电容器198施加正偏置电压之后非易失性存储器器件108的耦合比增大,因此施加到n阱电容器192和漏极120的编程电压降低。第二电容器198提高了从n阱电容器192和第二电容器198到存储器晶体管190的栅电极138的电压传输的效率。非易失性存储器器件108的耦合比可以是第二电容器198的电容(c

198

)和n阱电容器192的电容(c

192

)之和除以存储器晶体管190的栅电极138的电容(c

138

)、第二电容器198的电容(c

198

)和n阱电容器192的电容(c

192

)之和。因此,非易失性存储器器件108的耦合比=(c

198

c

192

)/(c

138

c

198

c

192

)。第二电容器198的电容可以等于或大于n阱电容器192的电容,因为第二电容器198可以与浮栅至少部分地重叠,并且绝缘层182可以具有与电介质层130可比的厚度或小于电介质层130的厚度。非易失性存储器器件108的耦合比可以从约80%增加到约90%或更大。由于在编程期间较低的编程偏置和较低的电场,因此提高了非易失性存储器器件108的可靠性。

[0031]

在擦除期间,n阱电容器192可以接地,并且可以将约五到八伏(5到8伏)的电压施加到存储器晶体管190的漏极120。存储器晶体管190的源极118和衬底端子116可以接地。可以将约

‑

5.5v的负电压施加到第二电容器198的输入端子以耦接到存储器晶体管190的栅电极138。偏置条件可通过带间隧穿(btb)在漏极120区中产生电子空穴对。空穴可通过电介质层128注入到存储器晶体管190的栅电极138中,并与存储在栅电极138中的电子复合。在擦除操作期间施加到第二电容器198上的负电压降低了施加到存储器晶体管190的漏极120上的擦除电压,同时提高了将空穴注入到存储器晶体管190的栅电极138中的效率。由于在擦除期间所使用的擦除电压较低且电场较弱,因此可以提高非易失性存储器器件108的可靠性和寿命。

[0032]

在读取操作期间,可以将约2.5v的正偏压施加到n阱电容器192,并且可以将约1v

的正偏压施加到存储器晶体管190的漏极120。源极118、衬底端子116和第二电容器198可以接地。替代地,第二电容器198可以浮置或不连接到任何偏置电压。在该偏置条件下,取决于存储器晶体管190的阈值电压,可以在存储器晶体管190的漏极120处检测到电流。例如,在擦除操作之后,存储器晶体管190的阈值电压较低,并且可以在存储器晶体管190的漏极120处检测到电流。编程操作可以导致存储器晶体管190的高阈值电压,并且可以在存储器晶体管190的漏极120处检测到较小的电流或可忽略的电流。

[0033]

图1和图2所示的实施例可以在不脱离本公开范围的情况下进行修改以形成替代实施例。例如,图3a是根据本公开的另外实施例的非易失性存储器器件208的阵列的俯视图。图1和图2中使用的相同参考标号也在图3a中用于指示相同特征。与图2所示的非易失性存储器器件阵列108相对比,图3a所示的存储器器件208具有邻近存储器晶体管190的栅电极138的第二电容器298。

[0034]

参考图3a,第二电容器298的电极280可以邻近存储器晶体管190的栅电极138形成。导电接触288可以形成在第二电容器298的电极280上方,用于连接到输入端子。存储器晶体管190的栅电极138和n阱电容器电极136可以由单个浮栅制成。浮栅可以跨半导体衬底110并在n阱112上方延伸。尽管未示出,但是隔离结构可将半导体衬底110与n阱112分隔开。在实施例中,浮栅可以跨将半导体衬底110与n阱112分隔开的隔离结构延伸。半导体衬底110可以是p掺杂的并且包括p阱。

[0035]

源极118可以形成在半导体衬底110中且邻近存储器晶体管190的栅电极138。漏极120可以形成在半导体衬底110中且邻近存储器晶体管190的栅电极138的与源极118相反的一侧。包括p 掺杂的半导体区域的衬底端子116可以形成在半导体衬底110的一部分中。尽管未示出,但是衬底端子116可以通过隔离结构而与源极118分隔开。n 掺杂半导体区域122可以形成在n阱112中且邻近n阱电容器电极136。

[0036]

图3b是根据本公开的另外实施例的沿图3a的剖面线x

‑

x’截取的非易失性存储器器件208的一部分的截面图。参考图3b,可以邻近第二电容器298的电极280的侧壁和存储器晶体管190的栅电极138的侧壁形成电介质间隔物(spacer)152。在实施例中,存储器晶体管190的栅电极138或浮栅可以是第二电容器298的第一电极,而电极280可以是第二电容器298的第二电极。在实施例中,存储器晶体管190的栅电极138具有与第二电容器298的电极280基本相同的厚度。电介质间隔物152可以在第二电容器298的第一电极与第二电极之间形成绝缘层。第二电容器298的第一电极和第二电极可以由多晶硅制成。在实施例中,多晶硅可以是掺杂的或未掺杂的。在实施例中,多晶硅可以掺杂有硼、磷或砷。电介质间隔物152可以由二氧化硅(sio2)或氮化硅(sin)制成。sti结构276可以形成在半导体衬底110中,并且第二电容器298的第二电极或者说280可以形成在sti结构276上方。可以在电极280与sti结构276之间形成电介质层208。电介质层208可以由二氧化硅制成。

[0037]

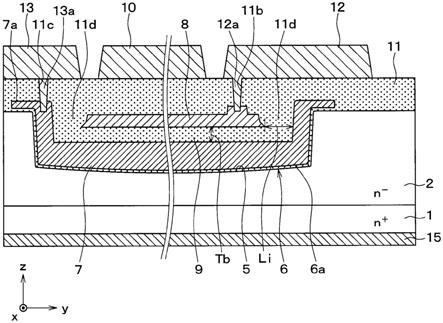

图4是根据本公开的另外实施例的沿图3a的剖面线x

‑

x’截取的非易失性存储器器件208的截面图。参考图4,非易失性存储器器件208包括具有栅电极138的存储器晶体管190。可以将包括n阱电容器192的第一电容器耦接到存储器晶体管190的栅电极138。第二电容器298可以包括存储器晶体管190的栅电极138作为第一电极138,并且包括电极280作为第二电极。可以在电极280上方形成硅化物层270,并且可以在硅化物层270上方形成导电接触288。

[0038]

半导体衬底110可以位于存储器晶体管190的栅电极138下方,并且存储器晶体管190的电介质层128可以位于栅电极138与半导体衬底110之间。可以邻近半导体衬底110形成n阱112,并且sti结构132可以将n阱112与半导体衬底110分隔开。n阱电容器192可以包括n阱112和位于n阱112上方的n阱电容器电极136。n阱电容器电极136可以电连接到存储器晶体管190的栅电极138。n阱电介质130可以位于n阱电容器电极136与n阱112之间。n阱112中的n 掺杂的半导体区域122可以邻近n阱电介质130形成。

[0039]

图5和图6示出了根据本公开的实施例的图2所示的非易失性存储器器件108的制造工艺流程。图5示出了根据本公开的实施例的沿图2的剖面线xy

‑

xy’截取的部分完成的非易失性存储器器件108。参考图5,可以提供半导体衬底110。sti结构126和132可以形成在半导体衬底110中。n阱112可以邻近半导体衬底110形成,与sti结构132相邻。可以提供包括栅电极138的存储器晶体管190。可以提供包括耦接到存储器晶体管190的栅电极138的n阱电容器192的第一电容器。可通过在半导体衬底110、sti结构132和n阱112上方沉积多晶硅层,来形成存储器晶体管190的栅电极138和n阱电容器电极136。该多晶硅层可以是掺杂的或未掺杂的。可通过常规的光致抗蚀剂工艺和蚀刻来图案化该多晶硅层。常规的光致抗蚀剂工艺可以包括在该多晶硅层上方沉积光致抗蚀剂层,然后进行曝光并显影以形成光致抗蚀剂图案。可通过湿法或干法蚀刻去除未被光致抗蚀剂图案覆盖的多晶硅层的部分,以在半导体衬底110和n阱112上方留下多晶硅层的一部分,从而形成存储器晶体管190的栅电极138和n阱电容器电极136。sti结构132上方的多晶硅层的一部分将存储器晶体管190的栅电极138和n阱电容器电极136进行电连接。随后可以去除光致抗蚀剂图案。间隔物结构152可以邻近存储器晶体管190的栅电极138和n阱电容器电极136的侧壁形成。

[0040]

源极118可以形成在半导体衬底110中且邻近存储器晶体管190的栅电极138。尽管未示出,但是漏极可以形成在半导体衬底110中且邻近栅电极138的与源极118相反的一侧。n 掺杂的半导体区域122可以形成在n阱112中且邻近n阱电容器电极136。源极118、漏极和n 掺杂的半导体区域122可以同时形成。衬底端子116可以形成在半导体衬底110中且邻近sti结构126。可以在存储器晶体管190的源极118上方形成硅化物层162,并且可以在n 掺杂的半导体区域122上方形成硅化物层168。可以在存储器晶体管190的栅电极138和n阱电极136上方形成硅化物层170。

[0041]

图6示出了根据本公开的实施例的在形成第二电容器198之后的非易失性存储器器件108。参考图6,可以提供包括第一电极180和第二电极186的第二电容器198。第二电容器198的第二电极186可以连接到输入端子。提供第二电容器198可以包括在硅化物层170上方形成第一导电接触150。导电接触150的形成可以包括在存储器晶体管190和n阱电容器192上方沉积层间电介质(ild)层的下部172a。虚线指示ild层的下部172a的顶表面。可以在ild层的下部172a中形成硅化物层170上方的开口,并且可以在ild层的下部172a中的开口内沉积合适的导电材料,例如钨(w)。可以使用诸如化学机械平面化(cmp)的平面化工艺去除ild层的下部172a上方的导电材料,而留下ild层的下部172a中的开口内的导电材料,从而形成导电接触150。可以分别在源极118和n 掺杂的半导体区域122上方形成导电接触156和160。

[0042]

可以在第一导电接触150上方形成第二电容器198的第一电极180。可以邻近第二电容器198的第一电极180形成绝缘层182。可以邻近绝缘层182形成第二电容器198的第二

电极186。第二电容器198的第一电极180、绝缘层182和第二电容器198的第二电极186的形成可以包括在ild层的下部172a的顶表面上方和第一导电接触150上方沉积合适的第一金属材料(例如tin)层。可以在第一金属材料层上方沉积合适的绝缘材料(例如sin)层。可以在该绝缘材料层上方沉积合适的第二金属材料(例如tin)层。沉积工艺可以是通过原子层沉积(ald)、化学气相沉积(cvd)、物理气相沉积(pvd)或任何其他合适的沉积工艺。第一金属材料层、绝缘材料层和第二金属材料层可以通过常规的光致抗蚀剂工艺和蚀刻来图案化,以留下第一金属材料层、绝缘材料层和第二金属材料层的一部分,从而分别形成第二电容器198的第一电极180、绝缘层182和第二电容器198的第二电极186。

[0043]

可以在ild层的下部172a的顶表面上方形成金属线176和178。金属线176和178可以分别连接到导电接触156和160。金属线176和178的形成可以包括在ild层的下部172a的顶表面上方沉积合适的金属层,其中所述金属包括铜、铝或任何其他合适金属,随后通过常规的光致抗蚀剂工艺和蚀刻进行图案化,以在ild层的下部172a的顶表面以及导电接触156和160上方留下该金属层的一部分,从而分别形成金属线176和178。在形成金属线176和178之前,可以在第二电容器198上方沉积保护层,例如光致抗蚀剂或电介质。可以在形成金属线176和178之后通过湿法或干法蚀刻去除该保护层。可以在ild层的下部172a、金属线176和178以及第二电容器198上方沉积ild层的上部172b。可以在ild层的上部172b中第二电容器198的第二电极186上方形成连接到输入端子的第二导电接触188。

[0044]

图7至图10示出了根据本公开的另外实施例的图4所示的非易失性存储器器件208的制造工艺流程。图7示出了根据本公开的实施例的部分完成的非易失性存储器器件208。参考图7,可以提供半导体衬底110和邻近半导体衬底110的n阱112。可以在半导体衬底110与n阱112之间提供sti结构132。可以在半导体衬底110中提供sti结构276。提供半导体衬底110、n阱112以及sti结构132和276在本领域中是公知的,在此不做进一步阐述。

[0045]

图8示出了根据本公开的实施例的在提供存储器晶体管190、第一电容器和第二电容器298之后的部分完成的非易失性存储器器件208。参考图8,可以提供包括栅电极138的存储器晶体管190。可以提供包括耦接到存储器晶体管190的栅电极138的n阱电容器192的第一电容器。可以提供包括第一电极和第二电极的第二电容器298。第二电容器298的第一电极可以包括存储器晶体管190的栅电极138。第二电容器298的第二电极可以包括电极280。提供存储器晶体管190可以包括形成存储器晶体管190的栅电极138。提供第二电容器298可以包括形成电极280。存储器晶体管190的栅电极138、n阱电容器192的n阱电容器电极136和第二电容器298的电极280的形成可以包括在n阱112、半导体衬底110以及sti结构132和276上方沉积多晶硅层。该多晶硅层可以是掺杂的或未掺杂的。可通过常规的光致抗蚀剂工艺和蚀刻来图案化该多晶硅层,以在sti结构276上方留下多晶硅层,从而形成第二电容器298的电极280。可通过常规的光致抗蚀剂工艺和蚀刻来图案化该多晶硅层,以留下在n阱112、sti结构132和半导体衬底110上方延伸的多晶硅层的一部分。n阱112上方的多晶硅层的一部分形成n阱电容器192的n阱电容器电极136。半导体衬底110上方的多晶硅层的一部分形成存储器晶体管190的栅电极138。sti结构132上方的多晶硅层的一部分提供n阱电容器电极136与存储器晶体管190的栅电极138之间的电连接。第二电容器298的电极280可以与存储器晶体管190的栅电极138以及n阱电容器电极136同时形成。

[0046]

可以邻近存储器晶体管190的栅电极138、n阱电容器电极136和第二电容器298的

电极280的侧壁形成间隔物电介质152。间隔物电介质152的形成可以包括在存储器晶体管190的栅电极138、第二电容器298的电极280和n阱电容器电极136上方沉积合适的电介质材料(例如氮化硅、氧氮化硅、二氧化硅或氧碳氮化硅)的层。可以从存储器晶体管190的栅电极138、第二电容器298的电极280和n阱电容器电极136的顶表面去除电介质材料,而留下存储器晶体管190的栅电极138、第二电容器298的电极280和n阱电容器电极136的侧壁上的电介质材料,从而形成间隔物电介质152。去除工艺可以是各向异性蚀刻。术语各向异性蚀刻可以指在特定方向上去除目标材料的蚀刻工艺。

[0047]

图9示出了根据本公开的实施例的在形成n 掺杂的半导体区域122之后的部分完成的非易失性存储器器件208。参考图9,n 掺杂的半导体区域122可以形成在n阱112中且邻近n阱电容器192的n阱电容器电极136。

[0048]

图10示出了根据本公开的实施例的在第二电容器298的电极280上方形成导电接触288之后的非易失性存储器器件208。在形成导电接触288之前,可以在第二电容器298的电极280上方形成硅化物层270。导电接触288的形成可以包括在第二电容器298的第二电极280上方沉积ild层172,并在ild层172中形成开口。可以在ild层172中的开口内沉积合适的导电材料,例如钨(w)。可以使用诸如cmp的平面化工艺去除ild层172上方的导电材料,而留下ild层172中的开口内的导电材料,从而形成导电接触288。导电接触288可以连接到外部输入端子以偏置第二电容器298。

[0049]

说明书和权利要求书中的术语“第一”、“第二”、“第三”等(如果有)用于区分相似的元素,而并不一定用于描述特定的次序或时间顺序。应当理解,如此使用的术语在适当的情况下是可互换的,以使得本文描述的器件的实施例例如能够以不同于本文示出或以其他方式描述的顺序操作。说明书和权利要求书中的术语“左”、“右”、“前”、“后”、“顶部”、“底部”、“上方”、“下方”等(如果有)仅用于描述的目的,而不一定用于描述永久性的相对位置。应当理解,如此使用的术语在适当的情况下是可互换的,以使得本文描述的器件的实施例例如能够以不同于本文示出或以其他方式描述的取向操作。类似地,如果本文描述的方法包括一系列步骤,则本文中呈现的这些步骤的顺序不一定是可以执行这些步骤的唯一顺序,所述步骤的特定步骤可以被省略和/或另外一些在此未描述的特定步骤可以被添加到该方法中。此外,术语“包括”、“包含”、“具有”及其任何变体旨在涵盖非排他性的包含内容,使得包括一系列元素的过程、方法、物品或器件不一定限于这些元素,而是可以包括未明确列出的或并非这些过程、方法、物品或器件所固有的其他元素。

[0050]

尽管上面对器件的详细描述中已经给出了若干示例性实施例,但是应当理解,存在许多变型。应当进一步理解,实施例仅是示例,并非旨在以任何方式限制器件的范围、适用性、尺寸或配置。而是,上面的详细描述将为本领域技术人员提供实现器件的示例性实施例的便利指南,将理解,在不偏离所附权利要求中陈述的本公开范围的情况下,可以对示例性实施例中描述的元素的功能和布置及其制造方法进行各种改变。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。