1.本公开大体上涉及微处理器,尤其涉及分支预测的方法及其微处理器以及数据处理系统。

背景技术:

2.在数据处理系统内,分支目标缓冲器(branch target buffer;btb)通常用于预测分支指令的结果和分支指令的目标地址以便增强性能。由于微处理器透过增大流水线级(pipeline stages)的数目和并行执行指令的数目来增强性能,因此分支目标缓冲器(btb)的大小通常随之增大以便提高命中率且减少分支误预测造成的性能损失。此外,4gb的数据存储器对处理来自因特网的大量数据不再足够,由此大部份高端微处理器需要64位存储器地址而非10年以前的32位存储器地址。然而,增大btb的大小导致芯片面积增大、存取时间增长以及增加btb操作所需的功率。

技术实现要素:

3.根据实施例中的一个,微处理器具备tlb和btb。tlb包含多个由分支页地址寻址的tlb条目。tlb用于根据指令页地址来判断多个tlb条目当中是否命中至少一个tlb条目。每一tlb条目包含虚拟页地址和对应于l2 tlb其中一路的tlb路码。btb包含多个由分支地址寻址的btb条目,每一条目包含分支地址简码和目标地址简码。在实施例中,判断是否命中btb是透过命中tlb的tlb路码用于选择至少一个btb条目达成。

4.根据实施例中的一个,提供一种在微处理器中从分支地址进行分支预测的方法。所述方法包含至少以下步骤:接收分支地址,根据分支地址的第一部分来存取tlb以从tlb阵列的tlb条目读取tlb路码,根据分支地址的第二部分来存取btb以从btb阵列选择至少一个btb条目,以及根据从tlb取得的tlb路码来判断是否命中btb,其中命中btb代表所选至少一个btb条目与分支地址相关联。

5.根据实施例中的一个,提供一种数据处理系统。数据处理系统包括微处理器、耦合到微处理器的主存储器、耦合到微处理器的总线桥以及耦合到总线桥的输入/输出装置。微处理器包含tlb和btb。tlb包含多个由分支地址寻址的tlb条目,且每一tlb条目包含一个虚拟页地址标记和对应于l2tlb其中一路的tlb路码。btb包含多个由分支地址寻址的btb条目,且每一条目包含分支地址简码和目标地址简码。在实施例中,使用tlb路码在分支预测时选择至少一个btb条目。

附图说明

6.当结合附图阅读时,从以下详细描述会最好地理解本公开。应注意,根据业界标准惯例,各种特征未按比例绘制。实际上,为了论述清楚起见,各种特征的尺寸经过任意的增大或减小。

7.图1是说明根据本公开的一些实施例的数据处理系统10的方块图;

8.图2是说明根据本公开的一些实施例的,如图1中所说明的,cpu指令流水线架构的方块图;

9.图3a和图3b用以说明根据本公开的一些实施例的处理器100的不同部分之间的分支预测;

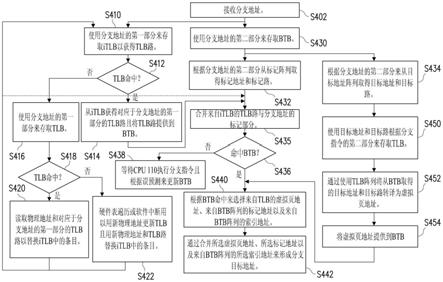

10.图4是说明根据本公开的一些实施例的分支预测过程的流程图;

11.图5a和图5b是说明根据本公开的一个实施例中的分支预测操作的图式;

12.图6是说明根据本公开的一些实施例的分支预测过程的流程图。

13.附图标号说明

14.10:数据处理系统;

15.11:系统总线;

16.12:外围装置;

17.13:存储器;

18.100:处理器;

19.101:内部总线;

20.110:中央处理单元;

21.111:指令提取单元;

22.114:指令解码/发射单元;

23.115:功能单元;

24.116:寄存器组;

25.117:控制和接口单元;

26.118:指令地址产生电路;

27.130:分支预测单元;

28.132:分支目标缓冲器;

29.134:分支历史表;

30.150:存储器管理单元;

31.151:指令转译后备缓冲器(itlb);

32.153:第2级转译后备缓冲器(l2 tlb);

33.171:指令高速缓存(i

‑

cache);

34.190:总线接口单元;

35.1000:指令地址;

36.1320:分支目标地址阵列(分支目标地址标记位置和分支目标索引码);

37.1322、1327:合并逻辑;

38.1323、1324、1512、1513、1531、1532、1533、1534:比较器;

39.1325、1326、1328、1514、1515、1536、1544:多路复用器(mux);

40.1329:分支目标缓冲器的分支标记阵列;

41.1539:转译后备缓冲器的虚拟页地址标记阵列;

42.1510:物理页地址阵列;

43.1516、1517、1537、1540、1542:总线;

44.1518:l2 tlb路码阵列;

45.1519:虚拟页地址标记阵列;

46.1530:物理页地址阵列;branch_addr:分支地址;

47.virtual_addr:虚拟地址;

48.virtual_page_addr:虚拟页地址;

49.inst_addr:指令地址;

50.phy_addr:物理地址;

51.s402、s410、s412、s414、s416、s418、s420、s422、s422、s430、s432、s434、s436、s438、s440、s442、s450、s452、s454、s616、s618、s620、s622:步骤;

52.target_addr:分支目标地址;

53.target_index:分支目标地址索引码;

54.target_way[1:0]:分支目标标记路码;

[0055]

tag_way[1:0]:分支页地址路码;

[0056]

tag_addr[17:12]:分支页地址标记索引码;

[0057]

tlb_way[1:0]:路码;

[0058]

virtual_tag:虚拟页地址标记。

具体实施方式

[0059]

以下公开内容提供用于实施本公开的不同特征的许多不同实施例或实例。下文描述组件和布置的具体实例以简化本公开。当然,这些组件和布置只是实例而非旨在进行限制。举例来说,在以下描述中,两个特征的叠加可以包括两个特征直接接触形成的实施例,也可包括两个特征之间可不直接接触而透过附加特征从叠加的实施例。另外,本公开会在各种实例中重复使用参考编号和/或字母。这种重复是出于简化和清楚的目的且本身并不指示所论述的各种实施例和/或配置之间的关系。

[0060]

分支目标缓冲器(branch target buffer;btb)的功用在提取指令时做分支预测。btb存储先前执行的分支指令的分支地址和分支目标地址以供分支预测之用。在本公开中,用转译后备缓冲器(translation lookaside buffer;tlb)的条目索引码和路码取代btb中用于判断指令分支地址是否在btb中的分支页地址。tlb是现成的转译指令地址的装置,所以通过利用现有tlb结构可减小btb大小。查找btb需要并行做tlb存取以判断分支地址是否在btb中。如此,btb不会受存储器地址位增大影响(具可扩展)且使用比传统btb少得多的位。

[0061]

图1是说明根据本公开的一些实施例的数据处理系统10的方块图。数据处理系统10包含处理器100、系统总线11、存储器13以及一或多个外围装置12。存储器13是系统存储器,系统存储器通过双向总线耦合到系统总线11。外围装置12通过双向总线耦合到系统总线11。处理器100包含总线接口单元(bus interface unit;biu)190,总线接口单元190经由双向总线耦合到系统总线11。处理器100可经由系统总线11与外围装置12或存储器13通信。总线接口单元190经由双向总线耦合到内部总线101。处理器100包含中央处理单元(central processing unit;cpu)110、分支预测单元(branch prediction unit;bpu)130、存储器管理单元(memory management unit;mmu)150以及指令高速缓存171。cpu 110是用于实施数据处理操作的处理器。cpu110、bpu 130、mmu 150以及指令高速缓存171皆经由相

应输入/输出(i/o)端口或端子耦合到内部总线101且在其间通信。

[0062]

处理器100通过执行多个数据处理指令来实施多种数据处理功能。cpu110使用虚拟地址以用于处理指令和数据,且mmu 150在存取cpu 110外部的数据之前将虚拟地址转译为物理地址。cpu 110中的指令地址是虚拟地址,所述虚拟地址必须由mmu 150转译以便cpu 110从指令高速缓存171或存储器13提取指令。类似地,cpu 110中的数据地址亦是虚拟地址且必须由mmu 150转译以便cpu 110从数据高速缓存(未示出)或存储器13提取数据。包含于bpu 130中的分支目标缓冲器(btb)132也使用虚拟地址,使得分支指令地址可直接存取btb 132以用于分支预测而不需要mmu 150进行分支指令地址的物理地址转译。指令高速缓存171是cpu 110频繁使用的指令的临时数据存储装置。cpu 110所需但不在指令高速缓存171内的指令存储于存储器13中。存储器13可包含第2级(level 2;l2)高速缓存和第3级(level 3;l3)高速缓存以及主存储器。l2高速缓存和l3高速缓存提供比主存储器更快的存取时间。l2高速缓存和l3高速缓存是频繁使用的指令和数据的临时存储装置。主存储器可包含随机存取存储器(random access memory;ram)、动态随机存取存储器(dynamic random access memory;dram)、静态随机存取存储器(static random access memory;sram)、只读存储器(read only memory;rom)、可编程只读存储器(programmable read only memory;prom)、电可编程只读存储器(electrically programmable read only memory;eprom)、电可擦除可编程只读存储器(electrically erasable programmable read only memory;eeprom)以及快闪存储器中的至少一者。

[0063]

mmu 150将来自cpu 110的虚拟地址转译为指令高速缓存171和存储器13可使用的物理地址。mmu 150还包含指令转译后备缓冲器(instruction translation lookaside buffer;itlb)151和第2级转译后备缓冲器(level 2translation lookaside buffer;l2 tlb)153。itlb 151和l2 tlb 153存储从虚拟页地址到物理页地址的最新指令页地址转译,可用于快速页地址查找。类似于数据页地址转译,itlb 151是一个仅存储用于指令页地址的虚拟页地址到物理页地址转译的小tlb。mmu 150还可具有用于数据地址的虚拟页地址到物理页地址转译的dtlb(未示出)。l2 tlb 153是比itlb 151大得多的tlb,具有比itlb 151多得多的条目。在实施例中,itlb 151和l2 tlb 153示出于mmu 150中。然而这并非本公开的限制。在其它实施例中,itlb 151和l2 tlb 153可驻存在cpu与指令高速缓存171之间的某些位置处。

[0064]

总线接口单元190是处理器100与系统总线11之间的若干接口单元中的一个。总线接口单元190用以协调与cpu 110执行指令,包含分支指令在内,产生的指令和数据流。由分支指令执行产生的控制信息和数据经由总线接口单元190在cpu 110与系统总线11之间交换。

[0065]

bpu 130是用于处理器100中的分支指令的分支预测单元,bpu 130包含分支目标缓冲器(btb)dbtb 132是一个存储多个条目的高速缓存缓冲器。所述每一条目皆对应于cpu 110曾经执行过的分支指令的指令地址和与分支目标地址。因此,cpu 110执行分支指令且确认下一指令是否为预期中的分支指令结果,若否则cpu 110产生一个新的指令地址经由内部总线101发送到bpu 130。btb 132含有一组由cpu 110产生的最频繁使用分支指令地址。bht 134提供btb 132中对应条目的跳转结果预测。所述跳转结果预测是基于分支指令的过去行为。bht 134可具有用于分支预测的许多不同算法和数个过去行为位。bht 134根

据分支预测的正确与否(分支误预测报告),进行更新。在本公开中不详细论述bht 134,使用任何预测机制皆可。根据从cpu 110接收的指令地址,如果指令地址命中btb,那么btb 132将对应于分支指令的分支目标地址提供给cpu 110。如上文所描述,存储器大小和指令流水线(instruction pipeline)级数的增大也需要较大btb,这需要更多的芯片面积、存取时间以及增加btb操作所需的功率。在本公开中,由btb 132用所预测分支指令地址和分支目标地址的l2 tlb 153的页地址索引码和路码替换各自的页地址以用于判断是否命中btb以及产出分支指令的目标地址。btb 132和其所存储信息的细节将随后描述。

[0066]

图2是说明根据本公开如图1中所说明的cpu 110的一些实施例的指令流水线(instruction pipeline)架构的方块图。cpu 110包含指令提取单元(instruction fetch unit)111、指令解码/发射单元(instruction issue/decode unit)114(也可称为指令解码单元)、一或多个功能单元(functional unit)115、寄存器组(register file)116以及控制和接口单元117。指令提取单元111包含指令缓冲器以暂时在发送到指令解码/发射单元114之前存放来自图1的指令高速缓存171或存储器13的指令。指令提取单元111的输出端耦合到指令解码/发射单元114的输入端以用于解码所提取指令。指令解码/发射单元114的输出端耦合到一或多个功能单元115。一或多个功能单元115经由双向总线耦合到寄存器组116。指令解码/发射单元114也耦合到寄存器组116以获得与正由功能单元115执行的指令有关的读取和写入控制和信息。在一些实施例中,指令解码/发射单元114可对后向条件分支指令或无条件分支指令进行静态分支预测且将分支跳转信息发送到控制和接口单元117。功能单元中的其中一个将执行分支指令,执行分支目标地址计算且判断分支指令的方向(跳转与否)。分支目标地址和分支跳转与否信息发送到控制和接口单元117。此外,指令提取单元111、指令解码/发射单元114以及功能单元115经由个别总线耦合到控制和接口单元117的相应输入/输出端子,控制和接口单元117与内部总线101互相介接。

[0067]

控制和接口单元117具有指令地址产生电路118,指令地址产生电路118具有第一输入端以用于从bpu 130经由内部总线101接收是否命中btb的指示信号以及跳转与否的分支指令预测。指令地址产生电路118还具有第二输入端以用于从btb 132经由内部总线101接收跳转分支指令的btb目标地址。指令地址产生电路118经由内部总线101将分支指令地址、所执行分支指令目标地址以及所执行分支跳转方向信号提供到bpu 130。其它数据和控制信号可视需要经由控制和接口单元117透过内部总线101传达以用于实现数据处理指令的执行。控制和接口单元117可包含数据地址产生电路(未示出)以用于功能单元115到l1数据高速缓存(未示出)和存储器13的数据存取。

[0068]

在实施例中,控制和接口单元117控制指令提取单元111以选择性地识别和实施指令提取,包含一次提取一群指令。指令解码/发射单元114执行指令解码以供一或多个功能单元115执行。寄存器组116用于支持一或多个功能单元115。指令地址产生电路118在控制和接口单元117内。指令地址产生电路118将指令地址发给bpu 130。如果指令地址命中btb,那么将btb目标地址连同跳转与否预测提供给cpu 110。cpu 110使用预测为跳转的分支指令的btb目标地址以从指令高速缓存171或者当指令高速缓存171关闭或其内不存在此地址的情况下从存储器13取得btb目标地址处的指令。在实施例中,可通过存取btb 132、itlb 151和/或l2 tlb 153取得btb命中与否信息和btb目标地址。在一些实施例中,使用基本块入口地址代替分支指令地址。在编译程序术语中,一个基本块是一个直线代码序列,仅能从

入口进入此序列,除了出口外没有分支。应用在本公开上,分支目标地址就是基本块入口地址,而基本块入口可取代分支指令地址用于查找btb。只要本公开中提到分支指令地址(或分支地址)处换成基本块入口地址即可。

[0069]

在实施例中,通过指令提取单元111(单独地或一次以两个或大于两个的群组)从指令高速缓存171或存储器13提取指令。由指令提取单元111用来提取指令的每一指令地址发送到btb 132以用于分支预测。举例来说,如果指令地址1000未命中btb 132,那么cpu 110的流水线假定指令地址1000不是分支指令,继续处理指令地址1000处的指令(且btb预测信息可携带未命中的信息以提供给cpu)。相反地,如果指令地址1000命中btb 132,那么假定指令地址1000有个分支指令,且btb预测信息可用于判断分支指令是否应跳转。举例来说,如果指令地址1000命中btb 132,且与命中的btb条目相关联的bht 134条目预测跳转,那么指令地址产生单元118可将(从btb 132接收到的)btb目标地址提供给指令提取单元111或直接提供给l1指令高速缓存171以投机地从所预测分支目标地址处开始提取。指令地址1000处的指令最终会到达指令提取单元111且通过cpu 110的指令流水线继续进行。即,所述指令从指令提取单元111提供给指令解码/发射单元114以用于解码,然后提供给功能单元115以用于执行(视需要会存取寄存器组116)。如果指令地址1000解码后为分支指令,那么分支指令是否真的跳转在功能单元115中决定。详细地说,当指令地址1000处的分支指令由功能单元115执行时,计算分支目标地址且判断分支方向(跳转与否)。计算后的分支目标地址和跳转与否信息从功能单元115发送到指令地址产生电路118,其中分支指令执行结果与分支预测信息进行比较。由于指令地址1000处的分支指令已经过执行,因此可确认bpu 130是否正确地预测指令地址1000的分支指令的跳转方向。如果分支跳转方向预测正确,那么指令流从当前位置继续执行且bht 134可利用此确认调校预测信息。如果分支预测错误,那么cpu110需要修正此错误。举例来说,cpu 110可视需要清空流水线,且基于功能单元115中的分支执行的结果而提取新指令流。预测错误可发生于bpu 130中命中btb,但分支跳转方向预测不正确地,或分支跳转方向预测正确但分支目标地址预测不正确地。预测错误亦可发生于分支指令不在btb中(未命中btb),但执行时确预测为是一跳转分支指令,或指令地址1000命中btb132但执行结果不是分支指令。指令地址产生电路118追踪所有分支预测地址和预测信息且检测所有分支预测错误或误判的分支指令以更新btb 132和/或bht 134。举例来说,通过指令解码/发射单元114可判断指令地址1000处的指令实际上不是分支指令,需由cpu 110善后。

[0070]

图3a和图3b是说明根据本公开的一些实施例的处理器100内不同部分之间处理分支预测的的方块图。存储器空间被分割为许多存储器页,且每一存储器页大小是4k字节固定大小或由系统存储器预定的任何大小。在一些32位地址存储器实施例中,4k字节由指令地址inst_addr[31:12]寻址。如上文所描述,在cpu 110内处理的所有地址都是虚拟地址,所述虚拟地址必须转译为物理地址以便存取存储器13或处理器100外部的任何物理存储器。虚拟页地址转译为物理页地址,即virtual_addr[31:12]转译为phy_addr[31:12],且虚拟地址和物理地址的位[11:0]共享相同的值。在实施例中,指令地址的第一部分(即,inst_addr[31:12])送给tlb以用于将指令的虚拟页地址转译为物理页地址。

[0071]

参考图3a,说明一些实施例的第2级转译后备缓冲器(l2 tlb)153。l2 tlb 153是具有标记阵列1539和数据阵列1530的高速缓存阵列。标记阵列1539或虚拟页地址标记阵列

是一个虚拟页地址构成的阵列,而数据阵列1530或物理页地址阵列是一个物理页地址构成的阵列。图示中,l2 tlb 153为256条目,4路相联映射的tlb,其构成方法为4组64条目阵列。条目数目被标记为第0项到第k项,其中k在这个实例中是63。l2 tlb 153的每一条目包含虚拟地址阵列1539中的虚拟页地址标记(例如,virtual_tag[31:12])和物理页地址阵列1530中的物理页地址(例如,phy_addr[31:12])。虽然实施例中高速缓存是4路相联映像,然而,限制l2 tlb的映像方式并非本公开意图。本公开的l2 tlb 153可以有各种数目路组的实作。在其它实施例中,l2 tlb阵列153可以是2路相联映射、8路相联映射、n路相联映射等等。在其它实施例中,l2 tlb 153可以是全相联映像或直接映像。此外,指令地址与数据地址共享同一l2 tlb 153,在一些实施例中,l2 tlb 153可包含一个仅特定用于指令地址的l2 itlb和一个仅特定用于数据地址的另一l2dtlb。

[0072]

在虚拟地址查找(或虚拟地址转译)的操作中,一个指令的虚拟页地址,例如,总线1537上的inst_addr[31:12],须转译成实体页地址,其中inst_addr[31:12]用于查找虚拟页地址标记阵列1539以用于判断是否命中tlb。如果tlb命中,那么提取物理页地址阵列1530中的对应条目为转译物理页地址(例如,mux 1536的输出端处的phy_addr[31:12])。如果未命中tlb,那么虚拟页地址不在l2 tlb 153中,硬件分页表遍历(未示出)或软件中断可用于取得转译物理页地址以替换l2 tlb 153中的条目。l2 tlb阵列153存储曾经执行过指令和使用过数据的虚拟页地址。如果分支指令页地址命中虚拟页地址阵列1539,那么分支指令页地址是有效的虚拟页地址。在实施例中,l2 tlb 153包含四个比较器1531、比较器1532、比较器1533、比较器1534,4个关联路,一路一个,且mux 1536使用来自其中一个比较器的命中路信号来选择物理页地址。虚拟页地址,即,总线1537上的inst_addr[31:12],通过查找虚拟页地址标记阵列1539并经由四个比较器1531、比较器1532、比较器1533以及比较器1534比较分支指令页地址的标记部分(例如,inst_addr[31:18])与虚拟页地址标记(例如,virtual_tag[31:18])来判断是否命中tlb,其中来自4个比较器之一的路命中信号用于透过mux1536从物理页地址阵列1530选择物理页地址。

[0073]

由于bpu 130仅使用虚拟地址,bpu 130不需使用l2 tlb 153的物理页地址阵列1530。实施例使用虚拟页地址阵列1539中的有效条目以用于分支预测。如上文所描述,虚拟页地址阵列1539中的条目表示先前所执行指令的有效虚拟页地址。在实施例中,分支预测时可使用来自btb 132的分支目标页地址索引码target_addr[17:12](总线1540)和路码target_way[1:0](总线1542)在l2 tlb 153中查找分支目标地址的虚拟页地址。详细地说,总线1540的分支目标页地址索引码target_addr[17:12]解码为l2 tlb 153的每一路的第0项到第k项当中的第x项,其中每一路的virtual_tag[31:18]可从四路虚拟页地址阵列1539的每一路读取项x取得。总线1542的target_way[1:0]用于通过mux 1544来选择虚拟页地址阵列1539中第x项的四个virtual_tag[31:18]之一作为分支目标地址的虚拟页地址的一部分(即,virtual_page_addr[31:18])。这里提醒virtual_page_addr[31:18]和target_addr[17:12]可以串接形成btb目标地址的完整目标页地址。如上文所描述,虚拟页地址[31:12]可用6位标记索引码(例如,target_addr[17:12])和2位路码(例如,target_way[1:0])从l2 tlb 153的虚拟页地址阵列1539查得。因此,本公开用分支地址branch_addr[17:12](l2 tlb索引码)和来自l2 tlb的路码(例如,tlb_way[1:0])替换常规习知的btb中的分支页地址branch_addr[31:12],得到与常规btb相比位少得多的优势。请注意,通过总线1537的虚

拟页地址查找以及通过总线1540和总线1542的分支目标页地址查找两者可能会同时发生而产生冲突,在此情况下,l2 tlb的控制逻辑将延后通过总线1537的虚拟地址查找1个时钟周期以排解此冲突。随后将进一步描述透过l2 tlb 153的目标地址查找。

[0074]

图3b说明根据本公开的一些实施例的itlb 151的实例。itlb 151是具有虚拟页地址标记阵列1519和物理页地址阵列1510的高速缓存阵列。标记阵列1519或虚拟页地址标记阵列是一个由虚拟页地址构成的阵列,而数据阵列1510或物理页地址阵列是一个由物理页地址构成的阵列。itlb 151的每一条目包含虚拟页地址标记阵列1519中的虚拟页地址标记(例如,virtual_addr[31:12])和物理页地址阵列1510中对应于虚拟页地址标记的物理页地址(例如,phy_addr[31:12])。itlb 151存放最近使用的虚拟页地址且相较于l2 tlb 153具有较少条目。举例来说,itlb 151可具有8个条目,在此情况下可使用全相联映射。在从虚拟地址到物理地址的指令地址转译中,虚拟页地址标记阵列1519的所有8个项可在比较器1512中与总线1517的指令页地址(即,inst_addr[31:12])同时进行比较。来自物理页地址阵列1510的物理页地址由mux 1515通过来自比较器1512的路命中信号进行读取和选择。指令提取单元111需要将指令地址转译成物理地址以从指令高速缓存171或存储器13提取指令。如果inst_addr[31:12]不在虚拟页地址标记阵列1519中,即未命中tlb,那么itlb 151将请求发送到l2 tlb 153以取得物理页地址并替换itlb 151其中之一条目。

[0075]

如上文所描述,实施例通过用6位标记索引码和2位路码替换分支指令的虚拟页地址(即,branch_addr[31:12])来简化分支指令查找。分支预测基于虚拟地址且仅使用虚拟页地址标记阵列1519但不需使用itlb 151的物理页地址阵列1510。在实施例中,itlb 151更包含l2 tlb路码阵列1518以用于分支预测。itlb路码阵列1518的每一条目存放l2 tlb路码(例如,tlb_way[1:0])且与虚拟页地址标记阵列1519中的一个虚拟页地址相对映。l2 tlb路码阵列1518用于将分支地址的虚拟页地址转译为用于分支预测的l2 tlb路码(例如,tlb_way[1:0])。举例来说,总线1516的分支页地址branch_addr[31:12]用于存取itlb 151以用于将分支页地址转译为用以判断是否命中btb的tlb路码tlb_way[1:0]并将其传回btb 132。这里提醒,通过总线1517的指令虚拟页地址查找和通过总线1516的分支目标页地址查找两者可分别通过独立比较器1512和比较器1513以及独立多路复用器mux1515和mux 1514同时发生。分支预测的细节将稍后论述。

[0076]

图3b也根据本公开的一些实施例图示了btb 132的一个实例。在实施例中,btb 132是具有2路相联映射的2048条目btb,其中btb 132由2组1024条目阵列组成。条目号码标示为第0项到第n项,其中n在这个实例中是1023。btb 132是具有标记阵列1329和数据阵列1320的高速缓存阵列,存储先前所执行分支指令的分支标记和对应于该分支地址的分支目标地址简码。标记阵列1329,或称为分支标记阵列,是分支页地址标记位置,即分支页地址标记的索引码(tag_addr[17:12])与tlb路码(tlb_way[1:0]),所构成的阵列,而数据阵列1320,或称为分支目标地址阵列,是分支目标地址简码,即目标页地址标记的索引码与路码(target_addr[17:12]&target_way[1:0]),以及目标地址索引码(index[11:2])所构成的阵列。虽然这里的btb 132图示为2路相联映射高速缓存,但本公开的btb 132可以各种数目个路实施。在其它实施例中,btb阵列132可以是4路相联映像、8路相联映像以及n路相联映像。在其它实施例中,btb阵列132还可以是全相联映像或直接映像。btb 132还包含两个比较器1323、比较器1324,一路一个,且mux 1325、mux 1326以及mux 1328根据来自比较器

1323、比较器1324的路命中信号来选择目标地址。

[0077]

在实施例中,分支预测通过使用branch_addr[17:12](6位标记索引码)和l2 tlb_way[1:0](2位l2 tlb路码)来判断命中btb与否。因此,btb132的条目在分支标记部分仅储存branch_addr[17:12]和l2 tlb路码tlb_way[1:0]以用于识别指令是否是分支指令。当btb 132接收一个指令地址(分支指令的地址即是分支地址)时,branch_addr[31:12]需要转译为l2 tlb路码(即,tlb_way[1:0])。在实施例中,这一转译通过存取itlb 151来完成。转译过程是将虚拟页地址(即,branch_addr[31:12])转成l2 tlb路码(即,tlb_way[1:0])。参考图3b,总线1516的branch_addr[31:12]用于存取itlb151,其中branch_addr[31:12]通过比较器1513与虚拟页地址标记阵列1519的条目进行比较以判断是否命中tlb。l2 tlb路码(即,tlb_way[1:0])读取自itlb路码阵列1518并由mux 1514用来自比较器1513的路命中信号选出。所选出的,与branch_addr[31:12]相关联的,l2 tlb路码发送到btb132。分支地址的页地址标记索引码部分(即,branch_addr[17:12])和选自itlb151的l2 tlb路码(例如,tlb_way[1:0])随后用于与来自btb 132的分支标记阵列1329的tag_addr[17:12]和tag_way[1:0]比较以判断命中btb与否。如果比较器1513输出tlb未命中信息,那么将branch_addr[31:12]发送给l2tlb 153以提取新l2 tlb路码从而替换itlb 151中的一个条目。另外,由于物理地址阵列1510和l2 tlb路码阵列1518两者皆与相同一个虚拟地址标记阵列1519相关联,因此itlb中条目替换需要同时更新l2 tlb路码阵列1518中的l2 tlb路码和物理页地址阵列1510中的物理页地址。bpu 130的分支预测通常都在指令提取单元111之前决定好指令流顺序,如果因此发现分支地址不在itlb 151中,那么可在指令提取单元111需要之前提早从l2 tlb 153提取物理页地址。

[0078]

虽然tlb路码阵列1518和物理页地址阵列1510两者在图3b中说明为itlb 151的一部分,但本公开并不意欲限制itlb的实施方案。在另一实施例中,itlb 151可实施为2个独立itlb。举例来说,第一itlb可包含虚拟页地址标记阵列1519和用于将虚拟页地址转译为l2 tlb路码的tlb路码阵列1518,而第二itlb可包含虚拟页地址标记阵列1519和用于将虚拟页地址转译为物理页地址的物理页地址阵列1510。

[0079]

在另一实施例中,l2 tlb 153可限制存放指令虚拟页地址的路组。举例来说,指令虚拟页地址仅可替换4路相联映射的l2 tlb中的路0和路1。在这种情况下,btb 132的标记路码和itlb 151的tlb路码可简化为单个位路码而非用于4路相联映射的l2 tlb的2位路码。

[0080]

甚者,在另一实施例中,虚拟页可具有许多不同大小。举例来说,虚拟页大小可以是4k字节或4m字节。l2 tlb 153可设计成有4k字节的最小页大小但添加一个位到虚拟地址页标记阵列1539的条目中,以指示该条目来自较大的分页从而让比较器1531到比较器1534用于调整成适当地址位的比较。

[0081]

参考图2和图3b,在收到并将一个指令地址(例如,inst_addr[31:0])提供到控制和接口单元117后,控制和接口单元117将指令地址提供到总线101作为分支地址1000(例如,branch_addr[31:0])以用于分支预测。在实施例中,分支地址1000可以是32位存储器地址(例如,branch_addr[31:0]),所述32位存储器地址包含从分支地址1000的最高有效位开始的虚拟页地址(例如,20位,branch_addr[31:12])、后接索引地址(例如,10位,branch_addr[11:2],也可称为index[9:0]);由于单一指令长度在这个实例中是一个字长,位[1:0]

用于索引字节和半字地址因此字地址不需此两位。

[0082]

当收到分支地址1000以用于分支预测时,branch_addr[17:2]用于存取btb 132且branch_addr[31:12]用于存取itlb 151。在本公开中,btb 132和itlb 151的存取可并行或依序发生,其中本公开并不意欲限制用于分支预测的btb 132和itlb 151的存取时序或序列。详细地说,branch_addr[31:12]通过存取itlb 151来转译为tlb_way[1:0],且随后来自itlb 151的tlb_way[1:0]提供给btb 132且与branch_addr[17:2]一起使用以查找btb132中的分支标记阵列1329以用于判断是否命中btb。如果命中btb,那么对应于分支指令1000的分支目标地址的页地址可通过使用所命中的btb条目中的target_addr[17:12]和target_way[1:0]存取l2 tlb 153来取得。分支预测的操作将在下文详细进行描述。

[0083]

参考图3b,分支地址的页地址部分(即,branch_addr[31:12])提供给itlb 151以用于将分支地址的页地址部分转译为l2 tlb路码(即,tlb_way[1:0])。详细地说,branch_addr[31:12]传至比较器1513,在这里itlb151的每一条目的虚拟页地址(即,virtual_addr[31:12])与branch_addr[31:12]做比较。如果命中itlb 151,那么mux 1514根据由比较器1513输出的路命中信号来选择对应于所命中的itlb条目的tlb_way[1:0]。tlb_way[1:0]随后提供给btb 132以用于判断是否命中btb。如果未能命中itlb 151,那么branch_addr[31:12]发送到l2 tlb 153以提取新l2 tlb路码从而替换itlb151中的一个条目。举例来说,branch_addr[31:12]提供给l2 tlb 153作为图3a中的address[31:12]以用于虚拟页地址查找。由于物理地址阵列1510和l2tlb路码阵列1518两者与同一虚拟页地址标记阵列1519相关联,因此itlb151中的条目替换需要同时更新l2 tlb路码阵列1518中的l2 tlb路码以及物理页地址阵列1510中的物理页地址。请注意,在图3a中,如果地址不是来自btb,那么总线1537上示出的“address[31:12]”或“address[31:18]”就是指令地址(即,inst_address)。如果地址来自btb 132,那么总线1537上示出的“address[31:12]”或“address[31:18]”就是分支地址(branch_addr),这可视为由btb 132请求的虚拟页地址查找操作。

[0084]

在btb 132中,使用分支指令1000的页地址的一部分(即,branch_addr[17:2])以查找btb阵列。详细地说,分支地址1000的索引部分(即,branch_addr[11:2])解码为第0项到第n项中的第x项,其中分支页地址标记索引码(即,tag_addr[17:12])和标记路码(即,tag_way[1:0])可从每一路的分支标记阵列1329读取,且目标页地址标记索引码(即,target_addr[17:12])和目标页地址标记路码(即,target_way[1:0])可从每一路的目标地址阵列1320读取。合并逻辑1322合并(或串接)branch_addr[17:12]与来自itlb 151的tlb_way[1:0]以形成8位地址从而将其与来自分支标记阵列1329的8位数据进行比较。即,branch_addr[17:12]与来自itlb 151的tlb_way[1:0]的串接地址透过两个比较器1323、比较器1324将其与来自标记阵列1329的每一路的tag_addr[17:12]和tag_way[1:0]进行比较。2个比较器之一的命中信号若为真代表命中btb且用此信号透过mux 1325、mux 1326以及mux 1328来选择目标页地址。此外,从目标地址阵列1320读取对应于项x的两组target_addr[17:12]和target_way[1:0],以提供给l2 tlb 153用于虚拟页地址转译。如果未命中btb,那么分支地址1000不在btb 132中,bpu 130等待cpu 110执行分支指令后产生分支预测错误报告以便更新btb132。

[0085]

参考图3a,来自btb 132的每一组target_addr[17:12]和target_way[1:0]通过l2 tlb 153转译为虚拟页地址(即,virtual_page_addr[31:18])。target_addr[17:12]通过总

线1540发送到itlb 153且解码为l2 tlb 153每一路第0项到第k项中的第x项。第x项的virtual_addr[31:18]可从虚拟页地址阵列1539的每一路读取。target_way[1:0]通过总线1542发送到itlb 153且用于透过mux 1544从四个虚拟页地址标记阵列1539的每一路的项x的virtual_addr[31:18]中选择一个作为分支目标地址的虚拟页地址部分(即,virtual_page_addr[31:18])。在实施例中,l2 tlb 153将两个转译后虚拟页地址(即,virtual_page_addr[31:18])发送回到btb 132以用于产生分支指令的完整分支目标地址。

[0086]

返回参看图3b,两个virtual_page_addr[31:18]传给btb 132的mux1326,并根据来自比较器1323、比较器1324之一的命中信号来选择其一。比较器1323、比较器1324中的一个命中信号还提供给mux 1325和mux1328以从目标地址阵列1320选择与项x相关联的一个target_index[11:2]和一个target_addr[17:12]。合并逻辑1327采用来自目标地址阵列1320的target_index[11:2]和target_addr[17:12]以及来自l2 tlb 153的virtual_addr[31:18]以形成30位目标地址。在另一实施例中,单个target_addr[17:12]和target_way[1:0]可先由mux 1328选择出来再发送到l2tlb 153以用于转译为virtual_page_addr[31:18]。单个virtual_page_addr[31:18]从l2 tlb 153返回且通过合并逻辑1327与target_addr[17:12]和target_index[11:2]串接。在这个实施例中不需要mux 1326。在另一实施例中,分支地址和目标地址可在相同虚拟页地址中,在所述情况下,目标地址target_addr[31:12]与分支地址branch_addr[31:12]相同而无需由l2 tlb 153转译。目标地址阵列1320可包含一个额外位,例如“相同页”,以标记branch_addr[31:12]与target_addr[31:12]相同而省略存取l2 tlb 153。

[0087]

图3b所示的实施例中使用32位分支地址是出于说明目的,然而,本公开并不意欲限于此。在替代性实施例中,分支地址1000内的页地址部分和索引的次序可基于设计需求而改变。此外,实施例并不意欲限制指令地址的大小。在其它实施例中,指令地址可以是64个位、128个位或其它数目个位。无论指令地址的大小,因为分支预测储存在分支预测缓冲器内用于标记路码和标记索引的位数目是相同的。如此的btb可以说在存储器地址位或存储器大小上有可扩展性。

[0088]

为在分支地址1000上执行分支预测,bpu 130随后将btb命中、跳转预测以及btb目标地址提供给cpu 110,其中cpu 110可将所预测分支指令放置在指令流水线中。举例来说,指令提取单元可提取btb目标地址处的指令流。在一个实施例中,btb目标地址可在分支预测一开始便直接提供给btb132(如基本块分支预测),以便在btb目标地址上执行分支预测。每一组件和其间的通信的细节将在下文进行描述。

[0089]

在一个实施例中,使用单个tlb代替itlb和l2 tlb。单个tlb具有与l2 tlb相同的结构,其中branch_addr[31:12]通过总线1537查找tlb。比较器1531、比较器1532、比较器1533以及比较器1534判断命中路码,所述命中路码是tlb_way[1:0],用于btb 132中透过比较器1323和比较器1324进行tag_way[1:0]比较。单个tlb可通过虚拟页地址标记阵列1539来执行virtual_addr[31:12]到target_addr[17:12]和target_way[1:0]的转译。tlb路码阵列须添加到单个tlb阵列。

[0090]

图4是说明根据本公开的一些实施例的分支预测过程产生分支目标地址的流程图。在步骤s402中,从指令地址产生电路118或从btb 132接收到分支地址(例如,branch_addr[31:0])(即,提供来自先前指令所预测的分支目标地址以用于分支预测)。分支地址还

可来自功能单元115执行分支后的分支预测错误报告,或从cpu 110的外部中断产生,或来自cpu流水线中的异常,或来自bpu 130的所预测的跳转地址。分支地址和请求来源的数目不限于以上列举且可取决于处理器类型而来自其它来源。分支地址发送到itlb151以用于在步骤s410中进行存取,且发送到btb 132以用于在步骤s430中进行存取,以根据分支地址执行分支预测。

[0091]

在步骤s410中,使用分支地址的第一部分来存取itlb 151以取得tlb路码(例如,tlb_way[1:0])。在实施例中,分支地址的第一部分称为分支地址的页地址部分,例如,branch_addr[31:12]。如上文所论述,实施例的itlb151包含l2 tlb路码阵列1518,其中l2 tlb路码阵列的每一条目皆包含与虚拟页地址标记阵列1519中的虚拟页地址(例如,virtual_addr[31:12])相对映的tlb路码。

[0092]

在步骤s412中,判断命中tlb与否。详细地说,分支地址的页地址部分与标记阵列1519中的虚拟页地址进行比较,以便判断是否命中itlb 151。如果命中itlb 151(步骤s412的“是”路径),那么过程转到步骤s414以判断命中btb与否。如果未命中itlb 151(步骤s412的“否”路径),那么过程转到步骤s416以提取对应于分支地址的第一部分的tlb条目。

[0093]

在步骤s414中,即,命中itlb 151时,匹配到虚拟页地址的标记阵列1519条目所对应的l2 tlb路码从tlb路码阵列1518提取且提供给btb 132以判断是否命中btb。

[0094]

在步骤s416中,即,未命中itlb 151时,使用分支地址的第一部分来存取l2 tlb 153。分支地址的第一部分(即,branch_addr[31:12])用于查找l2 tlb 153中的虚拟页地址标记阵列1539以判断是否命中l2 tlb(步骤s418)。如果命中l2 tlb 153(即,步骤s418的“是”路径),那么过程转到步骤s420。在步骤s420中,从物理页地址阵列1530提取对应于分支地址的第一部分的新物理页地址(即,在虚拟页地址标记阵列1539有所匹配时),且也取得与新物理页地址相关联的l2 tlb 153的路码。根据分支地址的第一部分从l2 tlb 153新取得的物理页地址和路码将替换itlb 151中的一个条目。随后,过程转回到步骤s410、步骤s412、步骤s414以用于通过itlb 151将分支地址的第一部分转译为tlb路码(即,tlb_way[1:0])且将tlb路码提供到btb 132。如果未命中l2 tlb 153(即,步骤s418的“否”路径),那么过程转到步骤s422。在步骤s422中,硬件分页表遍历或软件中断可用于提取新物理地址以更新l2 tlb 153,且新物理页地址和对应于存储该新物理页地址的l2 tlb 153条目的tlb路码亦用以更新itlb 151。随后,过程转回到步骤s410、步骤s412、步骤s414以透过itlb 151将分支地址的第一部分转译为tlb路码(即,tlb_way[1:0])且将tlb路码提供给btb 132。

[0095]

在另一种实施例内,步骤s422和步骤s420可将对应于新物理地址的l2tlb 153的路码直接提供给步骤s434且跳过步骤s410、步骤s412、步骤s414。这在图4中以虚线箭头线表示。换句话说,不需再次存取itlb 151来从刚更新的itlb的条目读取tlb路码。取而代之的是通过步骤s418中的l2 tlb153或步骤s422中的硬件分页表遍历取得对应的tlb路码之后,直接将其提供给btb 132。

[0096]

在步骤s430中,通过使用分支地址的第二部分来存取btb 132。在实施例中,分支地址的第二部分是指分支地址中的页地址标记索引码部分(例如,branch_addr[17:12])和索引部分(例如,branch_addr[11:2]),其中索引部分用于索引btb 132的btb阵列的条目。这里提醒,实施例的btb 132是2路相联映像高速缓存,且因此,所有btb存取皆会读取两组

页地址标记索引码、页地址标记路码、目标页地址标记索引码以及目标页地址标记路码。换句话说,使用分支地址的第二部分存取btb 132时,btb 132的每一路将输出对应的页地址标记索引码和页地址标记路码码。如果命中btb,那么下文描述btb存取的细节和分支目标地址的形成。

[0097]

在步骤s432中,根据分支指令的第二部分从被索引到的分支标记阵列1329条目读取页地址标记索引码(例如,tag_addr[17:12])和页地址标记路码(例如,tag_way[1:0]),其中tag_addr[17:12]和tag_way[1:0]用于在步骤s436中判断是否命中btb。在步骤s436中,分支地址的页地址标记索引码部分(例如,branch_addr[17:12])与在步骤s414中从itlb 151取得的tlb路码(例如,tlb_way[1:0])串接。随后,串接地址(即,branch_addr[17:12] tlb_way[1:0])与从btb 132的分支标记阵列1329读取的tag_address[17:12]和tag_way[1:0]进行比较。如果命中btb(步骤s436的“是”路径),那么过程转到步骤s440,其中由比较产生的命中路信号用于产生分支目标地址和btb命中信号。btb阵列仅提供分支目标地址的一部分。完整分支目标地址的形成需要存取l2 tlb 153,且其过程将在以下步骤s434、步骤s450、步骤s452、步骤s454中解释。如果未命中btb(步骤s436的“否”路径),那么过程转到步骤s438。在步骤s438中,bpu等待cpu 110执行分支指令且根据预测错误报告来更新btb。

[0098]

在步骤s434中,根据分支指令地址的索引部分来从被索引到的目标地址阵列1320条目读取目标页地址标记索引码(例如,target_addr[17:12])和目标页地址路码(例如,target_way[1:0])。在步骤s450中,使用target_addr[17:12]和target_way[1:0]来存取l2 tlb 153。在l2 tlb 153中,透过存取虚拟页地址标记阵列1539将target_addr[17:12]转译为分支目标地址的虚拟页地址。来自btb 132的target_way[1:0]透过mux 1544从4路相联映射高速缓存阵列中与target_addr[17:12]相关联的虚拟页地址标记(例如,virtual_addr[31:18])当中择一。由于两组目标页地址标记索引码和目标页地址标记路码从btb132提供给l2 tlb以用于虚拟页地址转译,l2 tlb 153将对每一组btb 132提供的目标页地址标记索引码产生一个虚拟页地址标记(例如,virtual_page_addr[31:18])。在步骤s454中,l2 tlb 153将虚拟页地址提供给btb 132以用于形成完整分支目标地址。亦即,过程转回到步骤s440。

[0099]

在步骤s440中,由8位地址(即,由控制和接口117提供的分支地址与从itlb 151取得的tlb路码合并而来的地址)与btb条目中记录的8位数据之间比较得来的btb各路命中信号分别透过mux 1325和mux 1328从btb 132中的目标地址阵列1320选择目标页地址标记索引码(例如,target_addr[17:12])和目标地址索引码(例如,target_index[11:2])。btb各路命中信号也透过mux 1325从l2 tlb 153取得的各路虚拟页地址(例如,virtual_page_address[31:18])中择一。

[0100]

在步骤s442中,通过合并逻辑1327串接所选target_addr[17:12]、所选target_index[11:2]以及所选virtual_page_addr[31:18],以便形成完整分支目标地址(也称为btb目标地址)。分支目标地址可经由总线101提供给cpu 110,其中指令提取单元111可根据btb目标地址从指令高速缓存171提取指令。在其它实施例中,形成于步骤s442中的btb目标地址提供到分支预测步骤的开头,例如步骤s402,以便对btb目标地址做下一个分支预测。

[0101]

在以上实施例中,分支预测可存取itlb以取得与分支地址相映的tlb路码而利用

较少位的简化分支地址(即,分支地址的页地址标记部分)完成,其中tlb路码存储于itlb条目中的tlb路码数据字段。同时,还存取btb以查找与至少一个分支地址相关联的btb条目。随后,通过使用从itlb取得的tlb路码来判断是否命中btb。在实施例中,使用itlb快速存取路码以加速分支预测。然而,本公开并不意欲限于此。在其它替代实施例中,可直接存取l2 tlb以取得与分支地址相关联的tlb条目的tlb路码。

[0102]

图5a和图5b说明根据本公开的一些实施例的分支预测操作。图6是说明图5a到图5b中所说明的实施例的分支预测过程的流程图。在这些实施例中,btb 132和l2 tlb 153的结构与图3a到图3b中所说明的实施例相同,所以其细节为了简洁起见而在此处省略。这些实施例之间的一个差异是与分支页地址相关联的l2 tlb 153的tlb路码从l2 tlb 153直接提供给btb132。tlb路码代表l2 tlb 153的n路tlb条目中与分支页地址相关联的那一个条目。在实施例中,分支页地址直接提供给l2 tlb 153以用于虚拟页地址查找。虚拟页地址查找亦称作指令地址的虚拟页地址到物理页地址转译。在实施例中,地址的页部分(例如,address[31:12])可提供给l2 tlb 153以用于虚拟页地址查找操作。指令地址的页部分还可由btb 132提供(例如,branch_addr[31:12])。或者,指令地址的页部分可直接由cpu 110提供(inst_addr[31:12])。在这两种实施例中,btb 132和l2 tlb 153的存取可并行发生。本公开并不意欲限制提供指令地址的页部分的组件。

[0103]

参考图5a,图5b以及图6,btb 132以分支地址1000的索引地址部分(例如,branch_addr[11:2])作索引(步骤s402)。l2 tlb 153取代实施例图示说明图3a到图3b中的itlb 151,其中分支指令的页部分(例如,branch_addr[31:12])转递(或由cpu 110提供)给l2 tlb 153以用于虚拟地址查找操作(步骤s616)。l2 tlb 153根据分支地址的页部分,找出与之匹配的l2 tlb条目和对应于此条目的tlb路码(即,在命中tlb时)。在实施例中,分支地址的页部分(branch_addr[31:12])与l2 tlb的条目进行比较以判断是否命中tlb(步骤s618)。如果命中tlb,那么l2 tlb 153将与分支页地址相关联的l2 tlb条目的tlb路码直接提供给btb。即,对应于分支页地址的tlb路码从步骤s620提供到步骤s434。如果未命中tlb,那么使用硬件分页表遍历或软件中断服务提取对应于分支页地址的转译物理页地址以更新l2 tlb 153中的条目(步骤s622)。随后,过程转回到步骤s616。图6中的步骤s402、步骤s430、步骤s432、步骤s434、步骤s436、步骤s438、步骤s440、步骤s442、步骤s434、步骤s450、步骤s452以及步骤s454类似于图4中的步骤,因此其细节为简洁起见在此处省略。

[0104]

根据实施例中的一个,微处理器具备tlb和btb。tlb包含多个由分支页地址寻址的tlb条目。tlb用于根据指令页地址来判断多个tlb条目当中是否命中至少一个tlb条目。每一tlb条目包含虚拟页地址和对应于l2 tlb其中一路的tlb路码。btb包含多个由分支地址寻址的btb条目,每一条目包含分支地址简码和目标地址简码。在实施例中,判断是否命中btb是透过命中tlb的tlb路码用于选择至少一个btb条目达成。

[0105]

根据实施例中的一个,提供一种在微处理器中从分支地址进行分支预测的方法。所述方法包含至少以下步骤:接收分支地址,根据分支地址的第一部分来存取tlb以从tlb阵列的tlb条目读取tlb路码,根据分支地址的第二部分来存取btb以从btb阵列选择至少一个btb条目,以及根据从tlb取得的tlb路码来判断是否命中btb,其中命中btb代表所选至少一个btb条目与分支地址相关联。

[0106]

根据实施例中的一个,提供一种数据处理系统。数据处理系统包括微处理器、耦合

到微处理器的主存储器、耦合到微处理器的总线桥以及耦合到总线桥的输入/输出装置。微处理器包含tlb和btb。tlb包含多个由分支地址寻址的tlb条目,且每一tlb条目包含一个虚拟页地址标记和对应于l2tlb其中一路的tlb路码。btb包含多个由分支地址寻址的btb条目,且每一条目包含分支地址简码和目标地址简码。在实施例中,使用tlb路码在分支预测时选择至少一个btb条目。

[0107]

前文已概述了若干实施例的特征以使得所属领域的技术人员可更好地理解详细描述。所属领域的技术人员应了解,他们可轻易地将本公开用作设计或修改其它过程和结构的基础,以实现与本文中所介绍的实施例的相同目的和/或达成相同优点。所属领域的技术人员还应认识到,此类等效构造并不脱离本公开的精神和范围,且其可在不脱离本公开的精神和范围的情况下在本文中进行各种改变、替代和更改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。