一种基于dsp和fpga的单板卡式快速原型控制器

技术领域

1.本实用新型属于电子控制技术领域,具体涉及一种基于dsp和 fpga的单板卡式快速原型控制器。

背景技术:

2.硬件人员、软件人员、算法人员在小项目中往往分工不清,需要一人承担,对项目承担者要求过高。有能力的人员需要在一些硬件和软件的设计上花费大量的精力。如果在一个大型项目中,由于涉及人员众多,项目协调和沟通的成本增加,硬件原理图、软件设计和算法设计等工作内容不能完全分割开,造成沟通困难和项目维护困难;

3.如果dspace像快速原型一样采用控制器产品,价格昂贵,系统应用软件复杂,算法运算的快速原型控制器与实际控制器相差较大。若采用类rt

‑

lab的快速原型控制相关产品,价格高,系统复杂,与实际控制员相差甚远。如果采用x86结构的快速原型控制产品,除了与实际控制器存在较大差距外,其实时性也可能存在一些问题,为此我们提出一种基于dsp和fpga的单板卡式快速原型控制器。

技术实现要素:

4.本实用新型的目的在于提供一种基于dsp和fpga的单板卡式快速原型控制器,以解决上述背景技术中提出的问题。

5.为了实现上述目的,本实用新型采用了如下技术方案:一种基于 dsp和fpga的单板卡式快速原型控制器,包括至少两个主控芯片和至少一个数字信号处理器,所述数字信号处理器分别与主控芯片连接,其中一个主控芯片与仿真器模块连接,另一个主控芯片上具有 rj45网口、db9接口以及can信道,所述主控芯片包括第一dsp芯片和第二dsp芯片,所述第一dsp芯片通过jtag接口与仿真器模块连接,所述第二dsp芯片通过与以太网协议芯片连接,所述第二dsp芯片通过sci接口引出一路串口第一串口接口,第一串口接口采用db 的串口接口,所述第二dsp芯片通过第二串口接口引出can信道。

6.进一步地,所述数字信号处理器具体为fpga芯片,所述fpga芯片通过spi总线与第一数据采集模块和第二数据采集模块以及电压输出转换器连接,模拟接口的输出端接入第一数据采集模块和第二数据采集模块的输入端,电压输出转换器的输出端接入模拟接口的输入端。

7.进一步地,所述fpga芯片与第一dsp芯片以及fpga芯片与第二 dsp芯片之间均采用并行总线连接。

8.进一步地,所述第二dsp芯片通过转换收发器引出脉宽调制输出接口。

9.进一步地,所述脉宽调制输出接口包括12路pwi、4路do、4路 di以及一组qep。

10.进一步地,所述仿真器模块与上位机通过usb进行连接。

11.进一步地,所述模拟接口包括模拟转数字信号编码芯片和数字转模拟信号解码芯片,模拟转数字信号编码芯片的输出端接入第一数据采集模块和第二数据采集模块的输入

端,电压输出转换器的输出端接入数字转模拟信号解码芯片的输入端。

12.相比于现有技术,本实用新型的有益效果在于:通过一个相对简单的fpga,只有功能模块更具有通用性和可扩展性,控制器采用单板卡模式,最大限度地降低了系统成本。在一些小批量的场合,可以直接代替现场控制器,成本低,适用于电力电子和电机控制开发的快速原型控制器;该板卡中包含了一个仿真器模块,通过该仿真器模块可实现该板卡的程序在线烧写,通过为该板卡编写的硬件驱动,最终可以实现上位机的模型直接生产控制器代码,通过该仿真器可将该代码烧写。

13.该板卡方案中采用了两个dsp芯片,进行了主控制程序与通用功能扩展的分工,使得在算法程序处理人员或者算法开发阶段主要关注 1#dsp的程序处理,不需要去理会其余的硬件模块功能,通过2#dsp,扩展了一系列针对电机控制,电力电子控制的开发用的接口,通过专门针对2#dsp以及相接的fpga,编写相应的接口程序模块,可以方便的实习基于模型的开发。

附图说明

14.附图用来提供对本实用新型的进一步理解,并且构成说明书的一部分,与本实用新型的实施例一起用于解释本实用新型,并不构成对本实用新型的限制。

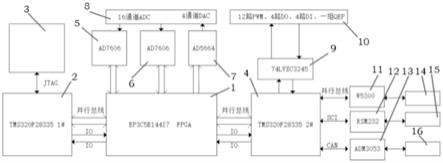

15.图1为本实用新型的原理结构图;

16.图中:1、fpga芯片;2、第一dsp芯片;3、仿真器模块;4、第二dsp芯片;5、第一数据采集模块;6、第二数据采集模块;7、电压输出转换器;8、模拟接口;9、转换收发器;10、脉宽调制输出接口;11、以太网协议芯片;12、第一串口接口;13、第二串口接口; 14、rj45网口;15、db9接口;16、can信道。

具体实施方式

17.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。

18.在本实用新型的描述中,需要理解的是,术语“上”、“下”、“前”、“后”、“左”、“右”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本实用新型的限制。

19.参照图1,本实用新型提出的一种技术方案:一种基于dsp和fpga 的单板卡式快速原型控制器,包括至少两个主控芯片和至少一个数字信号处理器,数字信号处理器分别与主控芯片连接,其中一个主控芯片与仿真器模块3连接,仿真器模块3与上位机通过usb进行连接,在上位机开发了对应目标板卡simulink下驱动模块,通过simulink 下连接仿真器,可实现simlink下的算法模型直接生成控制器代码,另一个主控芯片上具有rj45网口14、db9接口15以及can信道16;

20.主控芯片包括第一dsp芯片2和第二dsp芯片4,第一dsp芯片 2通过jtag接口与仿真器模块3连接,第二dsp芯片4通过与以太网协议芯片11连接,第二dsp芯片4通过sci接口引出一路串口第一串口接口12,第一串口接口12采用db9的串口接口,第二dsp芯片4通过第

二串口接口13引出can信道16;

21.fpga芯片1与第一dsp芯片2以及fpga芯片1与第二dsp芯片 4之间均采用并行总线连接,数字信号处理器具体为fpga芯片1,fpga 芯片1通过spi总线与第一数据采集模块5和第二数据采集模块6以及电压输出转换器7连接,模拟接口8的输出端接入第一数据采集模块5和第二数据采集模块6的输入端,电压输出转换器7的输出端接入模拟接口8的输入端,模拟接口8包括模拟转数字信号编码芯片和数字转模拟信号解码芯片,模拟转数字信号编码芯片的输出端接入第一数据采集模块5和第二数据采集模块6的输入端,电压输出转换器 7的输出端接入数字转模拟信号解码芯片的输入端。

22.本实施例中,第二dsp芯片4通过转换收发器9引出脉宽调制输出接口10,脉宽调制输出接口10包括12路pwi、4路do、4路di 以及一组qep。

23.本实用新型的工作原理及使用流程:该快速原型控制器有第一 dsp芯片2和第二dsp芯片4,型号具体为tms320f28335,以及fpga 芯片1,型号为ep3c5e144i7上述芯片为主要控制芯片,其中第一dsp 芯片2为主要的算法控制处理器,该芯片通过jtag接口与仿真器模块3对接,该仿真器模块3可以跟上位机通过usb进行对接,在上位机开发了对应目标板卡simulink下驱动模块,通过simulink下连接仿真器,可实现simlink下的算法模型直接生成控制器代码;

24.通过fpga芯片1扩展1#处理器外设端口的处理能力,fpga芯片1与第一dsp芯片2、第二dsp芯片4之间主要通过内部并行总线进行信息交互,通过该fpga通过spi总线与第一数据采集模块5和第二数据采集模块6连接,具体型号为ad7606,模拟接口8接入后,使得具备16路模拟量同步采集与处理的功能,通过spi总线与ad5664 信号的电压输出转换器7进行连接,使得板卡具有4路模数转换功能;第二dsp芯片4也接在并行总线上,可以跟fpga与1#dps芯片进行信息交互;

25.第二dsp芯片4引出了4路数字输出接口do,4路数字输入接口 di,12路脉宽调制输出接口10pwm,一组正交编码器信号接口qep,这些接口与dsp芯片之间的电平转换采用74lvx3245实现,第二dsp 芯片4通过并行总结与以太网协议芯片11w5300连接,扩展出了网速能到100m处理能力的以太网接口,该以太网接口采用标准rj45接口,第二dsp芯片4通过sci接口引出一路串口接口rs232,该rs232接口采用db9的串口接口,第二dsp芯片4通过adm3053引出can接口。

26.通过fpga ep3c5e144i7扩展了3个spi总线,以及采用并行总线与两个dsp芯片连接,可以进行三个主芯片之间的信息交互,最终可以将外设接口的信息传递给dsp芯片1,也能将一些ad外设的信息传递给dsp芯片2,通过dsp芯片的网口接口又可以把信息传递到以太网上,最终可以传递到上位机显示,从而可以完成板卡内部处理模块的一些信息实时在环显示。

27.以上所述,仅为本实用新型较佳的具体实施方式,但本实用新型的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本实用新型揭露的技术范围内,根据本实用新型的技术方案及其实用新型构思加以等同替换或改变,都应涵盖在本实用新型的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。