1.本发明涉及集成电路技术领域,特别涉及一种闪存器件的制造方法。

背景技术:

2.闪存元件由于具有可多次进行数据的存入、读取、擦除等动作,且存入的数据在断电后也不会消失的优点,所以已成为个人计算机和电子设备所广泛采用的一种挥发性存储器元件。

3.如图1a所示,衬底10’包括存储单元区aa’及逻辑单元区bb’,存储单元区aa’上形成有闪存单元结构21’,闪存单元结构21’的侧壁覆盖有侧墙层22’。如图1b所示,在对逻辑单元区bb’上暴露的浮栅层11’进行蚀刻时,容易出现衬底边缘的逻辑单元区bb1’和衬底中间的逻辑单元区bb2’的浮栅层11’的蚀刻效果不均匀的现象。例如当整体蚀刻强度较大,衬底中间的逻辑单元区bb2’的浮栅层11’被完整去除,而衬底边缘的逻辑单元区bb1’的浮栅层11’被过度蚀刻而出现表面凹坑缺陷111’(silicon pitting),当整体蚀刻强度较小,衬底边缘的逻辑单元区bb1’的浮栅层11’被完整去除时,而衬底中间的逻辑单元区bb2’的浮栅层11’难以被完整去除而出现浮栅残留缺陷112’(stringer defect)。

技术实现要素:

4.本发明的目的在于提供一种闪存器件的制造方法,以提高蚀刻去除浮栅层的均匀性。

5.为解决上述技术问题,本发明提供一种闪存器件的制造方法,包括:提供一衬底,所述衬底包括存储单元区及逻辑单元区,所述存储单元区及所述逻辑单元区的衬底上形成有浮栅层,在所述存储单元区的浮栅层上形成有闪存单元结构;形成侧墙层及第一氧化层,所述侧墙层覆盖所述闪存单元结构的侧表面,所述第一氧化层覆盖所述逻辑单元区的浮栅层,所述存储单元区及所述逻辑单元区上积聚有聚合物;执行灰化工艺去除所述聚合物,于所述浮栅层的表面形成第二氧化层,所述第一氧化层及所述第二氧化层的厚度和为76埃~80埃,所述灰化工艺的工艺气体包括氧气、氢气及氮气;以及,以所述闪存结构单元为掩模,蚀刻所述第一氧化层、所述第二氧化层及所述浮栅层以暴露所述衬底,所述闪存单元结构下方的浮栅层为所述闪存器件的浮栅。

6.可选的,执行灰化工艺去除所述聚合物,并形成所述第二氧化层的方法包括:执行第一灰化工艺以去除部分所述聚合物,并形成部分所述第二氧化层,所述第一灰化工艺的工艺气体包括氧气;以及,执行第二灰化工艺以去除剩余所述聚合物,并形成剩余部分的所述第二氧化层,所述第二灰化工艺的工艺气体包括氧气、氮气及氢气。

7.可选的,执行所述第一灰化工艺及所述第二灰化工艺的时间比例为1:2~2:1。

8.可选的,执行所述第一灰化工艺及所述第二灰化工艺的时间和为40秒~50秒。

9.可选的,所述第一灰化工艺及所述第二灰化工艺中的工艺温度为100℃~200℃。

[0010][0011]

可选的,所述第一灰化工艺及所述第二灰化工艺中的氧气的流量为2000sccm~4000sccm。

[0012]

可选的,所述第二灰化工艺中的氧气的流量为2000sccm~4000sccm,所述第二灰化工艺中氢气和氮气的流量和为100sccm~200sccm。

[0013]

可选的,形成所述侧墙层及所述第一氧化层的方法包括:依次形成缓冲层及侧墙材料层,所述缓冲层覆盖所述闪存单元结构的外壁以及所述逻辑单元区的浮栅层上,所述侧墙材料层覆盖所述缓冲层;蚀刻所述侧墙材料层,以去除位于所述逻辑单元区的浮栅层上及所述闪存单元结构的顶壁上的侧墙材料层以及部分所述缓冲层,以剩余的位于所述闪存单元结构的侧壁上的侧墙材料层及缓冲层为所述侧墙层,以所述逻辑单元区的浮栅层上剩余的缓冲层为所述第一氧化层。

[0014]

可选的,所述侧墙材料层的材质为氮化硅。

[0015]

可选的,执行所述灰化工艺后湿法清洗所述衬底。

[0016]

综上所述,本发明提供的闪存器件的制造方法具有如下有益效果:利用灰化工艺中额外通入的氢气和氮气形成的第二氧化层以与第一氧化层的厚度和为76埃~80埃,该第一氧化层及第二氧化层覆盖于浮栅层的表面,利用该厚度的第一氧化层及第二氧化层可在蚀刻浮栅层时既留有一定的缓冲余量,缓冲蚀刻浮栅层时的速度差异,不至于在部分区域形成表面凹坑缺陷,而又另部分区域不至于产生浮栅残留缺陷,从而提高蚀刻浮栅层的均匀性。

附图说明

[0017]

本领域的普通技术人员应当理解,提供的附图用于更好地理解本发明,而不对本发明的范围构成任何限定。

[0018]

图1a及图1b为现有制造闪存器件中形成蚀刻浮栅层的示意图;

[0019]

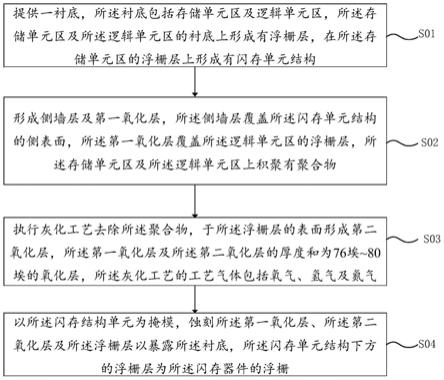

图2为本技术实施例提供的闪存器件的制造方法的流程图;

[0020]

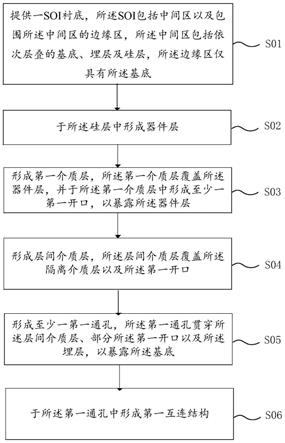

图3a至图3e为本技术实施例提供的闪存器件的制造方法的相应步骤对应的结构示意图。

[0021]

图1a及图1b中:

[0022]

10

’‑

衬底;aa

’‑

存储单元区;bb

’‑

逻辑单元区;bb1

’‑

衬底边缘的逻辑单元区;bb2

’‑

衬底中间的逻辑单元区;11

’‑

浮栅层;111

’‑

表面凹坑缺陷;112

’‑

浮栅残留缺陷;

[0023]

12

’‑

浅沟槽隔离;21

’‑

闪存单元结构;22

’‑

侧墙层。

[0024]

图3a至图3e中:

[0025]

10

‑

衬底;aa

‑

存储单元区;bb

‑

逻辑单元区;11

‑

浮栅层;12

‑

浅沟槽隔离;

[0026]

21

‑

闪存单元结构;22

‑

侧墙层;22a

‑

缓冲层;22b

‑

侧墙材料层;

[0027]

23

‑

聚合物;30

‑

氧化层;31

‑

第一氧化层;32

‑

第二氧化层。

具体实施方式

[0028]

在现有技术中,如图1a所示,在浮栅层11’(例如为多晶硅)的表面上形成有一层较薄的氧化层(图中未示出),氧化层的厚度例如为70埃左右,氧化层可阻挡正常环境中的氧

进入浮栅层11’消耗硅。如图1b所示,在蚀刻浮栅层11’的过程中,需先蚀刻去除氧化层,再去除浮栅层11’。由于衬底边缘的逻辑单元区bb1’之外无浮栅层11’,导致衬底边缘的逻辑单元区bb1’的浮栅层11’相对衬底中间的逻辑单元区bb2’的浮栅层11’的蚀刻强度(速度)相对较高,于是出现衬底边缘的逻辑单元区bb1’的浮栅层11’与衬底中间的逻辑单元区bb2’的浮栅层11’的蚀刻效果不均匀的现象,类似负载效应的效果。但经试验发现,衬底10’表面上的氧化层却并没有上述负载效应,相反,合适厚度氧化层的存在还能在一定程度上减轻上述蚀刻浮栅层11’时的负载效应。

[0029]

基于发明人的上述研究,本发明实施例提供一种闪存器件的制造方法,在形成侧墙层后的灰化工艺中,除通入氧气外,还通入氮气和氢气以增加氧原子的活性,使得浮栅层表面的氧化层的厚度增厚合适的厚度,以达到减轻后续的浮栅层蚀刻的负载效应,使得衬底上的浮栅层蚀刻更为均匀。

[0030]

为使本发明的目的、优点和特征更加清楚,以下结合附图和具体实施例对本发明作进一步详细说明。需说明的是,附图均采用非常简化的形式且未按比例绘制,仅用以方便、明晰地辅助说明本发明实施例的目的。此外,附图所展示的结构往往是实际结构的一部分。特别的,各附图需要展示的侧重点不同,有时会采用不同的比例。

[0031]

如在本发明中所使用的,单数形式“一”、“一个”以及“该”包括复数对象,术语“或”通常是以包括“和/或”的含义而进行使用的,术语“若干”通常是以包括“至少一个”的含义而进行使用的,术语“至少两个”通常是以包括“两个或两个以上”的含义而进行使用的,此外,术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”、“第三”的特征可以明示或者隐含地包括一个或者至少两个该特征,除非内容另外明确指出外。

[0032]

图2为本技术实施例提供的闪存器件的制造方法的流程图。

[0033]

如图2所示,本实施例提供的闪存器件的制造方法,包括:

[0034]

s01:提供一衬底,所述衬底包括存储单元区及逻辑单元区,所述存储单元区及所述逻辑单元区的衬底上形成有浮栅层,在所述存储单元区的浮栅层上形成有闪存单元结构;

[0035]

s02:形成侧墙层及第一氧化层,所述侧墙层覆盖所述闪存单元结构的侧表面,所述第一氧化层覆盖所述逻辑单元区的浮栅层,所述存储单元区及所述逻辑单元区上积聚有聚合物;

[0036]

s03:执行灰化工艺去除所述聚合物,于所述浮栅层的表面形成第二氧化层,所述第一氧化层及所述第二氧化层的厚度和为76埃~80埃,所述灰化工艺的工艺气体包括氧气、氢气及氮气;以及

[0037]

s04:以所述闪存结构单元为掩模,蚀刻所述第一氧化层、所述第二氧化层及所述浮栅层以暴露所述衬底,所述闪存单元结构下方的浮栅层为所述闪存器件的浮栅。

[0038]

图3a至图3e为本实施提供的闪存器件的制造方法的相应步骤对应的结构示意图,接下来,将结合图3a至图3e对所述闪存器件的制造方法进行详细说明。

[0039]

请参照图3a,执行步骤s01,提供一衬底10,衬底10包括存储单元区aa及逻辑单元区bb,存储单元区aa及逻辑单元区bb的衬底10上形成有浮栅层11,在存储单元区aa的浮栅层11上形成有闪存单元结构21。

[0040]

其中,衬底10可以为硅基半导体或绝缘体上硅(soi)衬底,本实施例中衬底10的材料以硅为例加以说明。衬底10表面可以形成有外延层(图中未示出),本实施例中的闪存器件均形成于外延层上。

[0041]

存储单元区aa及逻辑单元区bb的衬底10上依次形成有浮栅氧化层及浮栅层11。浮栅氧化层可作为闪存器件的隧穿氧化层,浮栅氧化层可例如为ono结构,浮栅层11可作为闪存器件的电荷存储层,浮栅层11的材质可例如为多晶硅。存储单元区aa用于形成闪存器件的闪存单元,逻辑单元区bb用于形成实现闪存器件的选择、控制、升压等功能单元。闪存单元结构21形成于存储单元区aa,且凸出浮栅层11的表面,可包括控制栅氧化层、控制栅层及擦除栅层。逻辑单元上还形成有浅沟槽隔离12(sti),浅沟槽隔离12凸出于浮栅层11的表面。

[0042]

请参照图3b,执行步骤s02,依次形成缓冲层22a及侧墙材料层22b,缓冲层22a覆盖闪存单元结构21的外壁及逻辑单元区bb的浮栅层11上,侧墙材料层22b覆盖缓冲层22a。其中,侧墙材料层22b用于形成后续的侧墙层22,侧墙材料层22b的材料可例如为氮化硅,其厚度可为200埃~400埃。缓冲层22a可作为侧墙材料层22b的应力缓冲层22a,以及蚀刻停止层,例如为氧化硅,其厚度可为70埃~120埃。

[0043]

请参照图3c,蚀刻侧墙材料层22b及缓冲层22a,去除位于逻辑单元区bb的浮栅层11上及闪存单元结构21的顶壁上的侧墙材料层22b以及部分缓冲层22a,以剩余的位于闪存单元结构21的侧壁上的侧墙材料层22b及缓冲层22a为侧墙层22,以逻辑单元区bb的浮栅层11上剩余的缓冲层为第一氧化层31。应理解,在上述干法蚀刻的过程中,形成有聚合物23(polymer),聚合物23附着于侧墙层22的表面、逻辑单元的第一氧化层31的表面,以及浅沟槽隔离12的侧壁。

[0044]

请参照图3d,执行步骤s03,执行灰化工艺去除聚合物23,并氧化部分所述浮栅层11以形成第二氧化层32,灰化工艺的工艺气体包括氧气、氢气及氮气。其中,以第一氧化层31及第二氧化层32为氧化层30,氧化层30的厚度(第一氧化层31及第二氧化层32的厚度和)为76埃~80埃。相比于现有技术中厚度为70埃左右的氧化层,本实施例中增厚6埃~10埃的氧化层30可以提高蚀刻浮栅层11的均匀性,减轻负载效应对蚀刻浮栅层11时均匀性的影响。经发明人试验发现,若增厚的氧化层30的厚度过薄,则增厚氧化层30的效果难以体现,而当增厚的氧化层30的厚度过厚,例如大于10埃时,则对浮栅层11的蚀刻会产生其他不良影响。

[0045]

本实施例中,灰化工艺可为等离子体灰化工艺,并将灰化工艺分为多步(至少两步)执行,以进一步精准控制该氧化层30厚度,具体如下:

[0046]

执行第一灰化工艺,执行第一灰化工艺以去除部分聚合物23,并形成部分厚度的第二氧化层32,第一灰化工艺的工艺气体包括氧气;执行第二灰化工艺以去除剩余聚合物23,并形成剩余厚度的第二氧化层32,第二灰化工艺的工艺气体包括氧气、氮气及氢气。其中,第一灰化工艺及第二灰化工艺的工艺温度在100℃~200℃,以降低灰化工艺的热预算;第一灰化工艺及第二灰化工艺中的氧气的流量为2000sccm~4000sccm,第二灰化工艺中氢气和氮气的流量和100sccm~300sccm,以免通入的氢气和氮气过量稀释氧气而降低实际的第二氧化层32形成速率以及降低灰化聚合物23的速率。

[0047]

实际中,在执行第一灰化工艺的过程中所形成的部分第二氧化层32以及第一氧化

层31将阻挡剩余的第二氧化层32的继续形成,因此,在相对确定工艺条件下,无论第一氧化层的厚度或厚或薄都将使得最终所形成部分氧化层(包括第一氧化层31及部分第二氧化层32)的厚度难以超过70埃,而在执行第二灰化工艺的过程中通入的氢气可与氧气作用形成更多的羟基和氧原子,通入的氮气也可催化氧气解离形成氧原子,并且氮气还可进一步增加氧原子的活性,从而在执行第二灰化工艺的过程中产生有较多的具有活性的氧原子。当形成的部分氧化层的厚度不再增加时,活性较强的氧原子可以隧穿过部分氧化层,继续形成剩余厚度的第二氧化层32,以使得氧化层30的厚度精确控制在76埃~80埃。由此,可通过第一灰化工艺与第二灰化工艺所执行的时间以及相应的时间比例以控制所形成的第二氧化层32的厚度,例如在本实施例中,执行第一灰化工艺与第二灰化工艺的时间比例为1:2~2:1,以较佳的实现氧化层30的厚度为76埃~80埃。该第二氧化层32的厚度相比相同条件下不包括氢气和氮气的氧化层的厚度增厚了6埃~10埃。当然,执行第一灰化工艺与第二灰化工艺一共所需时间则可根据待去除的聚合物23的量而定,例如执行第一灰化工艺与第二灰化工艺的时间和为40秒~50秒。

[0048]

在执行灰化工艺后,还可对衬底10执行湿法清洗以进一步清洁衬底10的表面。

[0049]

请参照图3e,执行步骤s04,以闪存单元结构21为掩模,蚀刻逻辑单元区bb的氧化层30及浮栅层11以暴露衬底10,以闪存单元结构21下剩余的浮栅层11为闪存器件的浮栅。

[0050]

上述适当增厚的氧化层30,可在蚀刻浮栅层11时提供一定的蚀刻余量,不至于在蚀刻相对较强的区域形成表面凹坑缺陷,同时又不至于在蚀刻相对较弱的区域形成浮栅残留缺陷。实际中,蚀刻浮栅层11的过程可分为多步进行,例如包括预蚀刻以去除表面的氧化层、主蚀刻以去除绝大部分的浮栅、过蚀刻以确保无浮栅残留,本领域的技术人员在理解上述氧化层30的作用后,可通过有限次的试验获得较均匀的蚀刻效果。

[0051]

当然,本实施例所举例的闪存器件的制造方法还包括后续的其他工艺制程,例如逻辑单元区的逻辑单元的形成、互连工艺的形成,在本技术其他实施例中也还包括其他相应的工艺步骤,但上述步骤的形成采用本领域常用的方法形成,在此不再赘述。

[0052]

综上所述,本发明提供的闪存器件的制造方法具有如下有益效果:利用灰化工艺中额外通入的氢气和氮气形成的第二氧化层以与第一氧化层的厚度和为76埃~80埃,该第一氧化层及第二氧化层覆盖于浮栅层的表面,利用该厚度的第一氧化层及第二氧化层可在蚀刻浮栅层时既留有一定的缓冲余量,缓冲蚀刻浮栅层时的速度差异,不至于在部分区域形成表面凹坑缺陷,而又另部分区域不至于产生浮栅残留缺陷,从而提高蚀刻浮栅层的均匀性。

[0053]

上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。