一种能快速稳定的高psrr、高瞬态响应低压差线性稳压器

技术领域

1.本发明涉及集成电路技术领域,具体的说,是一种能快速稳定的高psrr、高瞬态响应低压差线性稳压器(ldo)。

背景技术:

2.目前,低压差线性稳压器(low dropout regulator,简称ldo)广泛应用于便携式设备、低功耗系统的电源调节等领域,在许多片上系统(soc)中,一个或多个稳压电压用于为soc内的各种子系统供电。现目前已经开发出各种类型的电压调节器来向soc内的不同子系统提供稳压电压。在低功率应用中,稳压器通常用于产生比输入电压更低的稳压输出电压,这种稳压器的一种常见类型是低压差线性稳压器(ldo)。通常,ldo是一个带有误差放大器的闭环,用于驱动传输设备以调节输出电压。ldo一般可以分为两种类型,即n型输出ldo和p型输出ldo。虽然传统的n型输出ldo可以提供良好的psrr和更快的瞬态响应,但是往往需要额外的高电压电源vdd,一般都会增加额外的电荷泵,p型输出的ldo不需要额外的高电压电源vdd,但p型输出的ldo电源抑制比较低。

3.ldo的稳定性与闭环极点和零点有关,其稳定性受到相位裕度的影响,高增益和宽带宽会削弱环路的稳定性,而快速负载瞬态响应则要求宽的带宽,因此环路稳定性与负载瞬态响应是矛盾的关系。为了提高瞬态响应性能,可以采用自适应偏置的方法,即利用依赖于负载电流的偏置电流进行缩放来控制误差放大器输出端的极点,以提高系统带宽。然而,在轻负载电流下,ldo输出极点和误差放大器输出极点都处于非常低的频率并且非常接近,这会导致低相位裕度并降低ldo的稳定性。误差放大器输出端的极点频率也会随着负载电流的增加而增加,从而导致实现ldo稳定性方面面临更多挑战。

技术实现要素:

4.本发明的目的在于提供一种能快速稳定的高psrr、高瞬态响应低压差线性稳压器,解决了pmos晶体管作为输出功率管电源抑制比较低的问题,能够使得ldo快速稳定,提高ldo的瞬态响应性能,并且能够提高ldo的psrr。

5.本发明通过下述技术方案实现:一种能快速稳定的高psrr、高瞬态响应低压差线性稳压器(ldo),包括误差放大器、psrr提高电路、零极点追踪频率补偿电路、提供动态偏置电流的p型晶体管mp

‑

bias和p型输出功率管mp

‑

pass,所述误差放大器的负输入端连接电压差线性稳压器的输出端,误差放大器的正输入端接入参考电压vref,误差放大器的输出端分别与psrr提高电路和零极点追踪频率补偿电路相连接,误差放大器用于形成完整的反馈回路,对参考电压vref和低压差线性稳压器(ldo)的输出进行钳位;零极点追踪频率补偿电路用于产生零点来动态追踪输出极点,消除输出极点对稳定性的影响,进行频率补偿,提高系统的稳定性;psrr提高电路与p型输出功率管mp

‑

pass的栅极及低压差线性稳压器的输出端相连,用于提高低压差线性稳压器(ldo)的电源抑制比,并且当负载快速变化时,提供快速通路,提高系统的瞬态响应性能;所述p型晶体管mp

‑

bias的栅极与p型输出功率管mp

‑

pass的栅极相连,负载变化时,用于追踪随输出负载变化的动态电流,向零极点追踪频率补偿电路(振荡器)提供控制信号,使振荡器产生不同频率的输出信号,改变零极点追踪频率补偿电路(开关电容)的等效阻抗,从而改变零点的位置。

6.进一步的为更好地实现本发明,特别采用下述设置方式:所述误差放大器电路包括第一pmos晶体管mp1、第二pmos晶体管mp2、第三pmos晶体管mp3、第四pmos晶体管mp4、第一nmos晶体管mn1、第二nmos晶体管mn2、第三nmos晶体管mn3、第四nmos晶体管mn4以及尾电流源i1;所述第一pmos晶体管mp1的源极和第二pmos晶体管mp2的源极相连且接入电源电压vdd,所述第一pmos晶体管mp1的栅极与第二pmos晶体管mp2的栅极、第三pmos晶体管mp3的漏极以及第一nmos晶体管mn1的漏极相互连接;所述第一pmos晶体管mp1的漏极与第三pmos晶体管mp3的源极相连;所述第二pmos晶体管mp2的漏极与第四pmos晶体管mp4的源极相连,所述第三pmos晶体管mp3的栅极与第四pmos晶体管mp4的栅极相连接且接入偏置电压vb1;所述第四pmos晶体管mp4的漏极分别与第二nmos晶体管mn2的漏极、零极点追踪频率补偿电路(所述第三电容的c3上极板)以及psrr提高电路(第八pmos晶体管mp8的栅极)相互连接;所述第一nmos晶体管mn1的栅极与第二nmos晶体管mn2的栅极相互连接且接入偏置电压vb2,所述第一nmos晶体管mn1的源极与第三nmos晶体管mn3的漏极相连;所述第二nmos晶体管mn2的源极与第四nmos晶体管mn4的漏极相连;所述第三nmos晶体管mn3的栅极形成误差放大器的正输入端(所述第三nmos晶体管mn3的栅极与所述参考电压vref相连),所述第三nmos晶体管mn3的源极与第四nmos晶体管mn4的源极以及尾电流源i1相互连接;所述第四nmos晶体管mn4的栅极形成误差放大器的负输入端(即所述第四nmos晶体管mn4的栅极与所述p型输出功率管mp

‑

pass的漏极、以及所述第八pmos晶体管的源极相互连接)。

7.进一步的为更好地实现本发明,特别采用下述设置方式:所述psrr提高电路包括第七pmos晶体管mp7、第八pmos晶体管mp8以及尾电流源i2;所述第七pmos晶体管mp7的源极和所述p型输出功率管mp

‑

pass的源极皆接入电源电压vdd,第七pmos晶体管mp7的栅极与p型输出功率管mp

‑

pass的栅极、第七pmos晶体管mp7的漏极、p型晶体管mp

‑

bias的栅极、第八pmos晶体管mp8的漏极以及尾电流源i2相互连接。

8.进一步的为更好地实现本发明,特别采用下述设置方式:在所述p型输出功率管mp

‑

pass的漏极上还连接有负载电流il和负载电容cl;即所述p型输出功率管mp

‑

pass的漏极与所述负载电流il、所述负载电容cl上极板以及低压线性稳压器(ldo)的输出vout相互连接;所述负载电容cl的下极板与地相连。

9.进一步的为更好地实现本发明,特别采用下述设置方式:所述零极点追踪频率补偿电路包括相互连接的开关电容及振荡器,且振荡器与p型晶体管mp

‑

bias的漏极相连接。

10.进一步的为更好地实现本发明,特别采用下述设置方式:所述振荡器包括第一比较器comp、第一电容c1、第七nmos晶体管mn7、第一反相器inv1、第二反相器inv2、第三反相器inv3以及第一d触发器d_f;所述第一比较器comp的负输入端接入参考电压vref1,第一比较器comp的正输入端连接p型晶体管mp

‑

bias的漏极及第七nmos晶体管mn7的漏极,第一比较器comp的输出端与第二反相器inv2的输入端以及第一d触发器d_f的clk端相互连接;所述第七nmos晶体管mn7的源极与地相连,第七nmos晶体管mn7的栅极与第一反相器inv1的输出端相连,第一反相器inv1的输入端连接第二反相器inv2的输出端;所述第一d触发器d_f的d端与第一d触发器d_f的端相连,第一d触发器d_f的q端与第三反相器inv3的输入端及

开关电容(所述第五pmos晶体管mp5的栅极以及所述第六nmos晶体管mn6的栅极)相互连接;所述第三反相器inv3的输出端亦与开关电容相连接(所述第五nmos晶体管mn5的栅极以及第六pmos晶体管mp6的栅极相互连接),所述第一电容c1连接在第七nmos晶体管mn7的源极和漏极之间。

11.进一步的为更好地实现本发明,特别采用下述设置方式:所述开关电容包括第二电容c2、第三电容c3、第五pmos晶体管mp5、第六pmos晶体管mp6、第五nmos晶体管mn5及第六nmos晶体管mn6;所述第五pmos晶体管mp5的漏极、第六pmos晶体管mp6的源极、第五nmos晶体管mn5的源极及第六nmos晶体管mn6的漏极共接其连接第二电容c2的一端(所述第二电容c2的上极板),所述第二电容c2的另一端(所述第二电容c2的下极板)与第六pmos晶体管mp6的漏极及第六nmos晶体管mn6的源极相连接且接地;第五pmos晶体管mp5的栅极和第六nmos晶体管mn6的栅极皆接入振荡器的相同节点(第三反相器inv3的输入端),第五nmos晶体管mn5的栅极和第六pmos晶体管mp6的栅极皆接入振荡器的相同节点(第三反相器inv3的输出端),第五pmos晶体管mp5的源极和第五nmos晶体管mn5的漏极通过第三电容c3接入误差放大器(第二nmos晶体管mn2的漏极)和psrr提高电路(第八pmos晶体管mp8的栅极)。

12.设置时,所述第三电容c3的下极板与所述第五pmos晶体管mp5的源极以及第五nmos晶体管mn5的漏极相互连接;所述第六pmos晶体管mp6的漏极与地相连;所述第六nmos晶体管mn6的源极与地相连。

13.本发明与现有技术相比,具有以下优点及有益效果:

14.本发明能够提高p型输出ldo的电源抑制比,解决了pmos晶体管作为输出功率管电源抑制比较低的问题,并且采用开关电容作为频率相关电阻器件产生低频零点来追踪输出极点进行频率动态补偿的方式,与此同时,引入了快速通路,进一步增加了系统的闭环稳定性和单位增益带宽(ugbw),提高了ldo的瞬态响应性能,由于采用开关电容网络作为电阻器件进行频率补偿,也不会产生过大的功耗,并且占用更少的空间,节省了芯片的面积。

附图说明

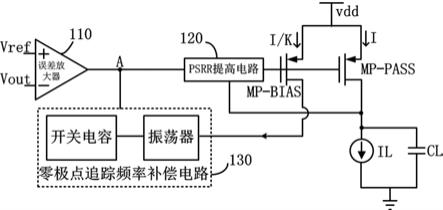

15.图1为本发明的结构框图。

16.图2为本发明的电路原理图。

17.图3为本发明所述振荡器输出的非交叠信号波形图。

18.图4为本发明的频率响应曲线图。

具体实施方式

19.下面结合实施例对本发明作进一步地详细说明,但本发明的实施方式不限于此。

20.为使本发明实施方式的目的、技术方案和优点更加清楚,下面将结合本发明实施方式中的附图,对本发明实施方式中的技术方案进行清楚、完整地描述,显然,所描述的实施方式是本发明一部分实施方式,而不是全部的实施方式。基于本发明中的实施方式,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施方式,都属于本发明保护的范围。因此,以下对在附图中提供的本发明的实施方式的详细描述并非旨在限制要求保护的本发明的范围,而是仅仅表示本发明的选定实施方式。基于本发明中的实施方式,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施方式,都属于本

发明保护的范围。

21.在本发明的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的设备或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

22.此外,术语“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”等的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

23.在本发明中,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

24.在本发明中,除非另有明确的规定和限定,第一特征在第二特征之“上”或之“下”可以包括第一和第二特征直接接触,也可以包括第一和第二特征不是直接接触而是通过它们之间的另外的特征接触。而且,第一特征在第二特征“之上”、“上方”和“上面”包括第一特征在第二特征正上方和斜上方,或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”包括第一特征在第二特征正下方和斜下方,或仅仅表示第一特征水平高度小于第二特征。

25.值得注意的是:在本技术中,某些需要应用到本领域的公知技术或常规技术手段时,申请人可能存在没有在文中具体的阐述该公知技术或/和常规技术手段是一种什么样的技术手段,但不能以文中没有具体公布该技术手段,而认为本技术不符合专利法第二十六条第三款的情况。

26.实施例1:

27.本发明设计出一种能快速稳定的高psrr、高瞬态响应低压差线性稳压器(ldo),解决了pmos晶体管作为输出功率管电源抑制比较低的问题,能够使得ldo快速稳定,提高ldo的瞬态响应性能,并且能够提高ldo的psrr,如图1、图2所示,特别采用下述设置结构:包括误差放大器、psrr提高电路、零极点追踪频率补偿电路、提供动态偏置电流的p型晶体管mp

‑

bias和p型输出功率管mp

‑

pass,所述误差放大器的负输入端连接电压差线性稳压器的输出端,误差放大器的正输入端接入参考电压vref,误差放大器的输出端分别与psrr提高电路和零极点追踪频率补偿电路相连接,误差放大器用于形成完整的反馈回路,对参考电压vref和低压差线性稳压器(ldo)的输出进行钳位;零极点追踪频率补偿电路用于产生零点来动态追踪输出极点,消除输出极点对稳定性的影响,进行频率补偿,提高系统的稳定性;psrr提高电路与p型输出功率管mp

‑

pass的栅极及低压差线性稳压器的输出端相连,用于提高低压差线性稳压器(ldo)的电源抑制比,并且当负载快速变化时,提供快速通路,提高系统的瞬态响应性能;所述p型晶体管mp

‑

bias的栅极与p型输出功率管mp

‑

pass的栅极相连,负载变化时,用于追踪随输出负载变化的动态电流,向零极点追踪频率补偿电路(振荡器)

提供控制信号,使振荡器产生不同频率的输出信号,改变零极点追踪频率补偿电路(开关电容)的等效阻抗,从而改变零点的位置。

28.实施例2:

29.本实施例是在上述实施例的基础上进一步优化,与前述技术方案相同部分在此将不再赘述,如图1~图2所示,进一步的为更好地实现本发明,特别采用下述设置方式:所述误差放大器电路包括第一pmos晶体管mp1、第二pmos晶体管mp2、第三pmos晶体管mp3、第四pmos晶体管mp4、第一nmos晶体管mn1、第二nmos晶体管mn2、第三nmos晶体管mn3、第四nmos晶体管mn4以及尾电流源i1;所述第一pmos晶体管mp1的源极和第二pmos晶体管mp2的源极相连且接入电源电压vdd,所述第一pmos晶体管mp1的栅极与第二pmos晶体管mp2的栅极、第三pmos晶体管mp3的漏极以及第一nmos晶体管mn1的漏极相互连接;所述第一pmos晶体管mp1的漏极与第三pmos晶体管mp3的源极相连;所述第二pmos晶体管mp2的漏极与第四pmos晶体管mp4的源极相连,所述第三pmos晶体管mp3的栅极与第四pmos晶体管mp4的栅极相连接且接入偏置电压vb1;所述第四pmos晶体管mp4的漏极分别与第二nmos晶体管mn2的漏极、零极点追踪频率补偿电路(所述第三电容的c3上极板)以及psrr提高电路(第八pmos晶体管mp8的栅极)相互连接;所述第一nmos晶体管mn1的栅极与第二nmos晶体管mn2的栅极相互连接且接入偏置电压vb2,所述第一nmos晶体管mn1的源极与第三nmos晶体管mn3的漏极相连;所述第二nmos晶体管mn2的源极与第四nmos晶体管mn4的漏极相连;所述第三nmos晶体管mn3的栅极形成误差放大器的正输入端(所述第三nmos晶体管mn3的栅极与所述参考电压vref相连),所述第三nmos晶体管mn3的源极与第四nmos晶体管mn4的源极以及尾电流源i1相互连接;所述第四nmos晶体管mn4的栅极形成误差放大器的负输入端(即所述第四nmos晶体管mn4的栅极与所述p型输出功率管mp

‑

pass的漏极、以及所述第八pmos晶体管mp8的源极相互连接)。

30.实施例3:

31.本实施例是在上述任一实施例的基础上进一步优化,与前述技术方案相同部分在此将不再赘述,如图1~图2所示,进一步的为更好地实现本发明,特别采用下述设置方式:所述psrr提高电路包括第七pmos晶体管mp7、第八pmos晶体管mp8以及尾电流源i2;所述第七pmos晶体管mp7的源极和所述p型输出功率管mp

‑

pass的源极皆接入电源电压vdd,第七pmos晶体管mp7的栅极与p型输出功率管mp

‑

pass的栅极、第七pmos晶体管mp7的漏极、p型晶体管mp

‑

bias的栅极、第八pmos晶体管mp8的漏极以及尾电流源i2相互连接。

32.实施例4:

33.本实施例是在上述任一实施例的基础上进一步优化,与前述技术方案相同部分在此将不再赘述,如图1~图2所示,进一步的为更好地实现本发明,特别采用下述设置方式:在所述p型输出功率管mp

‑

pass的漏极上还连接有负载电流il和负载电容cl;即所述p型输出功率管mp

‑

pass的漏极与所述负载电流il、所述负载电容cl上极板以及低压线性稳压器(ldo)的输出vout相互连接;所述负载电容cl的下极板与地相连。

34.实施例5:

35.本实施例是在上述任一实施例的基础上进一步优化,与前述技术方案相同部分在此将不再赘述,如图1~图2所示,进一步的为更好地实现本发明,特别采用下述设置方式:所述零极点追踪频率补偿电路包括相互连接的开关电容及振荡器,且振荡器与p型晶体管

mp

‑

bias的漏极相连接。

36.实施例6:

37.本实施例是在上述任一实施例的基础上进一步优化,与前述技术方案相同部分在此将不再赘述,如图1~图2所示,进一步的为更好地实现本发明,特别采用下述设置方式:所述振荡器包括第一比较器comp、第一电容c1、第七nmos晶体管mn7、第一反相器inv1、第二反相器inv2、第三反相器inv3以及第一d触发器d_f;所述第一比较器comp的负输入端接入参考电压vref1,第一比较器comp的正输入端连接p型晶体管mp

‑

bias的漏极及第七nmos晶体管的漏极,第一比较器comp的输出端与第二反相器inv2的输入端以及第一d触发器d_f的clk端相互连接;所述第七nmos晶体管mn7的源极与地相连,第七nmos晶体管mn7的栅极与第一反相器inv1的输出端相连,第一反相器inv1的输入端连接第二反相器inv2的输出端;所述第一d触发器d_f的d端与第一d触发器d_f的端相连,第一d触发器d_f的q端与第三反相器inv3的输入端及开关电容(所述第五pmos晶体管mp5的栅极以及所述第六nmos晶体管mn6的栅极)相互连接;所述第三反相器inv3的输出端亦与开关电容相连接(所述第五nmos晶体管mn5的栅极以及第六pmos晶体管mp6的栅极相互连接),所述第一电容c1连接在第七nmos晶体管mn7的源极和漏极之间。

38.实施例7:

39.本实施例是在上述任一实施例的基础上进一步优化,与前述技术方案相同部分在此将不再赘述,如图1~图2所示,进一步的为更好地实现本发明,特别采用下述设置方式:所述开关电容包括第二电容c2、第三电容c3、第五pmos晶体管mp5、第六pmos晶体管mp6、第五nmos晶体管mn5及第六nmos晶体管mn6;所述第五pmos晶体管mp5的漏极、第六pmos晶体管mp6的源极、第五nmos晶体管mn5的源极及第六nmos晶体管mn6的漏极共接其连接第二电容c2的一端(所述第二电容c2的上极板),所述第二电容c2的另一端(所述第二电容c2的下极板)与第六pmos晶体管mp6的漏极及第六nmos晶体管mn6的源极相连接且接地;第五pmos晶体管mp5的栅极和第六nmos晶体管mn6的栅极皆接入振荡器的相同节点(第三反相器inv3的输入端),第五nmos晶体管mn5的栅极和第六pmos晶体管mp6的栅极皆接入振荡器的相同节点(第三反相器inv3的输出端),第五pmos晶体管mp5的源极和第五nmos晶体管mn5的漏极通过第三电容c3接入误差放大器(第二nmos晶体管mn2的漏极)和psrr提高电路(第八pmos晶体管mp8的栅极)。

40.设置时,所述第三电容c3的下极板与所述第五pmos晶体管mp5的源极以及第五nmos晶体管mn5的漏极相互连接;所述第六pmos晶体管mp6的漏极与地相连;所述第六nmos晶体管mn6的源极与地相连。

41.实施例8:

42.如图1所示,一种能快速稳定的高psrr、高瞬态响应低压差线性稳压器(ldo),包括误差放大器110、psrr提高电路120、零极点追踪频率补偿电路130、提供动态偏置电流的p型晶体管mp

‑

bias以及p型输出功率管mp

‑

pass,其中零极点追踪补偿电路又包括振荡器和开关电容。

43.误差放大器110的负输入端与低压差线性稳压器(ldo)的输出相连,正输入端与参考电压vref相连,误差放大器110的输出端a与psrr提高电路和零极点追踪频率补偿电路

130相连,误差放大器110用于形成完整的反馈回路,对参考电压vref和ldo的输出进行钳位;

44.零极点追踪频率补偿电路130用于产生零点来动态追踪输出极点,消除输出极点对稳定性的影响,进行频率补偿,提高系统的稳定性;

45.psrr提高电路120与p型输出功率管mp

‑

pass的栅极和ldo的输出端相连,用于提高ldo的电源抑制比,并且当负载快速变化时,提供快速通路,提高系统的瞬态响应性能;

46.p型晶体管mp

‑

bias的栅极与p型输出功率管mp

‑

pass的栅极相连,负载变化时,用于追踪随输出负载变化的动态电流,向振荡器提供电流控制信号,使振荡器产生不同频率的输出信号,改变开关电容的等效阻抗,从而改变零点的位置。

47.具体地,如图2所示的ldo的电路原理图,误差放大器电路包括第一pmos晶体管mp1、第二pmos晶体管mp2、第三pmos晶体管mp3、第四pmos晶体管mp4、第一nmos晶体管mn1、第二nmos晶体管mn2、第三nmos晶体管mn3、第四nmos晶体管mn4以及尾电流源i1;第一pmos晶体管mp1的源极和第二pmos晶体管mp2的源极相连且接入电源电压vdd,第一pmos晶体管mp1的栅极与第二pmos晶体管mp2的栅极、第三pmos晶体管mp3的漏极以及第一nmos晶体管mn1的漏极相互连接;第一pmos晶体管mp1的漏极与第三pmos晶体管mp3的源极相连;第二pmos晶体管mp2的漏极与第四pmos晶体管mp4的源极相连,第三pmos晶体管mp3的栅极与第四pmos晶体管mp4的栅极相连接且接入偏置电压vb1;第四pmos晶体管mp4的漏极分别与第二nmos晶体管mn2的漏极、开关电容中的第三电容的c3上极板以及psrr提高电路中第八pmos晶体管mp8的栅极相互连接;第一nmos晶体管mn1的栅极与第二nmos晶体管mn2的栅极相互连接且接入偏置电压vb2,第一nmos晶体管mn1的源极与第三nmos晶体管mn3的漏极相连;第二nmos晶体管mn2的源极与第四nmos晶体管mn4的漏极相连;第三nmos晶体管mn3的栅极形成误差放大器的正输入端(即第三nmos晶体管mn3的栅极与参考电压vref相连),第三nmos晶体管mn3的源极与第四nmos晶体管mn4的源极以及尾电流源i1相互连接;第四nmos晶体管mn4的栅极形成误差放大器的负输入端(即第四nmos晶体管mn4的栅极与p型输出功率管mp

‑

pass的漏极、以及第八pmos晶体管mp8的源极相互连接)。

48.psrr提高电路包括第七pmos晶体管mp7、第八pmos晶体管mp8以及尾电流源i2;第七pmos晶体管mp7的源极和p型输出功率管mp

‑

pass的源极皆接入电源电压vdd,第七pmos晶体管mp7的栅极与p型输出功率管mp

‑

pass的栅极、第七pmos晶体管mp7的漏极、p型晶体管mp

‑

bias的栅极、第八pmos晶体管mp8的漏极以及尾电流源i2相互连接。

49.在p型输出功率管mp

‑

pass的漏极上还连接有负载电流il和负载电容cl;即p型输出功率管mp

‑

pass的漏极与负载电流il、负载电容cl上极板以及低压线性稳压器(ldo)的输出vout相互连接;负载电容cl的下极板与地相连。

50.零极点追踪频率补偿电路包括相互连接的开关电容及振荡器。

51.其中,振荡器包括第一比较器comp、第一电容c1、第七nmos晶体管mn7、第一反相器inv1、第二反相器inv2、第三反相器inv3以及第一d触发器d_f;第一比较器comp的负输入端接入参考电压vref1,第一比较器comp的正输入端连接p型晶体管mp

‑

bias的漏极及第七nmos晶体管的漏极,第一比较器comp的输出端与第二反相器inv2的输入端以及第一d触发器d_f的clk端相互连接;第七nmos晶体管mn7的源极与地相连,第七nmos晶体管mn7的栅极与第一反相器inv1的输出端相连,第一反相器inv1的输入端连接第二反相器inv2的输出

端;第一d触发器d_f的d端与第一d触发器d_f的端相连,第一d触发器d_f的q端与第三反相器inv3的输入端、开关电容的第五pmos晶体管mp5的栅极以及开关电容的第六nmos晶体管mn6的栅极相互连接;第三反相器inv3的输出端亦与开关电容的第五nmos晶体管mn5的栅极以及开关电容的第六pmos晶体管mp6的栅极相互连接,第一电容c1连接在第七nmos晶体管mn7的源极和漏极之间;p型晶体管mp

‑

bias的源极与电源电压vdd相连,p型晶体管mp

‑

bias的漏极与第一比较器comp的正输入端、第七nmos晶体管mn7的漏极、以及第一电容c1的上极板相互连接。

52.开关电容包括第二电容c2、第三电容c3、第五pmos晶体管mp5、第六pmos晶体管mp6、第五nmos晶体管mn5及第六nmos晶体管mn6;第五pmos晶体管mp5的漏极、第六pmos晶体管mp6的源极、第五nmos晶体管mn5的源极及第六nmos晶体管mn6的漏极共接其连接第二电容c2的上极板,所述第二电容c2的下极板与第六pmos晶体管mp6的漏极及第六nmos晶体管mn6的源极相连接且接地;第五pmos晶体管mp5的栅极和第六nmos晶体管mn6的栅极皆接入第三反相器inv3的输入端,第五nmos晶体管mn5的栅极和第六pmos晶体管mp6的栅极皆接入第三反相器inv3的输出端,第五pmos晶体管mp5的源极和第五nmos晶体管mn5的漏极通过第三电容c3接入第二nmos晶体管mn2的漏极和第八pmos晶体管mp8的栅极。

53.设置时,第三电容c3的下极板与第五pmos晶体管mp5的源极以及第五nmos晶体管mn5的漏极相互连接;第六pmos晶体管mp6的漏极与地相连;第六nmos晶体管mn6的源极与地相连。

54.下面结合图2、图3和图4对本发明的工作原理作进一步的说明:

55.ldo的稳定性与环路极点有关,在图2的具体实施例中,极点包括误差放大器输出级极点p

a

,误差放大器中的镜像极点p

b

,p型输出功率管mp

‑

pass栅极处的极点p

c

,以及ldo的输出极点p

out

。其中镜像极点p

b

和输出功率管mp

‑

pass栅极处的极点p

c

为高频极点,通常高于ldo环路的单位增益带宽,不会影响环路的稳定性。误差放大器的小信号分析表明,误差放大器输出端a点的3db带宽由下式给出:

[0056][0057]

其中,g

m,mp4

为晶体管mp4的跨导,f

ds,mp4

为晶体管mp4的沟道电阻,r

ds,mp2

为晶体管mp2的沟道电阻,g

m,mn2

为晶体管mn2的跨导,r

ds,mn2

为晶体管mn2的沟道电阻,r

ds,mn4

为晶体管mn4的沟道电阻,c

a

为误差放大器输出端a点的等效电容。

[0058]

由于第八pmos晶体管mp8类似于源跟随器,该ldo的输出电阻和输出极点的3db带宽由下式给出:

[0059][0060][0061]

其中,g

m,mp8

为第八pmos晶体管mp8的跨导,r

load

为负载电阻,r

ds,mp

‑

pass

为输出功率管mp

‑

pass的沟道电阻,c

load

位负载电容。

[0062]

由方程(2)(3)可知,p

out

随着ldo负载电流变化,并且在轻负载电流条件下处于非

常低的频率。p

out

的频率随着负载电流的增加而增加。在低静态电流ldo中,有限的偏置电流导致误差放大器高的输出阻抗。因此,与误差放大器的输出阻抗成反比的p

a

也处于非常低的频率,这会对环路稳定性造成严重影响。

[0063]

本发明提出了零极点追踪频率补偿电路来提高系统的稳定性,增加系统带宽。通过引入p

out

跟踪的零点,使得零点和p

out

彼此靠近,来消除输出极点,以提升相位,确保稳定性。具体实现原理如下,由图2的振荡器可知,通过p型输出功率管mp

‑

pass的电流被镜像通过p型晶体管mp

‑

bias,假设流过p型输出功率管mp

‑

pass的电流为i,流过p型晶体管mp

‑

bias的电流则为i/k。然后,通过p型晶体管mp

‑

bias的电流将作为振荡器中的偏置电流对第一电容c1充电,直到其电压v

c1

超过参考电压v

ref1

,在该参考电压下第一比较器comp将其输出状态瞬间改变为逻辑高电平以对第一电容c1放电;一旦第一电容c1放电,第一比较器comp就会输出逻辑低电平,输出再经过二分频电路(第一d触发器)d_f进行二分频,在经过第三反相器inv3,从而产生相反的非重叠输出时钟信号a和如图3所示。该振荡器的近似输出时钟频率f

c

为:

[0064][0065]

其中c1为第一电容的电容值,k为晶体管mp

‑

pass与晶体管mp

‑

bias的尺寸比,i为流过晶体管mp

‑

pass的电流大小,v

ref1

为参考电压。

[0066]

方程(4)表明输出频率与流过p型输出功率管mp

‑

pass的电流i是成比例的。

[0067]

由图2开关电容可知,振荡器产生的非重叠时钟信号a和驱动作为开关操作的一对传输门tg1和tg2,tg1和tg2以时钟频率f

c

交替打开,对第二电容c2进行充电和放电,从而改变开关电容的等效阻抗。该开关电容的等效阻抗r

eq

可以表示为:

[0068][0069]

从方程(5)中可以看出,该开关电容电路的等效电阻与第二电容c2和时钟频率f

c

成反比;当时钟频率增加时,等效阻抗减小,当第二电容c2增大时,等效阻抗减小。

[0070]

为了改变开关电容的等效阻抗,当负载电流i

load

改变时,会导致振荡器改变输出时钟信号a和的频率。当i

load

增加时,电流控制的振荡器导致输出时钟信号a和的频率增加,从而降低了开关电容网络的等效阻抗;当i

load

减小时,电流控制的振荡器导致输出时钟信号a和的频率降低,从而增加了开关电容网络的等效阻抗。

[0071]

开关电容极点跟踪产生的零点z

c

由下式给出:

[0072][0073]

由方程(6)可得,z

c

跟踪与i

load

成正比的p

out

,并且使得相位在整个负载电流范围都得到了提升,增加了系统的稳定性,同时引入的零点也增加了环路的单位增益带宽(ugbw),提高了瞬态响应性能。从图4频率响应曲线图可以看出,有零极点追踪频率补偿电路的ldo单位增益带宽(ugbw)可以显著提高,零极点消除使得稳定性条件被放松,表明还可以将误差放大器输出端的极点p

a

选择的更高,进一步提高ldo的瞬态响应性能,提高psrr的带宽。

[0074]

在另一方面,与r

eq

直接相连的净寄生电容c0也会产生额外的极点,形成的极点由

下式给出:

[0075][0076]

其中,f

c

为振荡器输出的时钟频率,c0为净寄生电容。

[0077]

但是由于净寄生电容c0很小,由方程(7)可知,p

c0

会超出环路的单位增益带宽,不会对环路稳定性造成影响。

[0078]

下面对psrr提升电路的工作原理作进一步分析,psrr是衡量ldo抑制来自不同频率的输入电源纹波的能力,采用pmos晶体管作为输出功率管的ldo除了输入电压v

in

不需要任何其他电压供应,但是由于pmos晶体管的栅极直接与输入电源电压相连,所以其电源抑制比较低。

[0079]

为了使得ldo在全频率范围内都有较高的电源抑制比,并且除了输入电压v

in

不需要任何其他电压供应;根据本发明的一方面,在pmos输出ldo内配备了快速环路和慢速环路,误差放大器采用共源共栅的cascode结构以提高电源抑制比,慢速环路包括误差放大器、第八pmos晶体管mp8以及零极点追踪频率补偿电路,快速通路包括第七pmos晶体管mp7、p型输出功率管mp

‑

pass以及第八pmos晶体管mp8。第七pmos晶体管mp7采用二极管连接,电源vin中的噪声通过第七pmos晶体管mp7传输到p型输出功率管mp

‑

pass的栅极,可以有效地消除电源vin中的噪声,提高ldo的电源抑制比。

[0080]

ldo输出端的瞬时电流有时候会非常大,输出可能会上冲和下冲过多,快速回路可以减少上冲和下冲的幅度,进一步提高瞬态响应性能。当负载电压v

out

发生突变时,被第八pmos晶体管mp8的源极所检测,通过快速环路使p型输出功率管mp

‑

pass的栅极电压快速响应。负载电流显著增加时,电流源i2可以瞬间吸收更多电流,直到慢速环路能够跟得上。

[0081]

综上所述,本发明提供的快速稳定的高psrr、高瞬态响应低压差线性稳压器通过引入开关电容电阻器件,镜像随负载变化的p型输出功率mos管作为振荡器的偏置电流,来改变振荡器的信号频率,从而控制开关电容的等效阻抗,进而产生追踪输出极点变化的零点,提高了环路的带宽和系统的稳定性,增加了慢速回路的响应速度,也节省了芯片的面积;由于零点和输出级负载电流相互追踪,因此负载电流可变参数的稳定性条件被大大放松了;此外,零极点消除意味着可以将误差放大器输出端的极点p

a

选择为更高,并且系统单位增益带宽(ugbw)可以更高,这将使得ldo瞬态响应更快,psrr带宽更高。除此之外,还提出了psrr提升电路,通过引入二极管连接的pmos晶体管显著提高了ldo的psrr,引入的快速环路可以进一步提高系统的带宽,这也有助于改善psrr和瞬态响应性能,减少负载变化时导致的电压上冲和下冲幅度。

[0082]

以上所述,仅是本发明的较佳实施例,并非对本发明做任何形式上的限制,凡是依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化,均落入本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。