1.本发明涉及显示技术领域,尤其涉及一种驱动电路和显示装置。

背景技术:

2.在相关的驱动电路中,与第一节点电连接的晶体管的特性容易发生负向漂移,会使得在输入阶段和输出阶段,第一节点的电位需要为有效电压时,所述第一节点放噪电路包括的晶体管会漏电而使得第一节点的电位不能维持为有效电压,从而发生第一节点充电不足和驱动信号输出不足的问题。

技术实现要素:

3.本发明的主要目的在于提供一种驱动电路和显示装置,解决由于漏电而导致的第一节点的电位不能在输入阶段和输出阶段维持为有效电压,而导致的驱动信号输出不足的问题。

4.为了达到上述目的,本发明实施例提供了一种驱动电路,包括第一节点放噪电路;

5.所述第一节点放噪电路分别与第一节点、复位端、第二节点、第一降噪电压端和第二降噪电压端电连接,用于在所述复位端提供的复位信号的控制下,控制所述第一节点与所述第一降噪电压端之间连通,在所述第二节点的电位的控制下,控制所述第一节点与所述第二降噪电压端之间连通;

6.所述第一降噪电压端用于提供第一降噪电压,所述第二降噪电压端用于提供第二降噪电压;

7.所述第一降噪电压的电压值在第一预定电压值范围内,所述第二降噪电压的电压值在第二预定电压值范围内。

8.可选的,所述第一节点放噪电路还分别与帧复位端和第三降噪电压端电连接,用于在所述帧复位端提供的帧复位信号的控制下,控制所述第一节点与所述第三降噪电压端之间连通;

9.所述第三降噪电压端用于提供第三降噪电压,所述第三降噪电压的电压值在第三预定电压范围内。

10.可选的,所述第一节点放噪电路包括第一晶体管;

11.所述第一晶体管的控制极与所述复位端电连接,所述第一晶体管的第一极与所述第一节点电连接,所述第一晶体管的第二极与所述第一降噪电压端电连接;

12.所述第一预定电压值范围被设置而使得当所述复位端提供的复位信号的电位为无效电压时,所述第一晶体管关断。

13.可选的,所述第一节点放噪电路包括第二晶体管;

14.所述第二晶体管的控制极与第二节点电连接,所述第二晶体管的第一极与所述第一节点电连接,所述第二晶体管的第二极与所述第二降噪电压端电连接;

15.所述第二预定电压值范围被设置而使得当所述第二节点的电位为无效电压时,所

述第二晶体管关断。

16.可选的,所述第一节点放噪电路包括第二晶体管和第三晶体管;所述第二节点包括第一个第二节点和第二个第二节点;

17.所述第二晶体管的控制极与所述第一个第二节点电连接,所述第二晶体管的第一极与所述第一节点电连接,所述第二晶体管的第二极与所述第二降噪电压端电连接;

18.所述第三晶体管的控制极与所述第二个第二节点电连接,所述第二晶体管的第一极与所述第一节点电连接,所述第二晶体管的第二极与所述第二降噪电压端电连接;

19.所述第二预定电压值范围被设置而使得当所述第一个第二节点的电位为无效电压时,所述第二晶体管关断,并使得当所述第二个第二节点的电位为无效电压时,所述第三晶体管关断。

20.可选的,所述第一节点放噪电路包括第四晶体管;

21.所述第四晶体管的控制极与所述帧复位端电连接,所述第四晶体管的第一极与所述第一节点电连接,所述第四晶体管的第二极与所述第三降噪电压端电连接;

22.所述第三预定电压值范围被设置而使得当所述帧复位端提供的帧复位信号的电位为无效电压时,所述第四晶体管关断。

23.可选的,所述第一预定电压值范围、所述第二预定电压值范围和所述第三预定电压值范围内为同一预定电压值范围,所述预定电压值范围为大于或等于

‑

8v而小于或等于

‑

4v。

24.可选的,本发明实施例所述的驱动电路还包括:第一节点控制电路、第二节点控制电路、储能电路、驱动输出电路和进位信号输出电路;

25.所述第一节点控制电路分别与第一节点与输入端电连接,用于根据所述输入端提供的输入信号,控制所述第一节点的电位;

26.所述第二节点控制电路用于控制第二节点的电位;

27.所述储能电路分别与所述第一节点和驱动信号输出端电连接,用于储存电能,并控制所述第一节点的电位;

28.所述驱动输出电路分别与第一节点、输出控制端、时钟信号端、第一电压端和驱动信号输出端电连接,用于在所述第一节点的电位的控制下,控制所述驱动信号输出端与所述时钟信号端之间连通,在所述输出控制端提供的输出控制信号的控制下,控制所述驱动信号输出端与所述第一电压端之间连通;

29.所述进位信号输出电路分别与第一节点、输出控制端、时钟信号端、第二电压端和进位信号输出端电连接,用于在所述第一节点的电位的控制下,控制所述进位信号输出端与所述时钟信号端之间连通,在所述输出控制端提供的输出控制信号的控制下,控制所述进位信号输出端与所述第二电压端之间连通;

30.所述输出控制端包括第二节点;或者,所述输出控制端包括所述第二节点和所述复位端。

31.本发明实施例还提供一种显示装置,包括降噪电压提供电路和上述的驱动电路;

32.所述降噪电压提供电路用于为第一降噪电压端提供第一降噪电压,为第二降噪电压端提供第二降噪电压,并使得所述第一降噪电压的电压值在第一预定电压值范围内,并使得所述第二降噪电压的电压值在第二预定电压值范围内。

33.可选的,所述第一节点放噪电路还分别与帧复位端、所述第一节点和第三降噪电压端电连接,用于在所述帧复位端提供的帧复位信号的控制下,控制所述第一节点与所述第三降噪电压端之间连通;

34.所述降噪电压提供电路还用于为所述第三降噪电压端提供第三降噪电压,以使得所述第三降噪电压的电压值在第三预定电压范围内。

35.本发明实施例所述的驱动电路和显示装置可以通过设置第一降噪电压的电压值和第二降噪电压的电压值,以使得在输入阶段和输出阶段,第一节点的电位能够维持为有效电压,使得驱动信号输出正常,利于实现高迁移率的驱动电路。

附图说明

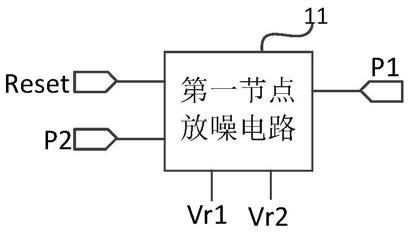

36.图1是本发明至少一实施例所述的驱动电路的结构图;

37.图2是本发明至少一实施例所述的驱动电路的结构图;

38.图3是本发明至少一实施例所述的驱动电路的结构图;

39.图4是本发明至少一实施例所述的驱动电路的结构图;

40.图5是本发明至少一实施例所述的驱动电路的结构图;

41.图6是本发明至少一实施例所述的驱动电路的结构图;

42.图7是本发明至少一实施例所述的驱动电路的电路图;

43.图8是图7所示的驱动电路的至少一实施例通过驱动信号输出端输出的驱动信号的波形图;

44.图9是图7所示的驱动电路的至少一实施例通过驱动信号输出端输出的驱动信号的波形图;

45.图10是图7所示的驱动电路的至少一实施例通过驱动信号输出端输出的驱动信号的波形图;

46.图11是本发明至少一实施例所述的驱动电路的电路图;

47.图12是本发明至少一实施例所述的驱动电路的电路图;

48.图13是本发明至少一实施例所述的驱动电路的电路图;

49.图14是本发明至少一实施例所述的驱动电路的电路图。

具体实施方式

50.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

51.本发明所有实施例中采用的晶体管均可以为三极管、薄膜晶体管或场效应管或其他特性相同的器件。在本发明实施例中,为区分晶体管除控制极之外的两极,将其中一极称为第一极,另一极称为第二极。

52.在实际操作时,当所述晶体管为薄膜晶体管或场效应管时,所述第一极可以为漏极,所述第二极可以为源极;或者,所述第一极可以为源极,所述第二极可以为漏极。

53.如图1所示,本发明实施例所述的驱动电路包括第一节点放噪电路11;

54.所述第一节点放噪电路11分别与第一节点p1、复位端reset、第二节点p2、第一降噪电压端vr1和第二降噪电压端vr2电连接,用于在所述复位端reset提供的复位信号的控制下,控制所述第一节点p1与所述第一降噪电压端vr1之间连通,在所述第二节点p2的电位的控制下,控制所述第一节点p1与所述第二降噪电压端vr2之间连通;

55.所述第一降噪电压端vr1用于提供第一降噪电压,所述第二降噪电压端vr2用于提供第二降噪电压;

56.所述第一降噪电压的电压值在第一预定电压值范围内,所述第二降噪电压的电压值在第二预定电压值范围内。

57.在本发明至少一实施例中,vr1和vr2可以为同一电压端,例如,vr1和vr2可以为第三低电压端,所述第三低电压端用于提供第三低电压vgl3;但不以此为限。在实际操作时,vr1和vr2也可以为不同的电压端。

58.可选的,所述第一预定电压值范围和所述第二预定电压值范围可以都为大于或等于

‑

8v而小于或等于

‑

4v,但不以此为限;更优选的,所述第一预定电压值范围和所述第二预定电压值范围可以都为大于或等于

‑

7.5v而小于或等于

‑

4.5v。

59.在具体实施时,所述第一节点p1可以为上拉节点,所述第二节点p2可以为下拉节点。

60.如图1所示的本发明实施例所述的驱动电路在工作时,当所述第一节点放噪电路11包括的与第一节点p1电连接的晶体管的特性负向漂移时,可以通过设置第一降噪电压的电压值和第二降噪电压的电压值,以使得在输入阶段和输出阶段,不会发生所述第一节点放噪电路11包括的晶体管漏电而使得p1的电位不能维持为有效电压的情况,从而能够在输入阶段和输出阶段,可以保证第一节点的电位为有效电压,使得驱动信号输出正常,利于实现高迁移率的驱动电路。

61.在本发明至少一实施例中,当驱动电路中的驱动输出电路包括的栅极与所述第一节点电连接的晶体管为n型晶体管时,所述有效电压可以为高电压,当该晶体管为p型晶体管时,所述有效电压可以为低电压;但不以此为限。

62.如图1所示的本发明实施例所述的驱动电路在工作时,在输入阶段和输出阶段,通过提升第一降噪电压和第二降噪电压,可以断开所述第一节点p1与第一降噪电压端vr1之间的漏电通路,断开所述第一节点p1与第二降噪电压端vr2之间的漏电通路。

63.如图2所示,在图1所示的驱动电路的实施例的基础上,所述第一节点放噪电路11还可以分别与帧复位端t_rst和第三降噪电压端vr3电连接,用于在所述帧复位端t_rst提供的帧复位信号的控制下,控制所述第一节点p1与所述第三降噪电压端之间vr3连通;

64.所述第三降噪电压端vr3用于提供第三降噪电压,所述第三降噪电压的电压值在第三预定电压范围内。

65.在本发明至少一实施例中,vr1、vr2和vr3可以为同一电压端,例如,vr1、vr2和vr3可以为第三低电压端,所述第三低电压端用于提供第三低电压vgl3;但不以此为限。在实际操作时,vr1、vr2和vr3也可以为不同的电压端。

66.可选的,所述第三预定电压值范围可以为大于或等于

‑

8v而小于或等于

‑

4v,但不以此为限;更优选的,所述第三预定电压值范围可以为大于或等于

‑

7.5v而小于或等于

‑

4.5v。

67.本发明如图2所示的驱动电路的实施例在工作时,在输入阶段和输出阶段,通过提升第三降噪电压,可以断开所述第一节点p1与第三降噪电压端vr3之间的漏电通路。

68.可选的,所述第一节点放噪电路包括第一晶体管;

69.所述第一晶体管的控制极与所述复位端电连接,所述第一晶体管的第一极与所述第一节点电连接,所述第一晶体管的第二极与所述第一降噪电压端电连接;

70.所述第一预定电压值范围被设置而使得当所述复位端提供的复位信号的电位为无效电压时,所述第一晶体管关断。

71.在具体实施时,所述第一节点放噪电路可以包括第一晶体管,当复位端提供的复位信号为无效电压时,通过设置第一预定电压值范围,能够保证第一晶体管关断,不存在漏电通路。

72.在本发明至少一实施例中,当第一晶体管为n型晶体管时,无效电压可以为低电压;当第一晶体管为p型晶体管时,无效电压可以为高电压。

73.在具体实施时,当所述第一晶体管为n型晶体管时,所述第一预定电压值范围被设置,而使得当所述复位信号的电位为无效电压时,所述复位信号的电位与所述第一降噪电压的电压值的差值小于所述第一晶体管的阈值电压,以保证所述第一晶体管关断。

74.当所述第一晶体管为n型晶体管,并第一晶体管的阈值电压由于负向偏移而变为负值时,为了防止在输入阶段和输出阶段,第一晶体管的栅源电压大于所述第一晶体管的阈值电压而发生漏电,导致第一节点的电位不能维持为有效电压,从而不能正常输出驱动信号的情况发生,本发明至少一实施例可以通过提升所述第一降噪电压的电压值,保证在输入阶段和输出阶段,所述第一节点的电位能够为有效电压,保证正常输出驱动信号。

75.在本发明至少一实施例中,第一晶体管并不限于为n型晶体管,在实际操作时,所述第一晶体管也可以为p型晶体管。

76.可选的,所述第一节点放噪电路包括第二晶体管;

77.所述第二晶体管的控制极与第二节点电连接,所述第二晶体管的第一极与所述第一节点电连接,所述第二晶体管的第二极与所述第二降噪电压端电连接;

78.所述第二预定电压值范围被设置而使得当所述第二节点的电位为无效电压时,所述第二晶体管关断。

79.在本发明至少一实施例中,当第二晶体管为n型晶体管时,无效电压可以为低电压;当第二晶体管为p型晶体管时,无效电压可以为高电压。

80.在具体实施时,所述第一节点放噪电路可以包括第二晶体管,当第二节点的电位为无效电压时,通过设置第二预定电压值范围,能够保证第二晶体管关断,不存在漏电通路。

81.在具体实施时,当所述第二晶体管为n型晶体管时,所述第二预定电压值范围被设置,而使得当所述第二节点的电位为无效电压时,所述第二节点的电位与所述第二降噪电压的电压值的差值小于所述第二晶体管的阈值电压,以保证所述第二晶体管关断。

82.当所述第二晶体管为n型晶体管,并第二晶体管的阈值电压由于负向偏移而变为负值时,为了防止在输入阶段和输出阶段,第二晶体管的栅源电压大于所述第二晶体管的阈值电压而发生漏电,导致第一节点的电位不能维持为有效电压,从而不能正常输出驱动信号的情况发生,本发明至少一实施例可以通过提升所述第二降噪电压的电压值,保证在

输入阶段和输出阶段,所述第一节点的电位能够为有效电压,保证正常输出驱动信号。

83.在本发明至少一实施例中,第二晶体管并不限于为n型晶体管,在实际操作时,所述第二晶体管也可以为p型晶体管。

84.可选的,所述第一节点放噪电路包括第二晶体管和第三晶体管;所述第二节点包括第一个第二节点和第二个第二节点;

85.所述第二晶体管的控制极与所述第一个第二节点电连接,所述第二晶体管的第一极与所述第一节点电连接,所述第二晶体管的第二极与所述第二降噪电压端电连接;

86.所述第三晶体管的控制极与所述第二个第二节点电连接,所述第二晶体管的第一极与所述第一节点电连接,所述第二晶体管的第二极与所述第二降噪电压端电连接;

87.所述第二预定电压值范围被设置而使得当所述第一个第二节点的电位为无效电压时,所述第二晶体管和所述第三晶体管都关断。

88.在具体实施时,所述第一节点放噪电路可以包括第二晶体管和第三晶体管,当第一个第二节点的电位和第二个第二节点的电位都为无效电压时,通过设置第二预定电压值范围,能够保证所述第二晶体管和所述第三晶体管都关断,不存在漏电通路。

89.在本发明至少一实施例中,当第二晶体管和第三晶体管为n型晶体管时,无效电压可以为低电压;当第二晶体管和第三晶体管为p型晶体管时,无效电压可以为高电压。

90.在具体实施时,第二节点可以包括第一个第二节点和第二个第二节点,当所述第二晶体管和所述第三晶体管都为n型晶体管时,所述第二预定电压值范围被设置而使得当所述第一个第二节点的电位为无效电压时,所述第一个第二节点的电位与所述第二降噪电压的电压值的差值小于所述第二晶体管的阈值电压,并使得当所述第二个第二节点的电位为无效电压时,所述第二个第二节点的电位与所述第二降噪电压的电压值的差值小于所述第三晶体管的阈值电压,以保证所述第二晶体管和所述第三晶体管都关断。

91.当所述第二晶体管和所述第三晶体管为n型晶体管,并第二晶体管的阈值电压和/或所述第三晶体管的阈值电压由于负向偏移而变为负值时,为了防止在输入阶段和输出阶段,第二晶体管的栅源电压大于所述第二晶体管的阈值电压,和/或,第三晶体管的栅源电压大于所述第三晶体管的阈值电压,而发生漏电,导致第一节点的电位不能维持为有效电压,从而不能正常输出驱动信号的情况发生,本发明至少一实施例可以通过提升所述第二降噪电压的电压值,保证在输入阶段和输出阶段,所述第一节点的电位能够为有效电压,保证正常输出驱动信号。

92.在本发明至少一实施例中,第二晶体管和第三晶体管并不限于为n型晶体管,在实际操作时,所述第二晶体管和所述第三晶体管也可以为p型晶体管。

93.可选的,所述第一节点放噪电路包括第四晶体管;

94.所述第四晶体管的控制极与所述帧复位端电连接,所述第四晶体管的第一极与所述第一节点电连接,所述第四晶体管的第二极与所述第三降噪电压端电连接;

95.所述第三预定电压值范围被设置而使得当所述帧复位端提供的帧复位信号的电位为无效电压时,所述第四晶体管关断。

96.在具体实施时,所述第一节点放噪电路可以包括第四晶体管,当帧复位端提供的帧复位信号为无效电压时,通过设置第三预定电压值范围,能够保证第四晶体管关断,不存在漏电通路。

97.在本发明至少一实施例中,当第四晶体管为n型晶体管时,无效电压可以为低电压;当第四晶体管为p型晶体管时,无效电压可以为高电压。

98.在具体实施时,当所述第四晶体管为n型晶体管时,所述第三预定电压值范围被设置而使得当所述帧复位端提供的帧复位信号的电位为无效电压时,所述帧复位信号的电位与所述第三降噪电压的电压值的差值小于所述第四晶体管的阈值电压,以保证所述第四晶体管关断。

99.当所述第四晶体管为n型晶体管,并第四晶体管的阈值电压由于负向偏移而变为负值时,为了防止在输入阶段和输出阶段,第四晶体管的栅源电压大于所述第四晶体管的阈值电压而发生漏电,导致第一节点的电位不能维持为有效电压,从而不能正常输出驱动信号的情况发生,本发明至少一实施例可以通过提升所述第三降噪电压的电压值,保证在输入阶段和输出阶段,所述第一节点的电位能够为有效电压,保证正常输出驱动信号。

100.在本发明至少一实施例中,第四晶体管并不限于为n型晶体管,在实际操作时,所述第四晶体管也可以为p型晶体管。

101.在本发明至少一实施例中,所述第一预定电压值范围、所述第二预定电压值范围和所述第三预定电压值范围内可以为同一预定电压值范围,所述预定电压值范围为大于或等于

‑

8v而小于或等于

‑

4v,但不以此为限。更优选的,所述预定电压值范围可以为大于或等于

‑

7.5v而小于或等于

‑

4.5v。

102.在具体实施时,本发明至少一实施例所述的驱动电路还包括:第一节点控制电路、第二节点控制电路、储能电路、驱动输出电路和进位信号输出电路;

103.所述第一节点控制电路分别与第一节点与输入端电连接,用于根据所述输入端提供的输入信号,控制所述第一节点的电位;

104.所述第二节点控制电路用于控制第二节点的电位;

105.所述储能电路分别与所述第一节点和驱动信号输出端电连接,用于储存电能,并控制所述第一节点的电位;

106.所述驱动输出电路分别与第一节点、输出控制端、时钟信号端、第一电压端、驱动信号输出端电连接,用于在所述第一节点的电位的控制下,控制所述驱动信号输出端与所述时钟信号端之间连通,在所述输出控制端提供的输出控制信号的控制下,控制所述驱动信号输出端与所述第一电压端之间连通;

107.所述进位信号输出电路分别与第一节点、输出控制端、时钟信号端、第二电压端和进位信号输出端电连接,用于在所述第一节点的电位的控制下,控制所述进位信号输出端与所述时钟信号端之间连通,在所述输出控制端提供的输出控制信号的控制下,控制所述进位信号输出端与所述第二电压端之间连通;

108.所述输出控制端包括第二节点;或者,所述输出控制端包括所述第二节点和所述复位端。

109.可选的,所述第一电压端可以为第二低电压端,所述第二电压端可以为第一低电压端,但不以此为限。

110.在本发明至少一实施例中,所述第一节点控制电路控制第一节点的电位,第二节点控制电路控制第二节点的电位,驱动输出电路控制通过驱动信号输出端输出驱动信号,进位信号输出电路通过进位信号输出端输出进位信号。

111.可选的,本发明至少一实施例所述的驱动电路可以为栅极驱动电路或发光控制信号生成电路,用于生成栅极驱动信号或发光控制信号,但不以此为限。

112.如图3所示,在图1所示的驱动电路的至少一实施例的基础上,第二节点包括第一个第二节点p21和第二个第二节点p22;本发明至少一实施例所述的驱动电路还包括:第一节点控制电路31、第二节点控制电路32、驱动输出电路33、进位信号输出电路34和储能电路35;

113.所述第一节点放噪电路11分别与p21和p22电连接,用于在p21的电位的控制下,控制所述第一节点p1与所述第二降噪电压端vr2之间连通,并在p22的电位的控制下,控制所述第一节点p1与所述第二降噪电压端vr2之间连通;

114.所述第一节点控制电路31分别与第一节点p1与输入端input电连接,用于根据所述输入端input提供的输入信号,控制所述第一节点p1的电位;

115.所述第二节点控制电路32分别与第一个第二节点p21、第二个第二节点p22、第一控制电压端vddo、第二控制电压端vdde、输入端input、第一节点p1和第一低电压端电连接,用于在所述第一控制电压端vddo提供的第一控制电压、所述输入信号和所述第一节点p1的电位的控制下,控制所述第一个第二节点p21的电位,在所述第二控制电压端vdde提供的第二控制电压、所述输入信号和所述第一节点p1的电位的控制下,控制第二个第二节点p22的电位;所述第一低电压端用于提供第一低电压lvgl;

116.所述驱动输出电路33分别与第一节点p1、第一个第二节点p21、第二个第二节点p22、时钟信号端、第二低电压端和驱动信号输出端gout电连接,用于在所述第一节点p1的电位的控制下,控制所述驱动信号输出端gout与所述时钟信号端之间连通,在所述第一个第二节点p21的电位的控制下,控制所述驱动信号输出端gout与所述第二低电压端之间连通,并在所述第二个第二节点p22的电位的控制下,控制所述驱动信号输出端gout与所述第二低电压端之间连通;

117.所述进位信号输出电路34分别与第一节点p1、第一个第二节点p21、第二个第二节点p22、时钟信号端、第二低电压端和进位信号输出端电连接out_c,用于在所述第一节点p1的电位的控制下,控制所述进位信号输出端out_c与所述时钟信号端之间连通,在所述第一个第二节点p21的电位的控制下,控制所述进位信号输出端out_c与所述第一低电压端之间连通,并在所述第二个第二节点p22的电位的控制下,控制所述进位信号输出端out_c与所述第一低电压端之间连通;

118.所述储能电路35分别与所述第一节点p1和驱动信号输出端gout电连接,用于储存电能,并控制所述第一节点p1的电位;

119.所述时钟信号端用于提供时钟信号clk,所述第二低电压端用于提供第二低电压vgl。

120.在图3所示的驱动电路的至少一实施例中,所述第一节点放噪电路11还可以与帧复位端t_rst电连接,用于在所述帧复位端t_rst提供的帧复位信号的控制下,对第一节点进行放噪。

121.本发明如图3所示的驱动电路的至少一实施例中,采用了两个第二节点:第一个第二节点p21和第二个第二节点p22,第二节点控制电路32控制p21的电位和p22的电位,驱动输出电路33在p1的电位、p21的电位和p22的电位的控制下,控制所述驱动信号输出端gout

输出驱动信号,进位信号输出电路34在p1的电位、p21的电位和p22的电位的控制下,控制所述进位信号输出端out_c输出进位信号。

122.如图4所示,在图3所示的驱动电路的至少一实施例的基础上,所述第一节点放噪电路11还可以分别与帧复位端t_rst和第三降噪电压端vr3电连接,用于在所述帧复位端t_rst提供的帧复位信号的控制下,控制所述第一节点p1与所述第三降噪电压端之间vr3连通;

123.所述第三降噪电压端vr3用于提供第三降噪电压,所述第三降噪电压的电压值在第三预定电压范围内。

124.如图5所示,在图4所示的驱动电路的至少一实施例的基础上,所述驱动输出电路33还与复位端reset电连接,所述驱动输出电路33用于在所述复位端reset提供的复位信号的控制下,控制所述驱动信号输出端gout与第二低电压端之间连通。

125.本发明图5所示的驱动电路的至少一实施例在工作时,所述驱动输出电路33在复位信号的控制下,控制所述驱动信号输出端gout输出第二低电压vgl。

126.如图6所示,在图1所示的驱动电路的至少一实施例的基础上,本发明至少一实施例所述的驱动电路还包括:第一节点控制电路31、第二节点控制电路32、驱动输出电路33、进位信号输出电路34和储能电路35;

127.所述第一节点控制电路31分别与第一节点p1与输入端input电连接,用于根据所述输入端input提供的输入信号,控制所述第一节点p1的电位;

128.所述第二节点控制电路32分别与第二节点p2、第一控制电压端vddo、输入端input、第一节点p1和第一低电压端电连接,用于在所述第一控制电压端vddo提供的第一控制电压、所述输入信号和所述第一节点p1的电位的控制下,控制所述第二节点p2的电位;第一低电压端用于提供第一低电压lvgl;

129.所述驱动输出电路33分别与第一节点p1、第二节点p2、复位端reset、时钟信号端、第二低电压端和驱动信号输出端gout电连接,用于在所述第一节点p1的电位的控制下,控制所述驱动信号输出端gout与所述时钟信号端之间连通,在所述第二节点p2的电位的控制下,控制所述驱动信号输出端gout与所述第二低电压端之间连通,并在所述复位端reset提供的复位信号的控制下,控制所述驱动信号输出端gout与所述第二低电压端之间连通;

130.所述进位信号输出电路34分别与第一节点p1、第二节点p2、时钟信号端、第一低电压端和进位信号输出端out_c电连接,用于在所述第一节点p1的电位的控制下,控制所述进位信号输出端out_c与所述时钟信号端之间连通,在所述第二节点p2的电位的控制下,控制所述进位信号输出端out_c与所述第一低电压端之间连通;

131.所述储能电路35分别与第一节点p1和驱动信号输出端gout电连接,用于储存电能,并控制第一节点p1的电位;

132.所述时钟信号端用于提供时钟信号clk,所述第二低电压端用于提供第二低电压vgl。

133.在图6所示的驱动电路的至少一实施例中,所述第一节点放噪电路11还可以与帧复位端t_rst电连接,用于在所述帧复位端t_rst提供的帧复位信号的控制下,对第一节点进行放噪。

134.本发明如图6所示的驱动电路的至少一实施例采用了一个第二节点p2,第二节点

控制电路32控制第二节点p2的电位,驱动输出电路33在第一节点p1、第二节点p2和复位信号的控制下,控制驱动信号输出端gout输出驱动信号,进位信号输出电路34在第一节点p1、第二节点p2和复位信号的控制下,控制进位信号输出端out_c输出进位信号。

135.如图7所示,在图5所示的驱动电路的至少一实施例的基础上,所述第一节点放噪电路11包括第一晶体管m1、第二晶体管m2、第三晶体管m3和第四晶体管m4;

136.所述第一节点控制电路31包括第五晶体管m5;

137.所述第二节点控制电路32包括第六晶体管m6、第七晶体管m7、第八晶体管m8、第九晶体管m9、第十晶体管m10、第十一晶体管m11;

138.所述驱动输出电路33包括第十二晶体管m12、第十三晶体管m13、第十四晶体管m14和第十五晶体管m15;

139.所述储能电路35包括存储电容c1;

140.所述进位信号输出电路34包括第十六晶体管m16、第十七晶体管m17和第十八晶体管m18;

141.m1的栅极与复位端reset电连接,m1的漏极与第一节点p1电连接,m1的源极与第三低电压端电连接;所述第三低电压端用于提供第三低电压vgl3;

142.m2的栅极与第一个第二节点p21电连接,m2的漏极与第一节点p1电连接,m2的源极与所述第三低电压端电连接;

143.m3的栅极与第二个第二节点p22电连接,m3的漏极与第一节点p1电连接,m3的源极与所述第三低电压端电连接;

144.m4的栅极与帧复位端t_rst电连接,m4的漏极与第一节点p1电连接,m4的源极与第一低电压端电连接;所述第一低电压端用于提供第一低电压lvgl;

145.m5的栅极和m5的漏极与输入端input电连接,m5的源极与第一节点p1电连接;

146.m6的栅极和m6的漏极都与第一控制电压端vddo电连接;

147.m7的栅极与第一节点p1电连接,m7的漏极与m6的源极电连接,m7的源极接入第一低电压lvgl;

148.m8的栅极与输入端input电连接,m8的漏极与m6的源极电连接,m8的漏极接入第一低电压lvgl;

149.m9的栅极和m9的漏极都与第二控制电压端vdde电连接;

150.m10的栅极与第一节点p1电连接,m10的漏极与m9的源极电连接,m10的源极接入第一低电压lvgl;

151.m11的栅极与输入端input电连接,m11的漏极与m9的源极电连接,m11的源极接入第一低电压lvgl;

152.m12的栅极与第一节点p1电连接,m12的漏极接入时钟信号clk,m12的源极与驱动信号输出端gout电连接;

153.m13的栅极与第一个第二节点p21电连接,m13的漏极与gout电连接,m13的源极接入第二低电压vgl;

154.m14的栅极与第二个第二节点p22电连接,m14的漏极与gout电连接,m14的源极接入第二低电压vgl;

155.m15的栅极与复位端reset电连接,m15的漏极与gout电连接,m15的源极接入第二

低电压vgl;

156.m16的栅极与p1电连接,m16的漏极接入clk,m16的源极与进位信号输出端out_c电连接;

157.m17的栅极与p21电连接,m17的漏极与out_c电连接,m17的源极接入第一低电压lvgl;

158.m18的栅极与p22电连接,m18的漏极与out_c电连接,m18的源极接入第一低电压lvgl;

159.c1的第一端与p1电连接,c1的第二端与gout电连接。

160.在图7所示的驱动电路的至少一实施例中,所有的晶体管都为n型薄膜晶体管,但不以此为限。

161.在图7所示的至少一实施例中,lvgl的电压值可以为

‑

11v,vgl的电压值可以为

‑

8v。

162.在图7所示的驱动电路的至少一实施例中,采用了两个下拉节点,vddo、vdde交替输出高电压信号,例如,每隔2s

‑

3s,vddo、vdde交替输出高电压信号。当vddo输出高电压信号时,vdde输出低电压信号;当vdde输出高电压信号时,vddo输出低电压信号。下面以vddo提供高电压信号,vdde提供低电压信号为例说明工作过程。

163.本发明如图7所示的驱动电路的至少一实施例在工作时,显示周期可以包括先后设置的输入阶段、输出阶段、复位阶段和输出截止保持阶段;

164.在输入阶段,input提供高电压信号,t_rst、vdde和reset提供低电压信号,vddo提供高电压信号,m5打开,以将p1的电位提升为高电压;m6打开,m7和m8都打开,p21的电位为低电压,m10和m11打开,p22的电位为低电压;m12和m16都打开,clk为低电压信号,gout和out_c都输出低电压信号;

165.在输出阶段,input提供低电压信号,t_rst、vdde和reset提供低电压信号,vddo提供高电压信号,clk为高电压信号,gout和out_c都输出高电压信号,通过c1自举拉升p1的电位;m5关断,m6打开,m7和m8都打开,p21的电位为低电压,m10和m11打开,p22的电位为低电压;

166.在复位阶段,input提供低电压信号,t_rst和vdde提供低电压信号,vddo提供高电压信号,reset提供高电压信号,m15打开,m1打开,以将p1的电位拉低;m6打开,m6和m7都关断,m9、m10和m11都关断,p21的电位为高电压;m13和m15都打开,gout输出低电压,m17打开,out_c输出低电压;

167.在输出截止保持阶段,input提供低电压信号,t_rst和vdde提供低电压信号,vddo提供高电压信号,reset提供低电压信号,p1的电位维持为低电压,p21的电位为高电压,m13和m17打开,gout和out_c输出低电压。

168.在图7所示的驱动电路的至少一实施例中,当m1的特性、m2的特性和m3的特性未漂移时,m1的阈值电压、m2的阈值电压和m3的阈值电压都为正值;

169.当m1的阈值电压负向偏移,m2的阈值电压负向偏移,m3的阈值电压负向偏移时,m1的阈值电压、m2的阈值电压和m3的阈值电压变为负值,在输入阶段和复位阶段,本发明至少一实施例通过增加vgl3的电压值,以防止m1、m2、m3中的至少一个漏电而使得p1的电位不能维持为高电压,从而导致gout和out_c不能在输出阶段输出高电压的情况,使得在输出阶

段,gout和out_c能够正常输出高电压。

170.经过对图7所示的驱动电路的至少一实施例进行仿真,可知当m1的阈值电压、m2的阈值电压和m3的阈值电压负偏至

‑

6v时,gout和out_c在输出阶段都能正常输出高电压,以提升阈值电压margin(范围)。

171.在图7所示的驱动电路的至少一实施例中,vgl3的电压值可以大于或等于

‑

8v而小于或等于

‑

4v,或者,更优选的,vgl3的电压值可以大于或等于

‑

7.5v而小于或等于

‑

4.5v,但不以此为限。

172.经过对图7所示的驱动电路的至少一实施例进行仿真,

173.当m1的阈值电压、m2的阈值电压、m3的阈值电压为

‑

3v,vgl3的电压值为

‑

4v时,在输出阶段,gout和out_c输出正常,噪声增加;

174.当m1的阈值电压、m2的阈值电压、m3的阈值电压为

‑

3v,vgl3的电压值为

‑

6v时,在输出阶段,gout和out_c输出正常,噪声增加;

175.m1的阈值电压、m2的阈值电压、m3的阈值电压为

‑

3v,vgl3的电压值为

‑

8v时,在输出阶段,gout和out_c输出正常,并减少延迟复位时间;

176.当m1的阈值电压、m2的阈值电压、m3的阈值电压为

‑

4.5v,vgl3的电压值为

‑

4v时,在输出阶段,gout和out_c输出多脉冲输出的情况;

177.当m1的阈值电压、m2的阈值电压、m3的阈值电压为

‑

4.5v,vgl3的电压值为

‑

6v时,在输出阶段,gout和out_c输出正常,噪声增加;

178.m1的阈值电压、m2的阈值电压、m3的阈值电压为

‑

4.5v,vgl3的电压值为

‑

8v时,在输出阶段,gout和out_c输出正常,没有延迟复位时间;

179.当m1的阈值电压、m2的阈值电压、m3的阈值电压为

‑

6v,vgl3的电压值为

‑

4v时,在输出阶段,gout和out_c输出正常,噪声增加;

180.当m1的阈值电压、m2的阈值电压、m3的阈值电压为

‑

6v,vgl3的电压值为

‑

6v时,在输出阶段,gout和out_c输出正常,噪声增加;

181.m1的阈值电压、m2的阈值电压、m3的阈值电压为

‑

6v,vgl3的电压值为

‑

8v时,在输出阶段,gout和out_c输出的信号的电位偏低。

182.根据如上仿真结构,可以根据m1的阈值电压、m2的阈值电压和m3的阈值电压负向偏移的程度来设置vgl3的电压值。

183.当m1的阈值电压、m2的阈值电压、m3的阈值电压为

‑

3v,vgl3的电压值为

‑

6v时,gout输出的驱动信号的波形如图8所示。

184.当m1的阈值电压、m2的阈值电压、m3的阈值电压为

‑

4.5v,vgl3的电压值为

‑

6v时,gout输出的驱动信号的波形如图9所示。

185.当m1的阈值电压、m2的阈值电压、m3的阈值电压为

‑

6v,vgl3的电压值为

‑

6v时,gout输出的驱动信号的波形如图10所示。

186.由图8

‑

图10所示,gout能够正常输出驱动信号。

187.图11所示的驱动电路的至少一实施例与图7所示的驱动电路的至少一实施例的区别在于:m4的源极与第三低电压端电连接;所述第一低电压端用于提供第三低电压vgl3。

188.与图7所示的驱动电路的至少一实施例相比,由于m4的源极接入vgl3(vgl3的电位高于lvgl的电位),本发明如11所示的驱动电路的至少一实施例的防止在输入阶段和输出

阶段,由于漏电而导致的p1的电位不能维持为有效电压的效果更好。

189.图12所示的驱动电路的至少一实施例与图7所示的驱动电路的至少一实施例的区别在于:不设置有m15。

190.如图13所示,在图6所示的驱动电路的至少一实施例的基础上,所述第一节点放噪电路11包括第一晶体管m1、第二晶体管m2、第四晶体管m4;

191.所述第一节点控制电路31包括第五晶体管m5;

192.所述第二节点控制电路32包括第六晶体管m6、第七晶体管m7和第八晶体管m8;

193.所述驱动输出电路33包括第十二晶体管m12、第十三晶体管m13和第十五晶体管m15;

194.所述储能电路35包括存储电容c1;

195.所述进位信号输出电路34包括第十六晶体管m16和第十七晶体管m17;

196.m1的栅极与复位端reset电连接,m1的漏极与第一节点p1电连接,m1的源极与第三低电压端电连接;所述第三低电压端用于提供第三低电压vgl3;

197.m2的栅极与第二节点p2电连接,m2的漏极与第一节点p1电连接,m2的源极与所述第三低电压端电连接;

198.m4的栅极与帧复位端t_rst电连接,m4的漏极与第一节点p1电连接,m4的源极与第一低电压端电连接;所述第一低电压端用于提供第一低电压lvgl;

199.m5的栅极和m5的漏极与输入端input电连接,m5的源极与第一节点p1电连接;

200.m6的栅极和m6的漏极都与第一控制电压端vddo电连接;

201.m7的栅极与第一节点p1电连接,m7的漏极与m6的源极电连接,m7的源极接入第一低电压lvgl;

202.m8的栅极与输入端input电连接,m8的漏极与m6的源极电连接,m8的漏极接入第一低电压lvgl;

203.m12的栅极与第一节点p1电连接,m12的漏极接入时钟信号clk,m12的源极与驱动信号输出端gout电连接;

204.m13的栅极与第二节点p2电连接,m13的漏极与gout电连接,m13的源极接入第二低电压vgl;

205.m15的栅极与复位端reset电连接,m15的漏极与gout电连接,m15的源极接入第二低电压vgl;

206.m16的栅极与p1电连接,m16的漏极接入clk,m16的源极与进位信号输出端out_c电连接;

207.m17的栅极与p2电连接,m17的漏极与out_c电连接,m17的源极接入第一低电压lvgl;

208.c1的第一端与p1电连接,c1的第二端与gout电连接。

209.在图13所示的驱动电路的至少一实施例中,所有的晶体管可以都为n型薄膜晶体管,但不以此为限。

210.在图13所示的至少一实施例中,lvgl的电压值可以为

‑

11v,vgl的电压值可以为

‑

8v。

211.本发明如图13所示的驱动电路的至少一实施例在工作时,显示周期可以包括先后

设置的输入阶段、输出阶段、复位阶段和输出截止保持阶段;

212.在输入阶段,input提供高电压信号,t_rst和reset提供低电压信号,vddo提供高电压信号,m5打开,以将p1的电位提升为高电压;m6打开,m7和m8都打开,p2的电位为低电压;m12和m16都打开,clk为低电压信号,gout和out_c都输出低电压信号;

213.在输出阶段,input提供低电压信号,t_rst和reset提供低电压信号,vddo提供高电压信号,clk为高电压信号,gout和out_c都输出高电压信号,通过c1自举拉升p1的电位;m5关断,m6打开,m7和m8都打开,p2的电位为低电压;

214.在复位阶段,input提供低电压信号,t_rst提供低电压信号,vddo提供高电压信号,reset提供高电压信号,m15打开,m1打开,以将p1的电位拉低;m6打开,m6和m7都关断,p2的电位为高电压;m13和m15都打开,gout输出低电压,m17打开,out_c输出低电压;

215.在输出截止保持阶段,input提供低电压信号,t_rst提供低电压信号,vddo提供高电压信号,reset提供低电压信号,p1的电位维持为低电压,p2的电位为高电压,m13和m17打开,gout和out_c输出低电压。

216.在图13所示的驱动电路的至少一实施例中,当m1的特性、m2的特性和m3的特性未漂移时,m1的阈值电压、m2的阈值电压和m3的阈值电压都为正值;

217.当m1的阈值电压负向偏移,m2的阈值电压负向偏移,m3的阈值电压负向偏移时,m1的阈值电压、m2的阈值电压和m3的阈值电压变为负值,在输入阶段和复位阶段,本发明至少一实施例通过增加vgl3的电压值,以防止m1、m2、m3中的至少一个漏电而使得p1的电位不能维持为高电压,从而导致gout和out_c不能在输出阶段输出高电压的情况,使得在输出阶段,gout和out_c能够正常输出高电压。

218.图14所示的驱动电路的至少一实施例与图13所示的驱动电路的至少一实施例的区别在于:m4的源极与第三低电压端电连接;所述第三低电压端用于提供第三低电压vgl3。

219.与图13所示的驱动电路的至少一实施例相比,由于m4的源极接入vgl3(vgl3的电位高于lvgl的电位),本发明如14所示的驱动电路的至少一实施例的防止在输入阶段和输出阶段,由于漏电而导致的p1的电位不能维持为有效电压的效果更好。

220.本发明实施例所述的显示装置包括降噪电压提供电路和上述的驱动电路;

221.所述降噪电压提供电路用于为第一降噪电压端提供第一降噪电压,为第二降噪电压端提供第二降噪电压,并使得所述第一降噪电压的电压值在第一预定电压值范围内,并使得所述第二降噪电压的电压值在第二预定电压值范围内。

222.本发明实施例所述的显示装置通过降噪电压提供电路提供第一降噪电压和第二降噪电压,当所述第一节点放噪电路包括的与第一节点电连接的晶体管的特性负向漂移时,可以通过设置第一降噪电压的电压值和第二降噪电压的电压值,以使得在输入阶段和输出阶段,不会发生所述第一节点放噪电路包括的晶体管漏电而使得第一节点的电位不能维持为有效电压的情况,从而能够在输入阶段和输出阶段,可以保证第一节点的电位为有效电压,使得驱动信号输出正常,利于实现高迁移率的驱动电路。

223.在具体实施时,所述第一节点放噪电路还分别与帧复位端、所述第一节点和第三降噪电压端电连接,用于在所述帧复位端提供的帧复位信号的控制下,控制所述第一节点与所述第三降噪电压端之间连通;

224.所述降噪电压提供电路还用于为所述第三降噪电压端提供第三降噪电压,以使得

所述第三降噪电压的电压值在第三预定电压范围内。

225.在输入阶段和输出阶段,所述降噪电压提供电路通过提升第三降噪电压,可以断开所述第一节点与第三降噪电压端之间的漏电通路。

226.本发明实施例所提供的显示装置可以为手机、平板电脑、电视机、显示器、笔记本电脑、数码相框、导航仪等任何具有显示功能的产品或部件。

227.以上所述是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明所述原理的前提下,还可以作出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。