1.本实用新型涉及计算机技术领域,特别是涉及一种主板及计算机设备。

背景技术:

2.目前,计算机主板中通常设置有中央处理单元(central processing unit,简称cpu)和紧凑型外设部件互连标准(compact peripheral component interconnect,简称cpci)连接器,cpu与cpci连接器通常通过pci桥片连接,以实现信号传输。具体地,由于部分cpu内部没有集成外设部件互连标准(peripheral component interconnect,简称pci)控制器,只有高速串行计算机扩展总线标准(peripheral component interconnect express,简称pcie)控制器,而传统的cpci连接器不具备实现支持高速信号的承载能力,无法直接与pcie控制器相连。由于pci桥片可以实现pcie与pci的转换,pcie控制器便可以通过pci桥片与传统的cpci连接器实现信号连接,因此需要在计算机主板中额外增加pci桥片,使用pci桥片实现pcie控制器与cpci连接器之间的信号传输,从而导致浪费主板空间及成本等问题。

3.综上,目前的计算机存在主板空间浪费及成本较高的问题。

技术实现要素:

4.鉴于上述问题,提出了克服上述问题或者至少部分地解决上述问题的一种主板及计算机设备,以解决现有计算机主板空间浪费及成本较高的问题。

5.为了解决上述问题,一方面,本实用新型公开了一种主板,包括:cpu和cpci连接器;其中,

6.所述cpu中集成有至少一个pcie控制器;

7.所述cpci连接器包括高速信号传输接口,所述高速信号传输接口为能够支持高频信号模拟带宽的接口;

8.所述pcie控制器通过所述高速信号传输接口与所述cpci连接器直接连接。

9.可选地,所述cpu集成了pcie 0控制器和pcie 1控制器,所述pcie0控制器直接与所述cpci连接器连接,所述pcie 1控制器与所述cpci连接器之间连接有网络控制器芯片。

10.可选地,所述pcie控制器与所述cpci连接器的所述高速信号传输接口之间通过pcie总线连接。

11.可选地,所述主板为标准6u欧式板卡类型或标准3u欧式板卡类型。

12.可选地,所述cpci连接器的接触电阻小于10mω。

13.可选地,所述cpci连接器的端接类型为直式通孔焊接。

14.可选地,所述主板还集成了数字量输入接口与数字量输出接口,所述数字量输入接口与所述数字量输出接口分别与所述cpci连接器电连接。

15.另一方面,本实用新型还公开了一种计算机设备,包括底板及上述的主板;

16.所述底板与所述主板通过所述cpci连接器电连接。

17.可选地,所述cpci连接器包括cpci插座或cpci插头;

18.所述cpci插座集成于所述主板上,所述cpci插头集成于所述底板上,所述pcie控制器与所述cpci插座电连接,所述cpci插座与所述cpci插头插接电连接;或,

19.所述cpci插座集成于所述底板上,所述cpci插头集成于所述主板上,所述pcie控制器与所述cpci插头电连接,所述cpci插座与所述cpci插头插接电连接。

20.本实用新型实施例包括以下优点:

21.本实用新型中提供一种主板,包括:cpu和cpci连接器;其中,cpu中集成有至少一个pcie控制器,cpci连接器包括高速信号传输接口,高速信号传输接口为能够支持高频信号模拟带宽的接口。pcie控制器通过高速信号传输接口与cpci连接器直接连接。相比传统方案而言,本实用新型实施例的cpci连接器包含支持高速信号传输的高速信号传输接口,该高速信号传输接口能够支持高频信号模拟带宽,进而能够接收pcie控制器传输的高频信号模拟带宽,因此,cpu中的pcie控制器可通过高速信号传输接口直接与cpci连接器相连,不需要额外的pci桥片。可见,本实用新型实施例既可以解决现有计算机主板中的pcie控制器无法直接与cpci连接器相连的问题,还可以节省主板的制板空间及成本,有效解决了现有主板空间浪费及成本较高的问题。

附图说明

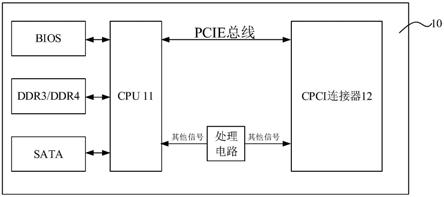

22.图1是本实用新型的一种主板的结构框图;

23.图2是本实用新型的另一种主板的结构框图;

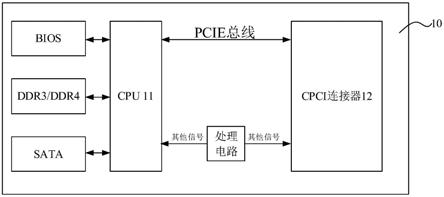

24.图3是本实用新型的计算机设备的结构框图;

25.图4是本实用新型的主板和底板的布置示意图。

具体实施方式

26.为使本实用新型的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本实用新型作进一步详细的说明。

27.参照图1,本实施例提供了一种主板10,包括:cpu 11和cpci连接器12;其中,

28.所述cpu 11中集成有至少一个pcie控制器;

29.所述cpci连接器12包括高速信号传输接口,所述高速信号传输接口为能够支持高频信号模拟带宽的接口;

30.所述pcie控制器通过所述高速信号传输接口与所述cpci连接器12直接连接。

31.可选地,cpu 11中可以集成两个x4模式的pcie控制器,可配置成六个x1模式的pcie控制器。cpci连接器12可以为h2系列高速背板cpci连接器,cpci连接器12包括高速信号传输接口,该高速信号传输接口为能够支持高频信号模拟带宽的接口,其传输速率可达3.125gbps,cpci连接器12还支持传输单端信号或差分信号。某些性能优异的cpci连接器12的传输速率甚至可达10gbps及以上。pcie控制器的信号传输接口通过高速信号传输接口与cpci连接器12直接连接,可将pcie控制器的高速信号传输至cpci连接器12。

32.本实用新型中提供一种主板10,如图1所示,包括:cpu 11和cpci连接器12;其中,cpu 11中集成有至少一个pcie控制器,cpci连接器12包括高速信号传输接口,pcie控制器与高速信号传输接口直接连接。相比传统方案而言,本实用新型实施例的cpci连接器支持

高速信号的传输,因此,cpu 10中的pcie控制器可直接与cpci连接器12的高速信号传输接口相连,不需要额外的pci桥片。可见,本实用新型实施例既可以解决现有计算机主板中的pcie控制器无法直接与cpci连接器12相连的问题,还可以节省主板的制板空间及成本,有效解决了现有主板空间浪费及成本较高的问题。

33.可选地,所述cpu 11集成了pcie 0控制器和pcie 1控制器,所述pcie0控制器直接与所述cpci连接器12连接,所述pcie 1控制器与所述cpci连接器12之间连接有网络控制器芯片13。

34.其中,pcie 1控制器可配置成两路x1模式的pcie控制器,pcie 1控制器与cpci连接器12之间连接网络控制器芯片,网络控制器芯片13可将pcie 1控制器的两路信号生成两路千兆以太网信号,再将以太网信号传输至cpci连接器12。pcie 0控制器可配置成四路x1模式的pcie控制器,pcie0控制器可直接与cpci连接器12连接,本实用新型实施例对pcie 0总线的用途不做限定,本领域技术人员可根据实际需求对pcie 0总线进行规划。

35.可选地,cpu 11为龙芯2k1000处理器。

36.其中,处理器中集成了两个pcie控制器,一个pcie控制器直接与cpci连接器12连接,另一个pcie控制器与cpci连接器12之间连接有网络控制器芯片13。此外,处理器中还可以集成有精简吉比特介质独立接口(reduced gigabit media independent interface,简称rgmii)、通用串行总线(universal serial bus,简称usb)2.0接口、控制器局域网络(controller area network,简称can)、平衡式多点接口(简称rs422)、标准串行数据接口(简称rs232)等功能接口,功能接口均与cpci连接器12连接,以实现不同功能接口的信号传输。此外,可以理解的是,由于pcie控制器的数据需要通过pcie总线进行传输,因此,pcie控制器与cpci连接器12通过pcie总线连接。

37.可选地,所述主板10为标准6u欧式板卡类型或标准3u欧式板卡类型。

38.其中,标准6u欧式板卡的尺寸为233.35mm

×

160mm,标准6u欧式板卡可设置八个槽位;标准3u欧式板卡的尺寸为100mm

×

160mm,标准3u欧式板卡可设置五个槽位。本实用新型实施例对主板10的尺寸不做限定,本领域技术人员可根据实际的尺寸及槽位需求设定主板10的具体尺寸。

39.可选地,所述cpci连接器12为h2系列高速背板cpci连接器。

40.其中,h2系列高速背板cpci连接器12具有支持高速信号的承载能力,可直接与pcie控制器相连,实现pcie高速信号的传输。而且,相比传统的压接cpci连接器而言,h2系列高速背板cpci连接器12支持焊接形式,提高了cpci连接器12的牢固性,能够承载更为恶劣的强振动环境。示例性地,本实用新型实施例中,所使用的cpci连接器12的接触电阻可以小于10mω,高速信号传输接口的差分信号对之间阻抗可以为100

±

10ω,高速信号传输接口的差分信号与地之间的阻抗可以为50

±

5ω。较小的接触电阻以及较小的传输阻抗均可以确保高速信号传输接口的传输速率达到3.125gbps。因此,本实用新型实施例的cpci连接器基于以上电学特性,将传统cpci连接器的接口(引脚)进行重定义,即将cpci连接器的部分接口重定义为高速信号传输接口,使得cpci连接器还可以支持10gbps甚至更高的模拟带宽,实现高速信号传输。

41.可选地,所述cpci连接器12的端接类型为直式通孔焊接。

42.其中,cpci连接器12的端接类型为直式通孔焊接,cpci连接器12可以为焊接在主

板上的插头或者插座。对于插头或者插座,均包括注塑的壳体以及封装固定在壳体内的金属插针。金属插针可以为壳体上伸出的直列插针,金属插针可以插入与主板上的焊孔中焊接固定,可以提升cpci连接器12的牢固性,使得cpci连接器12能够承载更为恶劣的强振动环境。

43.可选地,所述主板还集成了数字量输入接口与数字量输出接口,所述数字量输入接口与所述数字量输出接口分别与所述cpci连接器12电连接。

44.其中,主板还集成了数字量输入接口与数字量输出接口,数字量输入接口与数字量输出接口分别与cpci连接器12电连接,可通过cpci连接器12传输数字量输入接口与数字量输出接口的信号。本实用新型实施例既可以充分利用主板的制板空间,还可以增加主板的功能接口类型。当然,主板上还可以集成第三代双倍速内存(double data rate 3,简称ddr3)或第四代双倍速内存(double data rate 4,简称ddr4)、存储bios(basic input output system,基本输入输出系统)程序的非易失性存储器,显示接口及网络接口等,以及用于连接硬盘和光驱等设备的串行ata接口(serial ata,简称sata)、pcie 2.0、usb2.0、串行外设接口(serial peripheral interface,spi)、can、rs422等常用的主流外设接口,其中,ddr3内存设计可以选择使用小外形双列直插式内存模块(small outline dual in

‑

line memory module,简称so

‑

dimm);bios程序主要是为计算机提供最底层的、最直接的硬件设置和控制;处理电路可以为网络控制器芯片,网络控制器芯片与cpu、cpci控制器之间传输以太网信号。本实用新型实施例对主板上的设备及功能接口的数量及类型不做限定,本领域技术人员可根据实际需求裁剪或增加功能接口。

45.参照图3,本实施例提供了一种计算机设备,包括底板20和前述实施例中的主板10;

46.所述底板20与所述主板10通过所述cpci连接器12电连接。

47.本实施例中提供一种计算机设备,包括底板20和主板10,如图3所示,主板10包括:cpu 11和cpci连接器12;其中,cpu 11中集成有至少一个pcie控制器,cpci连接器12包括高速信号传输接口,pcie控制器与高速信号传输接口直接连接。相比传统方案而言,本实用新型实施例的cpci连接器12支持高速信号的传输,因此,cpu 11中的pcie控制器可直接与cpci连接器12的高速信号传输接口相连,不需要额外的pci桥片。可见,本实用新型实施例既可以解决现有计算机主板中的pcie控制器无法直接与cpci连接器相连的问题,还可以节省主板的制板空间及成本,有效解决了现有主板空间与成本浪费的问题。其中,底板20和主板10通过cpci连接器12电连接,可以实现主板10上的功能接口通过cpci连接器12与底板20连接,底板20上可连接对外接口板30和电源板40,如图3所示,从而可以实现对主板10功能接口的扩展使用。此外,在实际应用中,基于计算机设备的箱体尺寸及其内部组件的布局空间,可以将底板20和主板10按照图4的示意上下叠层设置,以节省计算机设备内部空间。当然,也可以在内部空间充足的情况下,将底板20和主板10并联设置在同一平面内。本实用新型实施例中对底板20和主板10的相对位置关系不做限定。

48.可选地,所述cpci连接器12包括cpci插座或cpci插头;

49.所述cpci插座集成于所述主板10上,所述cpci插头集成于所述底板20上,所述pcie控制器与所述cpci插座电连接,所述cpci插座与所述cpci插头插接电连接;或,

50.所述cpci插座集成于所述底板20上,所述cpci插头集成于所述主板10上,所述

pcie控制器与所述cpci插头电连接,所述cpci插座与所述cpci插头插接电连接。

51.其中,前述的cpci连接器12可以包括成对配套使用的cpci插座或cpci插头。当把cpci插座集成于主板10上时,相应地,cpci插头可以集成于底板20上,pcie控制器与cpci插座上插孔的针脚接触电连接,通过cpci插头的插针与cpci插座的插孔插接电连接,实现主板10与底板20的电连接,从而将pcie控制器的高速信号传输至底板20。反之,当把cpci插座集成于底板20上时,相应地,cpci插头可以集成于主板10上,pcie控制器与cpci插头的插针接触电连接,通过cpci插头的插针与cpci插座的插孔插接电连接,也是一种实现主板10与底板20之间高速信号传输的方式。

52.本说明书中的各个实施例均采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似的部分互相参见即可。

53.最后,还需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者终端设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者终端设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、物品或者终端设备中还存在另外的相同要素。

54.以上对本实用新型所提供的实施例进行了详细介绍,本文中应用了具体个例对本实用新型的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本实用新型的方法及其核心思想;同时,对于本领域的一般技术人员,依据本实用新型的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本实用新型的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。