半导体器件

1.相关申请的交叉引用

2.本技术要求于2020年5月22日提交的日本专利申请号2020

‑

090116的优先权,其内容通过引用由此并入本技术。

技术领域

3.本公开涉及半导体器件,并且可应用于例如具有电感器的半导体器件。

背景技术:

4.当在待被输入的电信号的电位彼此不同的两个电路之间传输电信号时,光电耦合器经常被用作光隔离器。光电耦合器具有发光元件(诸如发光二极管)和光接收元件(诸如光电晶体管),通过光传输元件将输入的电信号转换为光,并且通过光接收元件将该光返回到电信号,从而传输该电信号。

5.然而,由于光电耦合器具有发光元件和光接收元件,因此难以小型化。另外,当电信号的频率为高时,光电耦合器不能跟随电信号。作为用于解决这些问题的技术,已开发了一种技术,用于通过将两个电感器感应耦合的变压器来传输电信号。通过使用该变压器来构造隔离器。例如,公开了专利文件1(日本专利申请公开号2010

‑

219122)。

技术实现要素:

6.当通过将设置在半导体器件中的两个电感器感应耦合来传输电信号时,通过设置这两个电感器,半导体器件的尺寸可能变大。

7.在本公开的一个方面中,两个电感器各自被成形为曲折状以形成变压器。另外,通过使用变压器来构造隔离器。

8.根据以上半导体器件,可以降低其尺寸的增加。

附图说明

9.图1是根据实施例的半导体器件的平面图。

10.图2是图1中所示的半导体器件的横截面图。

11.图3是用于说明图1中所示的制造半导体器件的方法的横截面图。

12.图4是用于说明图1中所示的制造半导体器件的方法的横截面图。

13.图5是用于说明图1中所示的制造半导体器件的方法的横截面图。

14.图6是用于说明图1中所示的制造半导体器件的方法的横截面图。

15.图7是用于说明图1中所示的制造半导体器件的方法的横截面图。

16.图8是用于说明图1中所示的制造半导体器件的方法的横截面图。

17.图9是用于说明图1中所示的制造半导体器件的方法的横截面图。

18.图10是用于说明图1中所示的制造半导体器件的方法的横截面图。

19.图11是用于说明图1中所示的制造半导体器件的方法的横截面图。

20.图12是用于说明图1中所示的制造半导体器件的方法的横截面图。

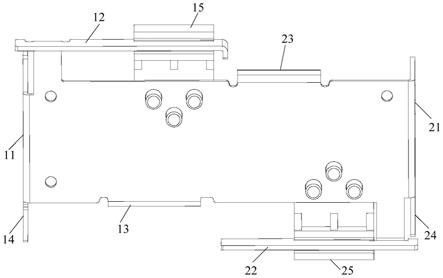

21.图13是图1中所示的两个电感器的平面图。

22.图14是第一修改示例中的电感器的平面图。

23.图15是第二修改示例中的电感器的平面图。

24.图16是示出实施例和第二修改示例中的电感器的相应电感值的图。

25.图17是示出实施例和第二修改示例中的电感器中的每个电感器的q值的图。

26.图18是第三修改示例中的电感器的平面图。

27.图19是第四修改示例中的电感器的平面图。

具体实施方式

28.在下文中,实施例和修改示例将参考附图来描述。然而,在以下描述中,相同的组件可以由相同的附图标记表示,并且其重复描述可以被省略。顺便提及,为了使说明清楚,附图可以示意性地表示与实际实施例相比的每个部分的宽度、厚度和形状等,但这仅是示例,并且示意性表示不用于限制本公开的解释。

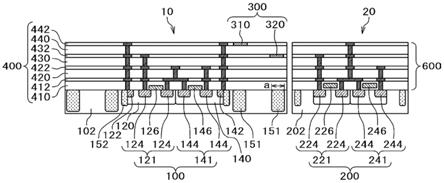

29.图1是根据实施例的半导体器件的示意性平面图。图2是示出图1中所示的半导体器件的配置的横截面图。

30.如图1中所示,半导体器件1具有第一半导体芯片10和第二半导体芯片20,并且半导体器件1配置了隔离器。在平面图中,在第一半导体芯片10的y轴方向上延伸的第一侧10a被布置为与在第二半导体芯片20的y轴方向上延伸的第一侧20a靠近并且相对。第一半导体芯片10包括第一电路100、第一电感器310和第二电感器320。第二半导体芯片20具有第二电路200。

31.在平面图中,第一电感器310和第二电感器320与第一侧10a靠近并且沿着第一侧10a延伸。第一电路100的至少一部分位于相对于第一电感器310和第二电感器320的、面向第一侧10a的第二侧10b。

32.第一电感器310和第二电感器320将变压器300配置为信号传输元件,并且通过相互感应耦合来相互传输电信号。电信号例如是数字信号,但可以是模拟信号。

33.第一电感器310连接到第一电路100,并且第二电感器320连接到第二半导体芯片20。第一电路100是传输电路。即,第一电感器310用作传输侧电感器,并且第二电感器320用作接收侧电感器。连接第二电感器320和第二半导体芯片20的布线例如是键合线521和522。第二电路200包括接收电路,并且经由键合线521和522连接到第二电感器320。

34.第一电路100包括:调制处理单元155,将数字信号调制为用于传输的信号;以及传输侧驱动器电路150,向第一电感器310输出经调制的信号。第二电路200包括:接收电路260,连接到第二电感器320;以及接收驱动器电路250(例如,栅极驱动器)。接收电路260将经调制的信号解调为数字信号。由接收电路260解调的数字信号被输出到接收驱动器电路250。

35.在第一电路100和第二电路200中,输入的电信号的电位彼此不同,但由于第一电感器310和第二电感器320通过使用感应耦合来传输和接收电信号,因此不会出现关于第一电路100和第二电路200的问题。即,第一电感器310和第二电感器320构造变压器。顺便提及,在图1配置中的“输入的电信号的电位彼此不同”的情况例如如下:

36.(a)电信号的幅度(指示0的电位和指示1的电位之间的差)彼此不同的情况;

37.(b)电信号的参考电位(指示0的电位)不同的情况;以及

38.(c)电信号的幅度彼此不同并且电信号的参考电位不同的情况。

39.如图2中所示,第一半导体芯片10的第一电路100形成在第一基板102上。这里,第一基板102是诸如硅基板的半导体基板。多层布线层400形成在第一基板102上。第一电感器310形成在多层布线层400上。第二电感器320形成在多层布线层400中,并且如图1中所示,在平面图中第二电感器320与第一电感器310不重叠。

40.第一半导体芯片10的第一电路100具有第一晶体管。第一晶体管包括第一导电类型的第一晶体管121和第二导电类型的第一晶体管141。第一导电类型的第一晶体管121形成在第二导电类型阱120中,并且具有各自用作源极和漏极的两个第一导电类型的杂质区124,以及栅极电极126。第二导电类型的第一晶体管141形成在第一导电类型阱140上,并且具有各自用作源极和漏极的两个第二导电类型的杂质区144,以及栅极电极146。栅极绝缘膜位于每个栅极电极126和146的下方。这两个栅极绝缘膜的厚度基本相等。第一晶体管121和141构造以上所提及的传输侧驱动器电路,例如,反相器。

41.第二导电类型的杂质区122形成在阱120中,并且第一导电类型的杂质区142形成在阱140中。提供接地电位作为第一导电类型的第一晶体管121的参考电位的布线连接到杂质区122,并且提供第二导电类型的第一晶体管141的参考电位的布线连接到杂质区142。

42.第二半导体芯片20的第二电路200形成在第二基板202中。这里,第二基板202是诸如硅基板的半导体基板。多层布线层600形成在第二基板202上。

43.第二电路200具有第二晶体管。第二晶体管还包括第一导电类型的第二晶体管221和第二导电类型的第二晶体管241。第一导电类型的第二晶体管221形成在第二导电类型阱220中,并且具有各自用作源极和漏极的两个第一导电类型的杂质区224,以及栅极电极226。第二导电类型的第二晶体管241形成在第一导电类型阱240中,并且具有各自用作源极和漏极的两个第二导电类型的杂质区244和栅极电极246。栅极绝缘膜位于每个栅极电极226和246的下方。如以上所描述的,第二晶体管221和241构造接收驱动器电路250和接收电路260。

44.第二导电类型的杂质区222形成在阱220中,并且第一导电类型的杂质区242形成在阱240中。提供第一导电类型的第二晶体管221的参考电位的布线连接到杂质区222,并且提供第二导电类型的第二晶体管241的参考电位的布线连接到杂质区242。

45.在图2中所示的示例中,第一晶体管121和141以及第二晶体管221和241具有相互不同的栅极绝缘膜,但也可以是相同的。

46.第一电感器310和第二电感器320是具有曲折形状并且形成在相互不同的布线层中的布线图案。第一电感器310例如位于上布线层442中,并且第二电感器320例如位于布线层432中,布线层432是在最上层之下的一层。

47.多层布线层400通过将绝缘层和布线层交替层叠t次(t≥3)或按顺序层叠更多次来形成。第二电感器320被设置在多层布线层400的第n布线层中。第一电感器310被设置在多层布线层的第m布线层(t≥m≥n 1)中,并且位于第二电感器320的上方。即,第一电感器310和第二电感器320形成在相互不同的布线层中。进一步地,位于第n布线层和第m布线层之间的布线层未被设置有位于第二电感器320上方的电感器。在本实施例中,多层布线层

400具有如下配置:绝缘层410、布线层412、绝缘层420、布线层422、绝缘层430、布线层432、绝缘层440和布线层442按顺序堆叠。这里,布线层412、422、432和442由绝缘膜和导体膜组成。绝缘层410、420、430和440可以具有在其中层叠多个绝缘膜的结构,或者也可以是单个绝缘膜。

48.位于布线层412、422、432和442中的布线是由镶嵌法形成的铜(cu)布线,并且被嵌入在每个沟槽中,该每个沟槽形成在布线层412、422、432和432的绝缘层中。焊盘(未示出)形成在最上布线上或在最上布线中。顺便提及,如以上所描述的布线层412、422、432和442中的至少一个布线层可以是铝合金布线。顺便提及,形成在布线层412、422、432和442中的布线经由嵌入在绝缘层410、420、430和440中的插塞彼此连接。

49.配置绝缘层和布线层的每个绝缘膜可以是二氧化硅(sio2)膜或低介电常数膜。低介电常数膜可以被设置为例如绝缘膜,该绝缘膜具有3.3或以下(优选2.9或以下)的相对介电常数。

50.键合焊盘161和162位于第一侧10a,面向第二半导体芯片20(与第二半导体芯片20对立)的一侧,并且第一电感器310和第二电感器320沿着第一侧10a并在键合焊盘161和162之间延伸。如以上所描述的,第一电路100位于第二侧10b,相对于第一电感器310和第二电感器320的一侧。第一电路100包括传输侧驱动器电路150。如以上所描述的,传输侧驱动器电路150由第一晶体管121和141的至少一部分(例如反相器的一部分)组成。第一电感器310的一端312连接到传输侧驱动器电路150。顺便提及,第一电感器310的另一端314连接到电源布线或接地布线。

51.接下来,将描述制造第一半导体芯片10的方法的概要。首先,将第一电路100形成在第一基板102上。接下来,将多层布线层400形成在第一基板102上。当多层布线层400被形成时,形成第一电感器310和第二电感器320。进一步地,第一电感器310经由被设置在多层布线层400中的布线连接到第一电路100。

52.下面将参考图3至图12更详细地描述第一半导体芯片10和第二半导体芯片20。图3是用于说明形成dti的过程的横截面图。图4是用于说明形成sti的过程的横截面图。图5是用于说明形成阱的过程的横截面图。图6是用于说明形成源极和漏极的过程的横截面图。图7是用于说明形成栅极的过程的横截面图。图8是用于说明形成绝缘层的过程的横截面图。图9是用于说明形成接触和第一绝缘层的过程的横截面图。图10是用于说明形成第一层的布线的过程的横截面图。图11是用于说明形成第二至第四层的布线的过程的横截面图。图12是用于说明形成保护膜的过程的横截面图。

53.如图3中所示,在第一基板102中形成dti(深沟槽隔离)151,dti 151具有与第一晶体管121和141的sti(浅沟槽隔离)152的沟槽相比更深的沟槽。dti 151的宽度(a)优选地比用于形成第一电感器310和第二电感器320的布线的每个宽度(b)宽,该第一电感器310和第二电感器320在dti 151中待被形成,并且更优选的是,“a”相对于“b”向右和向左更宽2μm至8μm。即,优选的是,“a”比“b”宽4μm至16μm。顺便提及,没有dti形成在第二基板202上。

54.接下来,如图4中所示,用于第一晶体管121和141中的每个晶体管的sti 152形成在第一基板102中或在第一基板102上。用于第二晶体管221和241中的每个晶体管的sti 252形成在第二基板202中或在第二基板202上。

55.接下来,如图5中所示,第二导电型阱120和第一导电型阱140形成在第一基板102

上或在第一基板102中。第二导电型阱220和第一导电型阱240形成在第二基板202上或在第二基板202中。

56.接下来,如图6中所示,在阱120中形成用作源极和漏极的第一导电类型的杂质区124和第二导电类型的杂质区122。在阱140中形成用作源极和漏极的第二导电类型的杂质区144和第一导电类型的杂质区142。在阱220中形成用作源极和漏极的第一导电类型的杂质区224和第二导电类型的杂质区222。在阱240中形成用作源极和漏极的第二导电类型的杂质区244和第一导电类型的杂质区242。

57.接下来,如图7中所示,栅极电极126和146通过在第一基板102上形成栅极绝缘膜并在栅极绝缘膜上形成导体膜来形成。栅极电极226和246通过在第二基板202上形成栅极绝缘膜并在栅极绝缘膜上形成导体膜来形成。

58.接下来,如图8中所示,在栅极电极126和146上形成绝缘层410作为布线中间层膜。在栅极电极226和246上形成绝缘层610作为布线中间层膜。

59.接下来,如图9中所示,在绝缘层410中形成接触孔之后,导体膜形成在接触孔中以形成接触411。其后,绝缘膜412a形成在接触411和绝缘层410上。在绝缘层610中形成接触孔之后,导体膜形成在接触孔中以形成接触611。其后,绝缘膜612a形成在接触611和绝缘层610上。

60.接下来,如图10中所示,沟槽形成在绝缘膜412a中,并且导体膜412b形成在沟槽中以形成布线层412。沟槽形成在绝缘膜612a中,并且导体膜612b形成在沟槽中以形成布线层612。

61.接下来,如图11中所示,层叠用于镶嵌布线的、氧化物膜的绝缘层420、430和440,并且通过镶嵌形成布线层422、432和442。布线层422、432和442形成以下:用于构造第一电感器310的布线;用于构造第二电感器320的布线;以及其他布线422b、432b和442b。层叠用于镶嵌布线的、氧化物膜的绝缘层620、630和640,并且通过镶嵌形成布线层622、632、642。

62.最后,如图12中所示,在布线层442上形成键合焊盘(未示出)和保护膜450。在布线层642上形成键合焊盘(未示出)和保护膜650。

63.将参考图13来描述第一电感器310和第二电感器320的形状,该第一电感器310和第二电感器320构造实施例中的变压器。图13是示出实施例中的两个电感器的平面图。

64.构造第一电感器310和第二电感器320的布线各自具有“b”的宽度,并且在平面图中以相等的间隔来(平行)布置。这里,构造第一电感器310和第二电感器320的布线之间的距离为“c”,并且“c”大于“b”。在平面图中,构造第一电感器310和第二电感器320的布线由相对于y轴方向成45度或135度的布线组成。另外,构造第一电感器310和第二电感器320的布线被形成为:以90

°

和270

°

弯曲的同时延长布线长度;交替地以90

°

和270

°

的弯曲角度来布置并且在y轴方向上延伸。

65.第二电感器320的两端电连接到键合焊盘161和162,并且第一电感器310连接到作为第一半导体芯片10的内部电路的传输侧驱动器电路150。调制信号从传输侧驱动器电路150被传输到第一电感器310,并且通过感应耦合被进一步传输到第二电感器320。连接到第二电感器320的键合焊盘161和162经由键合线521和522连接到第二半导体芯片20的键合焊盘261和262,并且由第二半导体芯片20解调。例如,当要求250v的耐受电压时,第一电感器310和第二电感器320之间的距离约为2μm长和10μm宽。

66.接下来,将描述本实施例的作用和效果。根据本实施例,它具有以下中的一个或多个。

67.(1)由于电感器要求相对大的面积,因此当第一电感器310和第二电感器320设置在第一半导体芯片10上以传输电信号时,容易使第一半导体芯片10变大。与其相反,在本实施例中,电感器形成为曲折形状。因此,每单位长度的电感值大于由直线形成的电感器的电感值,并且可以获得所要求的电感值,而无需在芯片的整个外围处布置电感器。因此,可以降低来自电感器和内部电路之间的爬电距离(由电感器和内部电路之间的爬电距离引起)的面积。

68.(2)通过减少布置电感器的边数,芯片内部电路和电感器之间的爬电距离要考虑的面积变小,并且其芯片面积变小。

69.(3)由于不存在布线以180

°

平行布置的区,因此可以形成变压器而未抵消布线之间生成的磁场。

70.<修改示例>

71.在下文中,将图示实施例的一些典型的修改示例。在以下修改示例的描述中,与上述实施例中的那些相同的参考标记可以被用于具有与上述实施例中描述的那些相同的配置和功能的部分。关于该部分的说明,上述实施例中的说明可以被适当地合并在技术上一致的范围内。另外,上述实施例的部分和多个修改示例的全部或部分可以在技术上一致的范围内被适当地组合应用。

72.(第一修改示例)

73.将参考图14来描述在第一修改示例中配置变压器的第一电感器310和第二电感器320的形状。图14是第一修改示例中的两个电感器的平面图。

74.第一电感器310和第二电感器320包括布线组301和布线组302。布线组301由以下来配置:由一定半径(r1)形成的半圆形布线3101;以及由半径(r1) 布线宽度(b) 布线间隔(c)组成的半径所形成的半圆形布线3201。布线3101和布线3201被形成为被布线间隔(c)均匀地分隔开。布线组302由以下来配置:由一定半径(r2)形成的半圆形布线3202;以及由半径(r2) 布线宽度(b) 布线间隔(c)组成的半径所形成的半圆形布线3102。布线3102和布线3202被形成为被布线间隔(c)均匀地分隔开。这里,如实施例中,“c”大于“b”。

75.布线组301和布线组302关于连接布线3101的两端的线303对称地布置。这里,线303在y轴方向上延伸。通过交替地连接布线组301和布线组302来构造第一电感器310和第二电感器320,并且被构造为在y轴方向上延伸。

76.在第一修改示例中,与实施例相比,布线没有边缘部分,并且高频信号中的电场集中小于实施例的高频信号中的电场集中,从而可以降低高频时的串联电阻。

77.(第二修改示例)

78.将参考图15至图17来描述在第二修改示例中构造变压器的第一电感器310和第二电感器320的形状。图15是第二修改示例中的两个电感器的平面图。图16是示出实施例和第二修改示例中的电感器的相应电感值的图。图17是示出实施例和第二修改示例中的电感器的相应q值的图。

79.如图15中所示,配置第一电感器310和第二电感器320的布线在平面图中由在x轴方向上延伸的布线和在y轴方向上延伸的布线组成。与实施例类似,配置第一电感器310和

第二电感器320的两条布线被形成为:以间隔“c”平行布置;弯曲90

°

和270

°

;以及在y轴方向上延伸。连续执行两次弯曲90

°

,并且然后连续执行两次弯曲270

°

,并且在重复这些步骤的同时,布线在y轴方向上延伸。当w1=l1和s1=s2时,每单位面积的电感值是大的。这里,“w1”是构造第一电感器310和第二电感器320的布线在x轴方向上的长度。“l1”是构造第一电感器310和第二电感器320的两个布线在y轴方向上的相应长度。“s1”是构造第二电感器320的布线在y轴方向上之间的间隔。“s2”是构造第一电感器310的布线在y轴方向上之间的间隔。s1优选为30μm或以上。

80.图16的纵轴指示电感值,图16的横轴指示布线密度。如图16中所示,在第二修改示例中,当w1=l1时,电感值与实施例的电感值几乎相同。在图16中,“a”指示实施例的电感值,并且“b”指示第二修改示例的电感值。在该情况中,在第二修改示例中,耦合系数和电阻值比在实施例中的大。图17的横轴指示q值,图17的纵轴指示频率。q值也称为q因子。如图17中所示,实施例的q值大于第二修改示例的q值。在图17中,“a”指示实施例的q值,并且“b”指示第二修改示例的q值。

81.(第三修改示例)

82.将参考图18来描述在第三修改示例中配置变压器的第一电感器310和第二电感器320的形状。图18是第三修改示例中的两个电感器的平面图。

83.构造第一电感器310和第二电感器320的布线由以下组成:在x轴方向上延伸的布线;以及在平面图中在相对于y轴方向成45度的方向上延伸的布线。与实施例类似,构造第一电感器310和第二电感器320的两个布线以相等的间隔来布置。进一步地,构造第一电感器310和第二电感器320的两个布线被形成为以90

°

、135

°

、225

°

和270

°

弯曲并且通过重复该弯曲来在y轴方向上延伸。

84.(第四修改示例)

85.将参考图19来描述在第四修改示例中配置变压器的第一电感器310和第二电感器320的形状。图19是第四修改示例中的两个电感器的平面图。

86.与实施例类似,在宏观的区域中,构造第一电感器310和第二电感器320的布线在平面图中由相对于y轴方向成45度或135度的布线组成。进一步地,构造第一电感器310和第二电感器320的布线被形成为:在以90

°

和270

°

弯曲的同时,延长相应布线长度;交替地以90

°

和270

°

的相应弯曲角度来布置;并且在y轴方向上延伸。

87.另一方面,在微观区域中,构造第一电感器310和第二电感器320的布线不由在平面图中相对于y轴方向成45度或135度的布线组成,而是由在x轴方向上延伸的布线和在轴向上延伸的布线组成。进一步地,构造第一电感器310和第二电感器320的两个布线被形成为:以90

°

和270

°

弯曲;以及通过重复该弯曲在相对于y轴方向成45

°

的方向上延伸。然而,在宏观区域中的布线的每个折叠部分处的微观区域,在90

°

是连续的或者270

°

是连续的,并且这导致布线的延伸。当以90

°

和90

°

、或270

°

和270

°

重复折叠角时,布线长度优选为30μm或以上。

88.使用光耦合器将光隔离器合并在一个封装中是困难的,而本公开的隔离器能够多通道集成。因此,例如,可以使反相器系统小型化。即,系统可以在诸如电机控制、隔离式dc

‑

dc、ups(不间断电源)、显示和照明控制的应用中小型化。

89.进一步地,可以与igbt集成或被集成到mcu。与mcu集成可以在诸如开关电源、医疗

器件、led照明和诸如车身系统和动力传动系统的车载式器件的应用中将系统小型化。

90.已基于实施例和修改示例具体描述了由本公开者做出的公开内容。然而,本公开不限于以上所提及的实施例和修改示例,并且可以以各种方式变化或改变。

91.例如,示例已在实施例中说明,其中第一半导体芯片10设置有传输电路、第一电感器310和第二电感器320,并且第二半导体芯片20设置有接收电路。第一半导体芯片10可以设置有接收电路、第一电感器310和第二电感器320,并且第二半导体芯片20可以设置有传输电路。在该情况中,第二电感器320用作传输侧电感器,并且第一电感器310用作接收侧电感器。

92.进一步地,在实施例中,通过将半导体器件划分为两个半导体芯片来形成半导体器件,但半导体器件可以形成在一个半导体芯片上。在该情况中,第一基板102由soi(绝缘体上硅)基板形成,并且第一电路100和第二电路200形成在第一基板102上。元件分离膜嵌入在第一基板102的硅层中。元件分离膜的下端到达第一基板102的绝缘层。元件分离膜使第一电路100和第二电路200绝缘。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。