一种纵向bcd器件及其制备方法

技术领域

1.本发明涉及单片集成工艺技术领域,尤其涉及一种纵向bcd器件及其制备方法。

背景技术:

2.bcd(bipolar

‑

cmos

‑

dmos)集成工艺是一种单片集成工艺技术,将bipolar(双极晶体管)、cmos(互补金属氧化物半导体场效应管)和dmosfet(双扩散金属氧化物半导体场效应管)器件同时制作在同一芯片上。它综合了各器件自身的优点,使其具有各自分立时的良好性能。整合过的bcd 工艺,可大幅降低功率耗损,提高系统性能,节省成本,可靠性更好。

3.dmosfet主要有两种类型:横向双扩散金属氧化物半导体场效应管ldmosfet和垂直双扩散金属氧化物半导体场效应管vdmosfet。目前,较为成熟的bcd工艺为平面结构,与平面结构工艺兼容的dmosfet通常采用ldmosfet。由ldmosfet要达到很高的耐压时,结构中需要设计漂移区(漂移区的杂质浓度比较低),使得漏极区占有较大的面积,同时也导致器件的导通电阻增加。vdmosfet的耐压非常高,其结构为纵向结构,漏极从晶圆背面引出,不适合与平面结构的集成电路相结合,兼容性较差。

技术实现要素:

4.本发明的目的是解决现有ldmosfet漏极区占用面积大、导通电阻较大以及vdmosfet兼容性较差的问题,提供一种纵向bcd器件的结构及其制备方法。

5.为实现上述目的,本发明采用以下技术方案:一种纵向bcd器件,包括n型衬底;在所述n型衬底上表面形成的n型外延层;在所述n型外延层通过局部氧化隔离形成的氧化层;所述n型外延层内依次设有p

‑

body区和hvpw区;所述p

‑

body区和hvpw区的注入离子均为p型离子;所述p

‑

body区的上表面设置有n 接触区,形成vdmosfet器件的源极,在p

‑

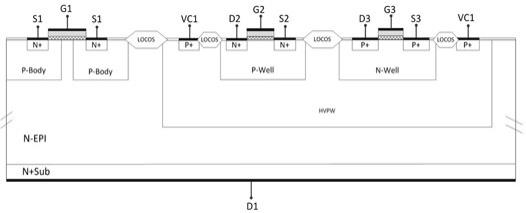

body区的上表面且位于n 接触区的一侧自下至上设置有栅氧化层和多晶硅层,所述栅氧化层和多晶硅层部分覆盖p

‑

body区上表面,形成vdmosfet器件的栅极;vdmosfet器件的漏极从n型衬底背面引出;所述hvpw区内依次设有p

‑

well区和n

‑

well区;所述p

‑

well区的注入离子为p型离子,所述n

‑

well区的注入离子为n型离子;所述p

‑

well区的上表面设置有两个n 接触区,形成cmos中nmos器件的漏极和源极,在p

‑

well区的上表面且位于两个n 接触区之间设置栅氧化层和多晶硅层,形成cmos中nmos器件的栅极;所述n

‑

well区的上表面设置有两个p 接触区,形成cmos中pmos器件的漏极和源极,在n

‑

well区的上表面且位于两个p 接触区之间设置栅氧化层和多晶硅层,形成cmos中

pmos器件的栅极;在hvpw区的上表面且位于p

‑

well区的左侧区域、位于n

‑

well区的右侧区域分别设置有p 接触区,形成hvpw的引出端。

6.进一步地,所述hvpw区内设置有hvnw区,所述hvnw区位于p

‑

well区的右侧,且n

‑

well区设置在hvnw区内,在所述hvnw区的上表面且位于n

‑

well区的左侧和右侧分别设置有n 接触区,形成hvnw的引出端。

7.进一步地,所述n型衬底的电阻率为0.002~0.004ohm*cm。

8.进一步地,所述n型外延层的厚度为6.4~6.8um,电阻率为1.0~1.2ohm*cm。

9.进一步地,所述氧化层通过locos局部氧化隔离实现,厚度为7600~9300埃。

10.上述纵向bcd器件的制备方法包括以下步骤:步骤一、选取晶向为<100>的n型衬底;步骤二、在n型衬底上生长n型外延层;步骤三、在n型外延层表面进行局部氧化工艺,实现局部氧化隔离,形成氧化层;步骤四、利用hvpw的光罩,通过光刻工艺在n型外延层内形成hvpw区,通过离子注入工艺对hvpw区注入硼离子;步骤五、利用p

‑

well的光罩,通过光刻工艺形成p

‑

well的离子注入区域,对其进行p型离子注入,形成p

‑

well区;利用n

‑

well的光罩,通过光刻工艺形成n

‑

well的离子注入区域,对其进行n型离子注入,形成n

‑

well区;其中n

‑

well区和p

‑

well区的工艺顺序可互换;步骤六、在n型外延层上生长栅氧化层,并在栅氧化层上淀积多晶硅层,利用栅极的光罩,通过光刻工艺定义出栅极区域,并对栅极的多晶硅层进行刻蚀,形成vdmosfet器件、cmos中pmos器件和nmos器件的栅极;步骤七、利用p

‑

body的光罩,通过自对准光刻工艺形成p

‑

body的离子注入区域,对其进行p型离子注入,形成p

‑

body区;步骤八、在p

‑

body区和p

‑

well区,分别利用n 的光罩,通过自对准光刻工艺形成n 的离子注入区域,对其进行n型离子注入,形成n 接触区,形成vdmosfet器件的源极、cmos中nmos器件的漏极和源极;在n

‑

well区、hvpw区,利用p 的光罩,通过自对准光刻工艺形成p 的离子注入区域,对其进行p型离子注入,形成p 接触区,分别形成cmos中pmos器件的漏极和源极、hvpw区的引出端;其中n 接触区和p 接触区的工艺顺序可互换;步骤九、形成中间介质层、接触孔和金属层;步骤十、根据vdmosfet器件的背面减薄工艺对n型衬底的下端面进行减薄,减薄后对其进行镀金,将vdmosfet器件的漏极从对n型衬底的下端面引出。

11.进一步地,步骤四中形成hvpw区后,还包括形成hvnw区的步骤:在hvpw区利用hvnw深n阱的光罩,通过光刻工艺形成hvnw区,再对hvnw区域进行离子注入;步骤八中,在p

‑

body区、p

‑

well区和hvnw区,分别利用n 的光罩,通过自对准光刻工艺形成n 的离子注入区域,对其进行n型离子注入,形成n 接触区,形成vdmosfet器件的源极、cmos中nmos器件的漏极和源极、hvnw的引出端;在n

‑

well区、hvpw区,利用p 的光罩,通过自对准光刻工艺形成p 的离子注入区域,对其进行p型离子注入,形成p 接触区,分别形成cmos中pmos器件的漏极和源极、hvpw区的引出端。其中n 接触区和p 接触区的工艺顺序可互换;

进一步地,所述hvnw区的离子注入为磷,离子注入能量为70~90kev,离子注入剂量为8e13cm

‑2~9.5e13cm

‑2。

12.进一步地,步骤四中,hvpw区的离子注入能量为80~100kev,离子注入剂量为1.7e13cm

‑2~2.0e13cm

‑2。

13.进一步地,步骤十中,晶圆背面减薄后的厚度为150~180um,镀金的材料为ti/ni/ag。

14.与现有技术相比,本发明具有如下有益效果:1.本发明提出一种纵向bcd器件,该器件的dmosfet采用的是vdmosfet,且漏极是从bcd器件的背面引出。在相同耐压下,此结构不仅可以大大的减小芯片面积,提高芯片利用率,同时还可降低导通电阻。

15.2.本发明纵向bcd器件在cmos器件区域增加深p阱hvpw,使得hvpw与n型外延层n

‑

epi之间形成二极管。当vdmosfet器件正常工作时,使得n

‑

epi与hvpw之间形成的二极管反向截止,不能出现反向击穿。该种设置避免了vdmosfet的漏极加电压时对bcd中的cmos器件造成的影响。

16.3.本发明纵向bcd器件增加了一层hvnw深n型阱,hvnw深n阱调节与hvpw之间形成的二极管的反向耐压,主要用于防止cmos中pmos的n

‑

well与hvpw之间形成的二极管反向击穿,影响pmos的正常工作。

附图说明

17.图1为本发明实施例一中纵向bcd器件结构示意图;图2为本发明实施例一纵向bcd器件制备方法中步骤二示意图;图3为本发明实施例一纵向bcd器件制备方法中步骤三示意图;图4为本发明实施例一纵向bcd器件制备方法中步骤四示意图;图5为本发明实施例一纵向bcd器件制备方法中步骤五示意图;图6为本发明实施例一纵向bcd器件制备方法中步骤六示意图;图7为本发明实施例一纵向bcd器件制备方法中步骤七示意图;图8为本发明实施例一纵向bcd器件制备方法中步骤八示意图;图9为本发明实施例一纵向bcd器件制备方法中步骤九示意图;图10为本发明实施例一纵向bcd器件制备方法中步骤十示意图;图11为本发明实施例二中纵向bcd器件的结构示意图;图12为本发明实施例二的纵向bcd器件制备方法中步骤三示意图;图13为本发明实施例二的纵向bcd器件制备方法中步骤四示意图;图14为本发明实施例二的纵向bcd器件制备方法中步骤八示意图。

具体实施方式

18.下面结合附图和具体实施方式对本发明进行详细说明。本领域技术人员应当理解的是,这些实施方式仅仅用来解释本发明的技术原理,目的并不是用来限制本发明的保护范围。

19.本发明提出一种纵向bcd器件,该纵向bcd器件的dmosfet采用的是vdmosfet,且漏

极是从bcd器件的背面引出。在相同耐压下,此结构不仅可以大大的减小芯片面积,提高芯片利用率,同时还可降低导通电阻。

20.实施例一图1所示为纵向bcd器件的结构示意图,以n型的平面vdmosfet器件为例,也可以是沟槽或超结等结构的vdmosfet器件。纵向bcd器件可实现降低导通电阻和缩小芯片面积的效果,但同时存在一个问题,vdmosfet的漏极加电压,会对bcd器件中的cmos器件造成影响。因此,需要在cmos器件区域增加深p阱hvpw,使得hvpw与n型外延层n

‑

epi之间形成二极管。当vdmosfet器件正常工作时,使得n

‑

epi与hvpw之间形成的二极管反向截止,且不能出现反向击穿,因此,n

‑

epi与hvpw之间形成的二极管的反向击穿电压需大于vdmosfet的击穿电压。另外,此结构是在vdmosfet器件的基础之上,对cmos器件区域增加一层深p阱hvpw的实现工艺,此工艺通常采用:光刻

‑

刻蚀

‑

离子注入(或者扩散),目前的工艺技术比较成熟,实现起来相对简单,不会增加工艺的难度。该图中g1为vdmosfet器件的栅极;d1为vdmosfet器件的漏极;s1为vdmosfet器件的源极;g2为cmos中nmos器件的栅极;d2为cmos中nmos器件的漏极;s2为cmos中nmos器件的源极;g3为cmos中pmos器件的栅极;d3为cmos中pmos器件的漏极;s3为cmos中pmos器件的源极;vc1为hvpw的引出端。该实施例中的纵向bcd器件具体结构如下,包括:n型衬底;在n型衬底上表面形成的n型外延层;在n型外延层上表面通过局部氧化隔离形成的氧化层;n型外延层内依次设有p

‑

body区和hvpw区;p

‑

body区和hvpw区的注入离子均为p型离子;p

‑

body区的上表面设置有n 接触区,形成vdmosfet器件的源极,在p

‑

body区的上表面且位于n 接触区的一侧自下至上设置有栅氧化层和多晶硅层,栅氧化层和多晶硅层部分覆盖p

‑

body区上表面,形成vdmosfet器件的栅极;vdmosfet器件的漏极从n型衬底背面引出;hvpw区内依次设有p

‑

well区和n

‑

well区;p

‑

well区的注入离子为p型离子,n

‑

well区的注入离子为n型离子;p

‑

well区的上表面设置有两个n 接触区,形成cmos中nmos器件的漏极和源极,在p

‑

well区的上表面且位于两个n 接触区之间设置栅氧化层和多晶硅层,形成cmos中nmos器件的栅极;n

‑

well区的上表面设置有两个p 接触区,形成cmos中pmos器件的漏极和源极,在n

‑

well区的上表面且位于两个p 接触区之间设置栅氧化层和多晶硅层,形成cmos中pmos器件的栅极;在hvpw区的上表面且位于p

‑

well区的左侧区域、位于n

‑

well区的右侧区域分别设置有p 接触区,形成hvpw的引出端。

21.上述纵向bcd器件的制备方法包括以下步骤:步骤一、根据vdmosfet器件的电性要求,选取晶向为<100>的n型衬底,其电阻率约为0.002~0.004ohm*cm;步骤二、在n型衬底上生长n型外延层n

‑

epi,n

‑

epi的厚度和电阻率是由vdmosfet

器件的源漏击穿电压和导通电阻决定,n型外延层的厚度为6.4~6.8um,电阻率为1.0~1.2ohm*cm,如图2所示;步骤三、在n

‑

epi上进行局部氧化工艺,实现locos局部氧化隔离,其氧化层厚度为7600~9300埃,如图3所示;步骤四、先利用hvpw的光罩,通过光刻工艺形成hvpw的离子注入区域,再通过离子注入工艺对其hvpw区域进行离子注入,hvpw注入的离子为硼,注入能量为80~100kev,注入剂量为1.7 e 13cm

‑2~2.0 e 13cm

‑2,如图4所示;步骤五、形成cmos器件中的背栅区,其中,nmos器件利用p

‑

well的光罩,通过光刻工艺形成p

‑

well的离子注入区域,对其进行p型离子注入,形成p

‑

well区;pmos器件利用n

‑

well的光罩,通过光刻工艺形成n

‑

well的离子注入区域,对其进行n型离子注入,形成n

‑

well区。其中p

‑

well区和n

‑

well区的工艺顺序可互换,如图5所示;步骤六、生长栅氧化层,在其之上淀积多晶硅层,利用栅极的光罩,通过光刻工艺定义栅极区域,再通过刻蚀工艺去除多余的栅氧化层和多晶硅,形成vdmosfet器件、cmos中pmos器件和nmos器件的栅极,如图6所示;步骤七、形成vdmosfet器件中的背栅区,利用p

‑

body的光罩,通过自对准光刻工艺形成p

‑

body的离子注入区域,对其进行p型离子注入,形成p

‑

body区,如图7所示;步骤八、在p

‑

body区和p

‑

well区,分别利用n 的光罩,通过自对准光刻工艺形成n 的离子注入区域,对其进行n型离子注入,形成n 接触区,形成vdmosfet器件的源极、cmos中nmos器件的漏极和源极;在n

‑

well区、hvpw区,利用p 的光罩,通过自对准光刻工艺形成p 的离子注入区域,对其进行p型离子注入,形成p 接触区,分别形成cmos中pmos器件的漏极和源极、hvpw区的引出端。其中n 接触区和p 接触区的工艺顺序可互换,如图8所示;步骤九、后续的工艺为常规工艺,如中间介质层、接触孔和金属层的形成等,完成晶圆正面的所有工艺,如图9所示;步骤十、根据vdmos的背面减薄工艺对其晶圆背面进行减薄,减薄后的厚度约为150~180um,减薄之后对其进行镀金,镀金的材料为ti/ni/ag,vdmos的漏极d1从晶圆背面引出,如图10所示。

22.实施例二该实施例在实施例一的纵向bcd器件基础上,增加了一层hvnw深n型阱,主要作用是防止cmos中pmos的n

‑

well与hvpw之间形成的二极管反向击穿,影响pmos的正常工作。由于n

‑

well主要用于调节pmos的沟道参数,于此同时,很难兼顾与hvpw的反向耐压,因此增加一层hvnw深n阱去调节与hvpw之间形成的二极管的反向耐压,其反向耐压必须要大于pmos的击穿耐压。如图11所示,vc2为hvnw的引出端,该实施例中的纵向bcd器件具体结构如下,包括:n型衬底;在n型衬底上表面形成的n型外延层;在n型外延层上表面通过局部氧化隔离形成的氧化层;n型外延层内依次设有p

‑

body区和hvpw区;p

‑

body区和hvpw区的注入离子均为p型离子;p

‑

body区的上表面设置有n 接触区,形成vdmosfet器件的源极,在p

‑

body区的上

表面且位于n 接触区的一侧设置有栅氧化层和多晶硅层,栅氧化层和多晶硅层部分覆盖p

‑

body区上表面,形成vdmosfet器件的栅极;vdmosfet器件的漏极从n型衬底背面引出;hvpw区内设有p

‑

well区和hvnw区,hvnw区位于p

‑

well区的右侧,且n

‑

well区设置在hvnw区内;p

‑

well区的注入离子为p型离子,n

‑

well区注入有n型离子;p

‑

well区的上表面设置有两个n 接触区,形成cmos中nmos器件的漏极和源极,在p

‑

well区的上表面且位于两个n 接触区之间设置栅氧化层和多晶硅层,形成cmos中nmos器件的栅极;在hvnw区的上表面且位于n

‑

well区的左侧和右侧分别设置有n 接触区,形成hvnw的引出端。

23.n

‑

well区的上表面设置有两个p 接触区,形成cmos中pmos器件的漏极和源极,在n

‑

well区的上表面且位于两个p 接触区之间设置栅氧化层和多晶硅层,形成cmos中pmos器件的栅极;在hvpw区的上表面且位于p

‑

well区的左侧区域、位于n

‑

well区的右侧区域分别设置有p 接触区,形成hvpw的引出端。

24.该实施例中的纵向bcd器件在实施例一结构的基础之上,增加了一层hvnw深n型阱,主要作用是防止cmos中pmos的n

‑

well与hvpw之间形成的二极管反向击穿,影响pmos的正常工作。由于n

‑

well主要用于调节pmos的沟道参数,于此同时,很难兼顾与hvpw的反向耐压,因此增加一层hvnw深n阱去调节与hvpw之间形成的二极管的反向耐压,其反向耐压必须要大于pmos的击穿耐压。

25.该实施例中的纵向bcd器件的制备方法包括以下步骤:步骤一、根据vdmosfet器件的电性要求,选取晶向为<100>的n型衬底,其电阻率约为0.002~0.004ohm*cm;步骤二、在n型衬底上生长n型外延层n

‑

epi,n

‑

epi的厚度和电阻率是由vdmosfet器件的源漏击穿电压和导通电阻决定,n型外延层的厚度为6.4~6.8um,电阻率为1.0~1.2ohm*cm;步骤三、如图12所示,在n

‑

epi上进行局部氧化隔离工艺,实现locos局部氧化隔离,由于要实现hvnw与pmos的隔离,其locos氧化隔离区增加;步骤四、先利用hvpw的光罩,通过光刻工艺形成hvpw的离子注入区,再通过离子注入工艺对其hvpw区进行离子注入,hvpw注入的离子为硼,注入的能量为80~100kev,注入的剂量为1.7e13cm

‑2~2.0e13cm

‑2;如图13所示,形成hvpw区之后,需要增加一层hvnw深n阱的光罩,通过光刻工艺形成hvnw区,再通过离子注入对hvnw区进行离子注入,其hvnw注入的离子为磷,注入能量为70~90kev,注入剂量为8e13cm

‑2~9.5e13cm

‑2;步骤五、形成cmos器件中的背栅区,其中,nmos器件利用p

‑

well的光罩,通过光刻工艺形成p

‑

well的离子注入区,对其进行p型离子注入,形成p

‑

well区;pmos器件利用n

‑

well的光罩,通过光刻工艺形成n

‑

well的离子注入区,对其进行n型离子注入,形成n

‑

well区;其中p

‑

well区和n

‑

well区的工艺顺序可互换;步骤六、生长栅氧化层,在其之上淀积多晶硅层,利用栅极的光罩,通过光刻工艺定义栅极区域,再通过刻蚀工艺去除多余的栅氧化层和多晶硅层,形成vdmosfet器件、cmos中pmos器件和nmos器件的栅极;

步骤七、形成vdmosfet器件中的背栅区,利用p

‑

body的光罩,通过自对准光刻工艺形成p

‑

body的离子注入区域,对其进行p型离子注入,形成p

‑

body区;步骤八、如图14所示,在p

‑

body区、p

‑

well区和hvnw区,分别利用n 的光罩,通过自对准光刻工艺形成n 的离子注入区域,对其进行n型离子注入,形成n 接触区,形成vdmosfet器件的源极、cmos中nmos器件的漏极和源极、hvnw的引出端;在n

‑

well区、hvpw区,利用p 的光罩,通过自对准光刻工艺形成p 的离子注入区域,对其进行p型离子注入,形成p 接触区,分别形成cmos中pmos器件的漏极和源极、hvpw区的引出端;其中n 接触区和p 接触区的工艺顺序可互换;步骤九、后续的工艺为常规工艺,如中间介质层、接触孔和金属层的形成等,完成晶圆正面的所有工艺;步骤十、根据vdmosfet器件的背面减薄工艺对其晶圆背面进行减薄,减薄后的厚度约为150~180um,减薄之后对其进行镀金,镀金的材料为ti/ni/ag,vdmosfet的漏极d1从晶圆背面引出。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。