1.本发明涉及一种用于测试配置在硅晶圆上的集成电路的方法及系统。

背景技术:

2.在硅晶圆上制造集成电路。硅晶圆包括大量的集成电路,通常是数千个。

3.测试集成电路包括借由确保晶体管正确连接在一起以形成所寻求的功能来检查其功能性。制造集成电路的过程可能会在一个或多个晶体管上或在连接处引起各种故障。必须侦测这些故障,因为它们可能会损害集成电路的性能。

4.一些集成电路由逻辑门、逻辑触发器及至少一个可重写存储器(例如,闪存)组成。

5.一些集成电路具有可选择地参数化的内部频率,内部频率由逻辑门使用,并且用于对所有逻辑触发器及可重写存储器的运作进行定时。

6.可重写存储器的访问时间是必须被测试及证明合格的重要元素。通常,增加可重写存储器的频率频率,直到在可重写存储器的输出处获得与期望内容不对应的数据为止。

7.当在整个集成电路中使用相同的内部频率时,无法增加频率频率以表征可重写存储器的访问时间,因为这样的内部频率的频率的增加也可能导致逻辑门或触发器的故障失效,这会使可重写存储器的访问时间的合格性的结果是错误的。

8.本发明旨在可判定由内部频率来进行定时的包含在集成电路中的可重写存储器的访问时间,所述集成电路也由逻辑触发器及逻辑门组成。

技术实现要素:

9.为此,依据第一形态,本发明提出一种用于测试集成电路的系统,该集成电路包括逻辑门、逻辑触发器及可重写存储器,该集成电路包括内部频率,该内部频率由该逻辑门使用来对所有该逻辑门及该可重写存储器的运作进行定时,该集成电路可配置成处于称为扫描链(scan chain)模式的操作模式中,其中该触发器的所有部件一个接一个地连成一串,以便测试该逻辑门及该触发器的操作,其特征在于该系统包括:

10.用于将该集成电路置于该扫描链模式中的机构;

11.用于使该可重写存储器与该逻辑门及该逻辑触发器隔离的机构;

12.用于借由外部频率对用于使该可重写存储器与该逻辑门及该逻辑触发器隔离的机构进行定时的机构;

13.用于改变该外部频率的周期性的机构;

14.用于读取该可重写存储器的内容并且用于将该数值与预定数值进行比较的机构;

15.用于依据该比较的结果来判定该可重写存储器的访问时间的机构。

16.本发明也有关于一种用于测试集成电路的方法,该集成电路包括逻辑门、逻辑触发器及可重写存储器,该集成电路包括内部频率,该内部频率由该逻辑门使用且用于对所有该逻辑触发器及该可重写存储器的操作进行定时,该集成电路可配置成处于称为扫描链模式的操作模式中,其中该触发器的所有部件一个接一个地连成一串,以便测试该逻辑门

及该触发器的操作,其特征在于该方法包括下列步骤:

17.将该集成电路置于该扫描链模式中;

18.使该可重写存储器与该逻辑门及该逻辑触发器隔离;

19.借由外部频率对用于使该可重写存储器与该逻辑门及该逻辑触发器隔离的装置进行定时;

20.改变该外部频率的周期性;

21.读取该可重写存储器的内容并将该数值与预定数值进行比较;

22.依据该比较的结果来判定该可重写存储器的访问时间。

23.因此,可以借由利用该扫描链模式来判定该可重写存储器的访问时间,同时从而避免必须添加专用系统。

24.依据本发明的特定实施例,该隔离机构由设置在用于控制该可重写存储器的寻址的至少一个缓存器及用于控制该可重写存储器的读取的缓存器的输入及输出处的多任务器组成。因此,取决于该常用扫描链模式或读取该访问时间测量模式的周期是在操作中,该可重写存储器的输入分别与该电路的其余部分隔离或连接至该控制缓存器。依据本发明的特定实施例,控制该可重写存储器的寻址的该缓存器的输出连接至设置在该可重写存储器的输入处的该多任务器的输入。

25.因此,在该读取周期期间,保持先前加载该寻址控制缓存器中的数值。在此模式中,它是可判定的与该读取控制缓存器的启动有关的访问时间。

26.依据本发明的特定实施例,控制该可重写存储器的寻址的该缓存器的输出连接至逆变器,该逆变器的输出连接至设置在该可重写存储器的输入处的该多任务器的输入。

27.因此,在该读取周期期间,使先前加载该寻址控制缓存器中的数值成倒数。在此模式中,它是可判定的与该寻址控制缓存器的启动有关的访问时间及与该读取控制缓存器有关的访问时间。

28.依据本发明的特定实施例,设置在该控制缓存器的输入处的该多任务器由第一逻辑信号来进行控制,并且设置在该控制缓存器的输出处的该多任务器由与该第一逻辑信号不同的第二逻辑信号来进行控制。

29.因此,设置在该控制缓存器的输出处的该多任务器是被使用于在简单扫描链模式中,使该可重写存储器与该电路的其余部分隔离,并且被使用于在访问时间测量模式中的读取周期期间,使该可重写缓存器连接至该控制缓存器。设置在该控制缓存器的输入处的该多任务器仅在访问时间测量模式中使用,以在该读取周期期间控制该缓存器的内容。

30.依据本发明的特定实施例,该可重写存储器的输出连接至另一个多任务器,而该另一个多任务器连接至输出缓存器。

31.因此,可捕获在该可重写存储器中读取的数值,以便接下来将其传送至测试器,测试器能够将其与期望数值进行比较。

32.本发明也有关于储存在信息载体上的计算机程序,该程序包括在该程序被加载计算机系统并由该计算机系统执行时用于使用该前述方法的指令。

附图说明

33.通过阅读以下示范实施例的说明,上述本发明的特征以及其它特征将变得更加清

楚,其中该说明是相对于附图进行的,其中:

34.图1显示了用于测试硅晶圆上的集成电路的系统;

35.图2显示了依据本发明的测试装置的架构;

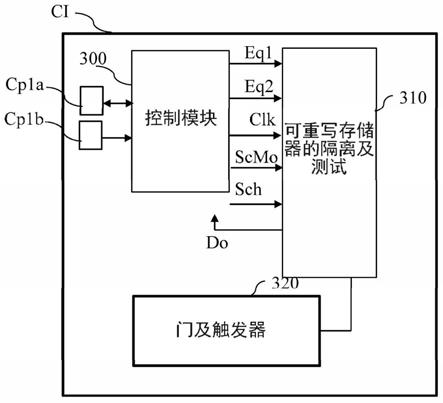

36.图3显示了依据本发明的集成电路的架构;

37.图4显示了依据本发明的用于隔离及测试可重写存储器的模块的架构的第一示例;

38.图5显示了依据本发明的第一示范实施例中由用于隔离及测试可重写存储器的模块所使用的信号的时序图;

39.图6显示了依据本发明的用于隔离及测试可重写存储器的模块的架构的第二示例;

40.图7显示了依据本发明的第二示范实施例中由用于隔离及测试可重写存储器的模块所使用的信号的时序图;

41.图8显示了依据本发明的用于隔离及测试可重写存储器的模块的架构的第三示例;

42.图9显示了依据本发明的第三示范实施例中由用于隔离及测试可重写存储器的模块所使用的信号的时序图;

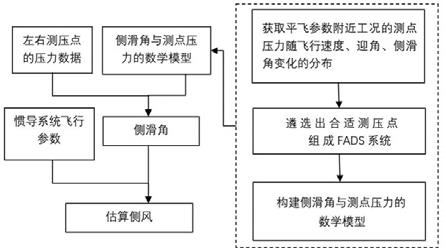

43.图10显示了依据本发明的算法的示例。

具体实施方式

44.图1显示用于测试硅晶圆上的集成电路的系统。

45.在图1中,测试器te使用与同时被测试的一组集成电路的矩形区域接触的复数个探针卡来测试硅晶圆dut的集成电路ci。

46.测试器te例如是用于控制一个或多个探针卡的计算机。测试器te测试集成电路是否符合规格,并且可以配置及调整集成电路的参数。

47.每个集成电路具有至少两个接触区域,每个接触区域在图1中用黑色正方形来表示,所述接触区域用于测试集成电路。测试器te使用一个探针来控制各种测试,并且使用一个探针来提供外部频率,以表征包含在集成电路中的可重写存储器的访问时间。在图1中,借由包括探针cp1a、cp1b、cp2a及cp2b的探针卡来同时测试两个集成电路。当然,同时测试大量的集成电路,图1中的示例仅仅是对实际状况的简化。同样地,出于简化的原因,在图1中仅显示七个集成电路。当然,在硅晶圆dut上存在大量的集成电路。

48.为了侦测集成电路中的故障,必须要检查集成电路功能的性能。功能由一组逻辑门及连接来执行。功能的性能由其输入端的信号来判定。一种方法包括在集成电路的一个特定状态下将集成电路的一个或多个功能的所有或一些触发器一个接一个地连成一串。这种分组称为“扫描链”。由于是触发器的情况,例如,它们将在每个频率的事件下进行更新。因此,触发器将更新其后面的触发器,并将由其前面的触发器来进行更新:此动作将称为“扫描加载(scan loading)”。借由固定触发器的数值,可以固定集成电路的各种组合云(combinatorial clouds)的输入。组合云由一组不执行开关功能的逻辑门组成。

49.为了捕获组合云的输出,可停用触发器的连锁,使得其输入直接连接至组合云的输出。借由将一个事件(例如,一个频率)施加至所有触发器,更新所有触发器:此动作将称

的信号处于高电平时,并且当称为捕获的信号处于高电平时,信号eq2处于高电平。

71.信号scmo是控制扫描链模式的信号。

72.捕获信号是常用的扫描捕获信号。

73.信号scan_taa是在希望表征可重写存储器410的访问时间时依据本发明使用的信号。

74.用于隔离及测试可重写存储器的模块310包括三个控制缓存器420、421及422。

75.控制缓存器420是可以程序化、抹除可重写存储器410并且可以将可重写存储器410置于低功耗模式及可重写存储器410的内部测试模式中的缓存器。

76.控制缓存器420是控制可重写存储器410的寻址的缓存器。

77.控制缓存器422是控制可重写存储器410的读取的缓存器。

78.多任务器400的输出连接至控制缓存器421的输入。控制缓存器421的输出连接至多任务器403的第一输入及多任务器400的第一输入。

79.当信号eq2处于高电平时,控制缓存器420的输出被导向控制缓存器421的输入。当信号eq2处于低电平时,连接至多任务器400的第二输入的表示为fon1的信号被导向控制缓存器421的输入。

80.信号fon1表示在集成电路的常用操作期间(也即,当可重写存储器410非正在测试的访问时间时)施加在控制缓存器421的输入上的信号。

81.多任务器401的输出连接至控制缓存器422。控制缓存器422的输出连接至多任务器404的第一输入。

82.当信号eq2处于高电平时,连接至多任务器401的第一输入的信号act被导向控制缓存器422的输入。当信号eq2处于低电平时,连接至多任务器401的第二输入的表示为fon2的信号被导向控制缓存器422的输入。

83.信号act是启动可重写存储器410的控制以在控制缓存器421所提供的存储器地址处读取其内容的信号。

84.信号fon2表示在集成电路的常用操作期间(也即,当可重写存储器410非正在测试的访问时间时)施加在控制缓存器422的输入上的信号。

85.外部频率clk及信号sch被传送至控制缓存器420、421及422。

86.信号sch是用于借由扫描链将所需数值加载至控制缓存器420、421及422的信号。

87.多任务器402、403及404的第二输入连接至表示为in的信号。信号in的功能是停用功能。

88.多任务器402由信号scmo控制,而多任务器403及404由信号eq1控制。

89.当信号scmo处于高电电平时,并且当信号“scan_taa”处于低电平时或者当捕获信号处于低电平时,信号eq1处于高电平。

90.捕获信号是用于控制扫描链的捕获的常用信号。

91.多任务器402、403及404的输出连接至可重写存储器410。

92.当信号eq1处于高电平时,信号in被导向可重写存储器410。当信号eq1处于低电平时,控制缓存器421的输出被导向可重写存储器410。

93.当信号eq1处于高电平时,信号in被导向可重写存储器410。当信号eq1处于低电平时,控制缓存器422的输出被导向可重写存储器410。

94.当信号scmo处于高电平时,信号in被导向可重写存储器410。当信号scmo处于低电平时,控制缓存器420的输出被导向可重写存储器410。

95.可重写存储器410的输出连接至多任务器405的第一输入。多任务器405的第二输入连接至表示为otr的信号。

96.在常用扫描链模式中使用的情况下,可重写存储器410的输出不能连接至扫描链,因为不可能预测其数值。信号otr可以将已知且可控制的数据重新导向输出缓存器430。

97.多任务器405的输出连接至输出缓存器430的输入,输出缓存器430由外部频率clk来控制。

98.在对可重写存储器410的访问时间进行测试期间,将从控制缓存器输出的数据传送至控制模块300。

99.图5显示在依据本发明的第一示范实施例中由用于隔离及测试可重写存储器的模块所使用的信号的时序图。

100.图5显示来自外部频率clk的信号、信号eq1及eq2、从控制缓存器421输出的信号421_out、从控制缓存器422输出的信号422_out、从多任务器403输出的信号403_out、从多任务器404输出的信号404_out、从可重写存储器410输出的信号410_out以及从输出缓存器430输出的信号do。

101.控制缓存器421由频率clk的上升边缘来触发,控制缓存器422由频率clk的下降边缘来触发。

102.从控制缓存器421输出的地址是预定地址add1。当信号eq1变为低电平且信号eq2变为高电平时,只要信号eq1保持在低电平且信号eq2保持在高电平,信号403_out就变成有效的且表示地址add1。可重写存储器410的地址add1被寻址。

103.当信号eq1变为低电平且信号eq2变为高电平时,信号404_out在外部频率clk的下一个上升边缘时变成有效的且表示在地址add1处读取可重写存储器410的内容的命令,并且只要信号eq1保持在低电平且信号eq2保持在高电平,就会保持在有效状态中。

104.在地址add1处的可重写存储器410的内容d在表示可重写存储器410的访问时间的延迟ta下出现在输出410_out处。

105.然后,数据d在频率clk的下一个上升边缘时出现在输出缓存器430的输出do。

106.因此,当外部频率clk的周期pe变成小于可重写存储器410的访问时间时,在地址add1处的可重写存储器410的内容d不再出现在可重写存储器410的输出,并且数据d在频率clk的下一个上升边缘时不再出现在输出缓存器430的输出do。

107.图6显示依据本发明的用于隔离及测试可重写存储器的模块的架构的第二示例。

108.用于隔离及测试可重写存储器的模块310包括多任务器600、601、602、603及604,其在表征可重写存储器610的访问时间期间隔离可重写存储器610。

109.多任务器600及601由信号eq2控制。当信号scmo处于高电平时,当称为“scan_taa”的信号处于高电平时,并且当称为捕获的信号处于高电平时,信号eq2处于高电平。

110.信号scmo是控制扫描链模式的信号。

111.捕获信号是常用扫描捕获信号。

112.信号scan_taa是在希望表征可重写存储器610的访问时间时依据本发明使用的信号。

113.用于隔离及测试可重写存储器的模块310包括三个控制缓存器620、621及622。

114.控制缓存器620是可以程序化、抹除可重写存储器610并且可以将可重写存储器610置于低功耗模式及用于可重写存储器610的内部测试的模式中的缓存器。

115.控制缓存器621是控制可重写存储器610的寻址的缓存器。

116.控制缓存器622是控制可重写存储器610的读取的缓存器。

117.多任务器600的输出连接至控制缓存器621。控制缓存器621的输出连接至多任务器603的第一输入及逆变器640的输入,逆变器640的输出连接至多任务器600的第一输入。

118.当信号eq2处于高电平时,控制缓存器621的反相输出被导向控制缓存器621的输入。当信号eq2处于低电平时,连接至多任务器600的第二输入的表示为fon1的信号被导向控制缓存器621的输入。

119.信号fon1表示在集成电路的常用操作期间(也即,当可重写存储器610非正在测试的访问时间时)施加至控制缓存器621的输入的信号。多任务器601的输出连接至控制缓存器622。控制缓存器622的输出连接至多任务器604的第一输入。

120.当信号eq2处于高电平时,连接至多任务器601的第一输入的信号act被导向控制缓存器622的输入。当信号eq2处于低电平时,连接至多任务器601的第二输入的表示为fon2的信号被导向控制缓存器622的输入。

121.信号act是启动可重写存储器610的控制以在控制缓存器621所提供的存储器地址处读取其内容的信号。

122.信号fon2表示在集成电路的常用操作期间(也即,当可重写存储器610非正在测试的访问时间时)施加至控制缓存器621的输入的信号。外部频率clk及信号sch被传送至控制缓存器620、621及622。

123.信号sch是用于借由扫描链将所需数值加载至控制缓存器620、621及622的信号。

124.多任务器602、603及604的第二输入连接至表示为in的信号。信号in的功能是停用功能。

125.多任务器602由信号scmo控制,而多任务器603及604由信号eq1控制。

126.当信号scmo处于高电电平时,并且当信号“scan_taa”处于低电平时或者当捕获信号处于低电平时,信号eq1处于高电平。

127.捕获信号是用于控制扫描链的捕获的常用信号。

128.多任务器602、603及604的输出连接至可重写存储器610。

129.当信号eq1处于高电平时,信号in被导向可重写存储器610。当信号eq1处于低电平时,控制缓存器621的输出被导向可重写存储器610。

130.当信号eq1处于高电平时,信号in被导向可重写存储器610。当信号eq1处于低电平时,控制缓存器622的输出被导向可重写存储器610。

131.当信号scmo处于高电平时,信号in被导向可重写存储器610。当信号scmo处于低电平时,控制缓存器620的输出被导向可重写存储器610。

132.可重写存储器610的输出连接至多任务器605的第一输入。多任务器605的第二输入连接至表示为otr的信号。

133.在常用扫描链模式中使用的情况下,可重写存储器610的输出不能连接至扫描链,因为不可能预测其数值。信号otr可以将已知且可控制的数据重新导向输出缓存器630。

134.多任务器605的输出连接至输出缓存器630的输入,输出缓存器630由外部频率clk来控制。

135.在对可重写存储器610的访问时间进行测试期间,将从控制缓存器输出的数据传送至控制模块300。

136.图7显示在依据本发明的第二实施例中由用于隔离及测试可重写存储器的模块所使用的信号的时序图。

137.图7显示外部频率信号clk、信号eq1及eq2、从控制缓存器621输出的信号621_out、从控制缓存器622输出的信号622_out、从多任务器603输出的信号603_out、从多任务器604输出的信号604_out、从可重写存储器610输出的信号610_out以及从输出缓存器630输出的信号do。

138.控制缓存器621由频率clk的上升边缘来触发,控制缓存器622由频率clk的下降边缘来触发。

139.当信号eq2处于电平1时,控制缓存器621的输出借由逆变器门640连接至其输入,从控制缓存器621输出的地址在每个上升边缘处从地址ad1改变为地址ad1的补码,或在每个上升边缘处从地址ad1的补码改变为地址ad1。

140.从控制缓存器621输出的地址是预定地址ad1或其补码!ad1。当信号eq1变为低电平且信号eq2变为高电平时,只要信号eq1保持在低电平且信号eq2保持在高电平,信号603_out就变成有效的且表示地址ad1或其补码!ad1。可重写存储器610的地址ad1及地址!ad1被寻址。

141.这种配置可以在访问时间为最大的配置中测试可重写存储器610的访问时间。

142.当信号eq1变为低电平且信号eq2变为高电平时,信号604_out在外部频率clk的下一个上升边缘时变成有效的且表示在地址!ad1处及在随后的上升边缘时在地址ad1处读取可重写存储器610的内容的命令,并且只要信号eq1保持在低电平且信号eq2保持在高电平,就会保持在有效状态中。

143.在地址!ad1处的可重写存储器610的内容!d在表示可重写存储器610的访问时间的延迟ta下出现在输出610_out处,并且在频率clk的随后上升边缘时,在地址ad1处的可重写存储器610的内容d在表示可重写存储器610的访问时间的相同的延迟ta’下出现在输出610_out处。

144.然后,数据项d或!d在频率clk的下一个上升边缘时出现在输出缓存器430的输出do。

145.因此,当外部频率clk的周期pe变成小于可重写存储器410的访问时间时,在地址ad1处的可重写存储器410的内容d不再出现在可重写存储器410的输出,并且数据项d在频率clk的下一个上升边缘时不再出现在输出缓存器630的输出do。

146.图8显示依据本发明的用于隔离及测试可重写存储器的模块的架构的第三示例。

147.用于隔离及测试可重写存储器的模块310包括内部测试模块840及多任务器850、800、801、802、803及804,其在表征可重写存储器810的访问时间期间隔离可重写存储器810。用于隔离及测试可重写存储器的模块310包括三个控制缓存器820、821及822。

148.内部测试模块840可以表征由控制缓存器820、821及822传送的每个数据项对可重写存储器810的访问时间的影响。内部测试模块840由信号eq2控制。当信号scmo处于高电平

时,当称为“scan_taa”的信号处于高电平时,并且当称为捕获的信号处于高电平时,信号eq2处于高电平。

149.多任务器850、800及801由信号eq2控制。

150.信号scmo是控制扫描链模式的信号。

151.捕获信号是常用扫描捕获信号。

152.信号scan_taa是在希望表征可重写存储器810的访问时间时依据本发明使用的信号。

153.控制缓存器820是可以程序化、抹除可重写存储器810并且可以将可重写存储器810置于低功耗模式及用于可重写存储器810的内部测试的模式中的缓存器。

154.多任务器850的输出连接至控制缓存器820。控制缓存器820的输出连接至多任务器802的第一输入。

155.多任务器850的第一输入连接至内部测试模块840的输出846,而多任务器850的第二输入连接至信号fon1。

156.当信号eq2处于高电平时,内部测试模块840的输出846连接至控制缓存器820的输入。当信号eq2处于低电平时,表示为fon1的信号被导向控制缓存器820的输入。

157.信号fon1表示在集成电路的常用操作期间(也即,当可重写存储器810非正在测试的访问时间时)施加在控制缓存器820的输入上的信号。

158.多任务器801的输出连接至控制缓存器822。控制缓存器822的输出连接至多任务器804的第一输入。

159.多任务器800的输出连接至控制缓存器821。控制缓存器821的输出连接至多任务器803的第一输入。

160.当信号eq2处于高电平时,内部测试模块840的输出844连接至控制缓存器821的输入。当信号eq2处于高电平时,连接至多任务器800的第二输入的表示为fon1的信号被导向控制缓存器821的输入。

161.信号fon1表示在集成电路的常用操作期间(也即,当可重写存储器810非正在测试的访问时间时)施加在控制缓存器821的输入上的信号。

162.多任务器801的输出连接至控制缓存器822。控制缓存器822的输出连接至多任务器804的第一输入。

163.当信号eq2处于高电平时,内部测试模块840的输出842连接至控制缓存器822的输入。当信号eq2处于低电平时,连接至多任务器801的第二输入的表示为fon2的信号被导向控制缓存器822的输入。

164.输出842是启动可重写存储器810的控制以在控制缓存器821所提供的存储器地址处读取其内容的信号。

165.信号fon2表示在集成电路的常用操作期间(也即,当可重写存储器810非正在测试的访问时间时)施加在控制缓存器821的输入上的信号。外部频率clk及信号sch被传送至控制缓存器820、821及822。

166.信号sch是用于通过扫描链将所需数值加载至控制缓存器820、821及822的信号。

167.多任务器802、803及804的第二输入连接至表示为in的信号。信号in的功能是停用功能。

168.多任务器802由信号scmo控制,而多任务器803及804由信号eq1控制。

169.当信号scmo处于高电电平时,并且当信号“scan_taa”处于低电平时或者当捕获信号处于低电平时,信号eq1处于高电平。

170.捕获信号是用于控制扫描链的捕获的常用信号。

171.多任务器802、803及804的输出连接至可重写存储器810。

172.当信号eq1处于高电平时,信号in被导向可重写存储器810。当信号eq1处于低电平时,控制缓存器821的输出被导向可重写存储器810。

173.当信号eq1处于高电平时,信号in被导向可重写存储器810。当信号eq1处于低电平时,控制缓存器822的输出被导向可重写存储器810。

174.当信号scmo处于高电平时,信号in被导向可重写存储器810。当信号scmo处于低电平时,控制缓存器820的输出被导向可重写存储器810。

175.可重写存储器810的输出连接至多任务器805的第一输入。多任务器805的第二输入连接至表示为otr的信号。

176.在常用扫描链模式中使用的情况下,可重写存储器810的输出不能连接至扫描链,因为不可能预测其数值。信号otr可以将已知且可控制的数据重新导向输出缓存器830。

177.多任务器805的输出连接至输出缓存器830的输入,输出缓存器830由外部频率clk来控制。

178.在对可重写存储器810的访问时间进行测试期间,将从控制缓存器输出的数据传送至内部测试模块840。

179.图9显示依据本发明的第三示范实施例中由用于隔离及测试可重写存储器的模块所使用的信号的时序图。

180.图9显示来自外部频率clk的信号、信号eq1及eq2、从控制缓存器821输出的信号821_out、从控制缓存器822输出的信号822_out、从多任务器803输出的信号803_out、从多任务器804输出的信号804_out、从可重写存储器810输出的信号810_out以及从输出缓存器830输出的信号do。

181.控制缓存器821由频率clk的上升边缘来触发,控制缓存器822由频率clk的下降边缘来触发。

182.根据内部测试模块所提供的信号844,从控制缓存器421输出的地址从a1变化至an。当信号eq1变为低电平而信号eq2变为高电平时,只要信号eq1保持在低电平且信号eq2保持在高电平,信号803_out就会变成有效状态且表示地址a1至an。可重写存储器810的地址a1至an在频率clk的每个拍子(beat)处被依序地寻址。

183.当信号eq1变为低电平且信号eq2变为高电平时,信号804_out在外部频率clk的下一个上升边缘处变成有效的及表示在连续的地址a1至an处读取可重写存储器810的内容的命令,并且只要信号eq1保持在低电平且信号eq2保持在高电平,就会保持在有效状态中。

184.在地址a1至an处的可重写存储器810的内容d1至dn在表示可重写存储器810的访问时间的延迟下依序地出现在输出810_out中。

185.然后,数据dl至dn在频率clk的下一个上升边缘时出现在输出缓存器830的输出do处。

186.因此,当外部频率clk的周期pe变成小于可重写存储器810的访问时间时,可重写

存储器810的内容不再出现在可重写存储器810的输出处,并且数据项在频率clk的下一个上升边缘时不再出现在在输出缓存器830的输出do处。

187.图10显示依据本发明的算法的示例。

188.在步骤e100中,控制模块300进入扫描链模式。

189.在步骤e101中,由测试器te根据预定参数来决定外部频率的周期性:开始周期、每次重复时的减少。

190.在步骤e102中,控制模块300产成信号eq1及eq2。信号eq1被设定为低电平,而信号eq2被设定为高电平。这具有将可重写存储器与所有逻辑门及触发器320隔离的效果。

191.在步骤e103中,控制模块300依据参考图4所述的第一实施例等待外部频率clk的两个上升边缘或依据参考图6所述的第二实施例等待外部频率clk的三个上升边缘。

192.在步骤e104中,控制模块300将信号eq1设定为高电平,而将信号eq2设定为低电平。

193.在步骤e105中,控制模块300读取输出缓存器的输出do。

194.在步骤e106中,测试器te检查在输出do处读取的数据项是否等于在可重写存储器的地址add1或ad1处储存的数据项。

195.如果是,则在步骤e107中储存外部频率clk的周期,并且所述方法返回至步骤e101,或者减小外部频率的周期性。

196.如果不是,则所述方法前进至步骤e108,并且可重写存储器的取存时间被认为等于所储存的频率clk的最后周期。

197.附图标记说明

198.200:处理器

199.201:通信总线

200.202:rom存储器

201.203:挥发性存储器

202.205:界面

203.300:控制模块

204.310:用于隔离及测试可重写存储器的模块

205.320:逻辑门及触发器

206.400:多任务器

207.401:多任务器

208.402:多任务器

209.403:多任务器

210.404:多任务器

211.410:可重写存储器

212.420:控制缓存器

213.421:控制缓存器

214.422:控制缓存器

215.430:输出缓存器

216.403_out:信号

217.404_out:信号

218.410_out:信号

219.421_out:信号

220.422_out:信号

221.600:多任务器

222.601:多任务器

223.602:多任务器

224.603:多任务器

225.604:多任务器

226.603_out:信号

227.604_out:信号

228.610_out:信号

229.610:可重写存储器

230.620:控制缓存器

231.621:控制缓存器

232.622:控制缓存器

233.630:输出缓存器

234.640:逆变器

235.800:多任务器

236.801:多任务器

237.802:多任务器

238.803:多任务器

239.804:多任务器

240.810:可重写存储器

241.820:控制缓存器

242.821:控制缓存器

243.822:控制缓存器

244.830:输出缓存器

245.840:内部测试模块

246.803_out:信号

247.804_out:信号

248.810_out:信号

249.821_out:信号

250.822_out:信号

251.842:内部测试模块840的输出

252.844:内部测试模块840的输出

253.846:内部测试模块840的输出

254.850:多任务器

255.!ad1:补码

256.!d1:内容

257.act:信号

258.ad1:地址

259.add1:地址

260.add1:预定地址

261.an:地址

262.ci:集成电路

263.clk:外部频率

264.cp1a:探针

265.cp1b:探针

266.cp2a:探针

267.cp2b:探针

268.d:内容

269.do:信号

270.dut:硅晶圆

271.e100:步骤

272.e101:步骤

273.e102:步骤

274.e103:步骤

275.e104:步骤

276.e105:步骤

277.e106:步骤

278.e107:步骤

279.e108:步骤

280.eq1:信号

281.eq2:信号

282.fon1:信号

283.fon2:信号

284.in:信号

285.otr:信号

286.pe:周期

287.scan_taa:信号

288.sch:信号

289.scmo:信号

290.ta:延迟

291.ta’:延迟

292.te:测试器。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。