1.本发明涉及领域半导体器件领域,尤其涉及一种电力电子半导体器件。

背景技术:

2.为了达到电力变换装置的不断的低消费成本和大容量化,电力电子半导体器件有望成为在电力变换装置中的节能和大容量化起着关键的作用的器件。为了使得通态电压变低即导通电阻变低,使用门极绝缘栅极控制的晶体管即igbt (insulated gate bipolar transistor)器件是一个最佳的选择。由于使用了igbt,能够确保有高的击穿电压和实现快的开关速度。但是这种igbt在开通时候,会有由于电磁干扰 emi(electro

ꢀ‑

magnetic interference)引起的大量噪音。

技术实现要素:

3.为了解决电磁干扰的问题并保证半导体器件的高速开关特性,本技术把肖特基二极管(schottky diode)和快速二极管(fast

‑

recovering diode

ꢀ‑

fred diode)与igbt智能化的集成在一起的先进制造技术。而且,电力半导体器件的基区内有许许多多的驱动载流子从而形成了漂移层,这个漂移层内的浓度和厚度对电力半导体器件的导通电阻特性和雪崩击穿电压有着强烈的影响。但是这种导通电阻特性和雪崩击穿电压特性与漂移层内的浓度和厚度有一定的折衷关系缘故,所以同时满足解决上述两种问题。

4.针对上述技术中存在的不足之处,本发明提供一种电力电子半导体器件,其包括半导体基片,半导体基片上设置有活性区域和结终端区域;活性区域内设置有第一沟槽,活性区域与结终端区域的连接处设置第二沟槽,结终端区域内设置有第三沟槽;第一沟槽内设置有肖特基二极管半导体层;第二沟槽内设置有电场保护环,第三沟槽的内设有导电空间电荷层,第一沟槽、第二沟槽和第三沟槽采用肖特基二极管进行连接。

5.作为优选,第一沟槽与第二沟槽的宽度相同,第三沟槽的宽度大于第一沟槽的宽度。

6.作为优选,位于第一沟槽上侧壁的肖特基二极管半导体层漏出的高度的超过半导体基片的表面。

7.作为优选,半导体基片包括半导体衬底基板和漂移区,漂移区设置在半导体基板的上部,与半导体基板连接为一体式结构,半导体基板上设置有活性区域和结终端区域。

8.作为优选,半导体基片上还设置有场板,场板包括阳极金属电极场板和阴极金属电极场板;阳极金属电极场板和阴极金属电极场板分别设置在半导体基片的上下两侧。

9.作为优选,阴极金属电极场板与半导体衬底基板固定相连,阳极金属电极场板与漂移区通过绝缘膜相连接。

10.作为优选,位于第一沟槽上端两侧的绝缘膜与第一沟槽的边缘位置设有间隙,间隙靠近第一沟槽,位于第一沟槽内的肖特基二极管半导体层沿着第一沟槽的边缘进行延伸

并且对间隙进行填补,形成肖特基结。

11.作为优选,第一沟槽、第二沟槽和第三沟槽内还设置有绝缘膜绝缘膜为二氧化硅绝缘膜。

12.作为优选,第二沟槽设置有多个,多个第二沟槽环绕活性区域设置,多个第二沟槽之间的间隔是固定的,按照相同的环间距进行设置。

13.作为优选,结终端区域上设置有导电空间电荷层,导电空间电荷层包括第一导电空间电荷层和第二导电空间电荷层,第一导电空间电荷层设置在第三沟槽内,第二导电空间电荷层位于结终端区域的边缘位置,第一导电空间电荷层与第二导电空间电荷层处于相同的高度上。

14.本发明的有益效果是:本发明采用了肖特基二极管半导体层,活性区域以及pn结结终端区域的交界面形成保护环与pn结结终端区域侧面的残留导电空间电荷层通过一个桥连接成一个电回路,以阻止由于漏电电流源与部分电压平衡后使得半导体内部电场降低,从而使得雪崩击穿电压得到提高。据此,提高了电力电子半导体器件的雪崩击穿电压;其次,制作肖特基二极管的半导体层的工艺时,过度的化学蚀刻会造成该肖特基二极管的半导体层内的沟槽侧面露出部分的比较多,从而使得肖特基二极管的结合面积增大。这样一来,就可以改善电力半导体器件的电流能力。

附图说明

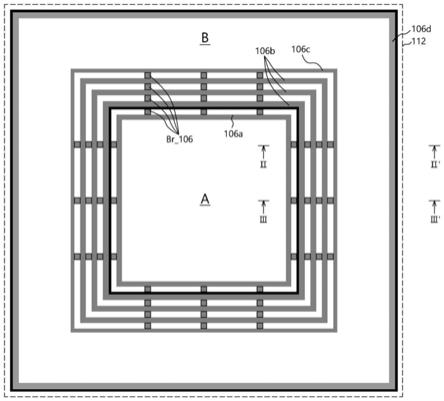

15.图1为本发明的电力电子半导体器件平面图;图2是图1沿着ii

‑

ii线截面的截面图;图3是图1沿iii

‑

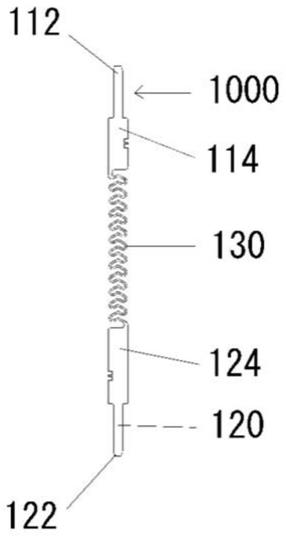

iii线截面的截面图。

16.主要元件符号说明如下:100.半导体基片 102.漂移区 104.绝缘膜 106a.肖特基二极管半导体层106b.电压保护环 106c.第一导电空间电荷层 106d.第二导电空间电荷层112. 阳极金属电极场板 114. 阴极金属电极场板a. 活性区域 b. 结终端区域 br_106. 肖特基二极管br_t. 桥式沟槽t1:第一沟槽 t2 .第二沟槽 t3.第三沟槽j. 肖特基结。

具体实施方式

17.为了更清楚地表述本发明,下面结合附图对本发明作进一步地描述。

18.请参阅图1至图3,本发明公开了一种电力电子半导体器件,包括半导体基片,半导体基片上设置有活性区域和结终端区域;活性区域内设置有第一沟槽,活性区域与结终端区域的连接处设置第二沟槽,结终端区域内设置有第三沟槽;第一沟槽内设置有肖特基二极管半导体层;第二沟槽内设置有电场保护环,第三沟槽的内设有导电空间电荷层,第一沟槽、第二沟槽和第三沟槽采用肖特基二极管进行连接。第一沟槽与第二沟槽的宽度相同,第三沟槽的宽度大于第一沟槽的宽度。

19.位于第一沟槽上侧壁的肖特基二极管半导体层漏出的高度的超过半导体基片的表面。半导体基片包括半导体衬底基板和漂移区,漂移区设置在半导体基板的上部,与半导

体基板连接为一体式结构。

20.在本实施例中,半导体基板上设置有活性区域和结终端区域,导电的活性区域为a,pn结的结终端为b,导电区域的中间部分为带沟槽门极的mos管、具有沟槽门极的igbt器件和带沟槽的肖特基二极管中的一种,活性区域内设有第一沟槽;结终端区域位于活性区域旁,活性区域与结终端区域的相交部分设置有第二沟槽,将第二沟槽填充导电物质后形成电压保护环,电压保护环环绕在活性区域的外侧设置,电压保护环设置有多个,多个电压保护环之间的间隔是固定的,按照一定的环间距进行排列。

21.同时在第三沟槽填充导电物质,同时在结终端区域的外圈设置进行填充,从而形成导电空间电荷层,两个导电空间电荷层是导电的空间电荷区出现的位置,肖特基二极管将三个电压保护环与一个导电空间电荷层进行相连,从而形成一个电气通道(br_106),即一个桥,在具体实施过程中,导电空间电荷层共设置有两个,包括第一导电空间电荷层106c和第二导电空间电荷层106d,第一导电空间电荷层和第二导电空间电荷层分别设置在结终端区域的外圈,更为具体的是,第一导电空间电荷层和第二导电空间电荷层之间的距离是200um。

22.活性区域和结终端区域的上端位置设有场板,且场板上设置有与第一沟槽相适配的凸起,场板覆盖在整个活性区域和结终端区域所形成的区域;场板与活性区域之间还设有绝缘膜,在实际的使用过程中,场板的设计厚度为50um。

23.半导体基片包括半导体衬底基板和漂移区,漂移区设置在半导体基板的上部,与半导体基板连接为一体式结构,半导体基板上设置有活性区域和结终端区域。半导体基片上还设置有场板,场板包括阳极金属电极场板和阴极金属电极场板;阳极金属电极场板和阴极金属电极场板分别设置在半导体基片的上下两侧。阴极金属电极场板与半导体衬底基板固定相连,阳极金属电极场板与漂移区通过绝缘膜相连接;第一沟槽、第二沟槽和第三沟槽内均设置有绝缘膜。

24.在电力电子半导体器件的生产过程中,选择一个半导体衬底基板来构建活性区和结终端区,半导体衬底基板是含有n型杂质的一种导电物质的硅晶圆片;首先在半导体衬底基上用离子注入的方法注入一种n型的低浓度的杂质,然后再在这个低浓度的半导体衬底基上注入高浓度的杂质形成一个漂移区,再对活性区和结终端区域上的漂移区进行蚀刻,从而在活性区内形成第一沟槽;在活性区和结终端的交接区域形成第二沟槽,第二沟槽设置有多个且均匀分布,在结终端上形成第三沟槽,且第一沟槽与第二沟槽的宽度保持一致,第三沟槽的宽度大于第一沟槽的宽度;第一沟槽、第二沟槽和第三沟槽采用桥式沟槽(bridgetrench)进行连接,对于在具体的实施过程中,三个沟槽都可通过现有的光刻技术或者蚀刻工艺从而实现;对于桥式沟槽(br_t)而言,由于第一沟槽、第二沟槽和第三均为垂直方向,方向都完全一致,桥式沟槽与内置的三个沟槽可以同时做成的,所以制作桥式沟槽并不需要附加的工艺过程。其次,桥式沟槽(br_t)与内置的三个沟槽是同时形成并连通的原因,所以把桥式沟槽(br_t)与内置的三个沟槽从同一侧面进行观察时,只能看到一个沟槽。

25.绝缘膜的上部所具有的半导体基板设有导电层,导电层是在活性区域内形成大功率mos管和igbt器件的门极,在具体实施应用过程中,导电层含有高浓度的杂质的多晶硅来形成,本技术将导电层作为半导体膜,在实际生产过程中,对于igbt器件的门极来说,导电

层的厚度具有一定的要求,因此可采用蒸发方法来做,对于第一沟槽、第二沟槽与桥式沟槽来说,由于尺寸较小,因此可采用填充的方式来进行处理;而对于第三沟槽,具有较大的尺寸,因此也采用蒸发工艺来处理;此外,对于第一沟槽和第二沟槽与桥式沟槽的导电层内部因为没有微小的空洞存在,所以可以用最先进的稳定的蒸发工艺方式来进行加厚和填充,比如采用低压化学气相蒸发工艺或者等离子增强型化学气相蒸发工艺技术来实现加厚和填充。

26.在实际生产过程中,肖特基二极管,保护环以及桥式沟槽可以采用光刻刻蚀的方法来形成。对于门极可以在活性区域内部用局部掩膜板的光刻来实现。对于肖特基二极管,保护环以及桥式沟槽可以采用各向异性的开孔蚀刻或者各向异性的背腐蚀工艺来完成,在第一沟槽区域内部,第二沟槽内部和桥式沟槽内部各自蚀刻进行。用同样的各向异性蚀刻,对于第三沟槽的侧壁的导电空间电荷区的残留部分也能用这样的工艺完成;对于肖特基二极管,保护环以及第三沟槽的侧壁残留的导电空间电荷区,用桥式沟槽就做部分的电气回路的连接。

27.为了形成肖特基二极管,保护环以及的导电空间电荷区,采用各向异性的开孔蚀刻或者各向异性的背腐蚀工艺时,可以实现导电层的过腐蚀。对于肖特基二极管,保护环以及导电空间电荷区的各层之间的绝缘膜在半导体基板的上部形成, 对于第一沟槽内部的肖特基二极管和它周边增加的裸露部分,可以用定向刻蚀来完成。

28.通过对绝缘膜上部和半导体基板背面的金属蒸发工艺,制作得到阳极金属电极场板和阴极的金属场板。金属电极场板的一部分作为肖特基二极管半导体层的接触层即实现了肖特基的半导体结。与第一沟槽的深度相比,肖特基半导体层的厚度相对的薄一些。由此,肖特基结是由肖特基二极管半导体层、第一沟槽的侧面和第一沟槽的上面这三部分形成的,所以肖特基二极管的结合面积增加;该肖特基二极管的电流密度和电流驱动能力就由此而改善。再则,通过场板可以把场环的和导电空间电荷层的电气信号引出,使得肖特基二极管的漏电电流发生减小,这有利于肖特基二极管的雪崩击穿电压的提高。

29.一般来说,为了防止在结终端区域形成的场保护环的电场强度过大问题,传统设计的场保护环与必然产生的导电空间电荷层的导电性会形成以浮桥形态存在的漏电电流源的。由此,这个问题对电力电子半导体器件的雪崩击穿电压的提高有着很大的影响。本技术在肖特基二极管半导体层, 场保护环和导电空间电荷层之间的漂移区内形成一个桥式沟槽。通过这个桥式沟槽和场板来提供一个漏电电流源并把电信号通过场保护环和导电空间电荷层予以导通;其结果就从根本上消除了漏电电流的问题。

30.本发明的优势在于:1)本发明通过在肖特基二极管半导体层的工艺时的过度刻蚀技术,使得沟槽侧墙的肖特基二极管半导体层漏出部分变的更多,由此增加了肖特基结的结合面积,最终的效果使得半导体器件的电流驱动能力获得了非常大的改善。

31.2)本发明在肖特基二极管半导体层,活性区域以及结终端区的交接面形成的场保护环和结终端侧墙的残留的空间电荷区通过一个桥设计进行电气性的联通,从而形成一个电流源把漏电流彻底泄放掉。消除了漏电电流对电力电子器件的雪崩击穿电压的影响,从而大大提高了电力电子半导体器件的雪崩击穿电压。

32.以上公开的仅为本发明的几个具体实施例,但是本发明并非局限于此,任何本领

域的技术人员能思之的变化都应落入本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。