1.本

技术实现要素:

是有关于一种半导体封装件。

背景技术:

2.双芯片封装(dual-die packaging)技术被广泛地应用于将两个集成电路芯片封装于单一封装模块中,使得单一封装模块能够提供双倍的功能或数据存储容量。如动态随机存取存储(dynamic random access memory,dram)芯片的存储芯片通常以此方式封装,以允许单一封装模块提供双倍的功能或数据存储容量。近年来,各种双芯片封装技术已被开发及利用于半导体产业中。

3.一般而言,dram芯片的运作通常需要接地源及多个电源,且金线及重分布层常被用以在电源/接地源与dram芯片之间传输电流。然而,当dram芯片于操作过程中(例如,高频率操作过程中)需要瞬间大电流时,在高频率操作下的金线会形成大的电阻,从而限制瞬间大电流的传输。如此一来,在dram芯片中将产生瞬间电压降,并最终导致芯片的误操作。因此,期望开发出一种具有改善的功能性的半导体装置以克服上述问题。

发明内容

4.本发明目的是有关于一种半导体封装件,其能够避免引起半导体封装件中的瞬间电压降的大电阻,且当即使需要瞬间大电流时,来自外部电子装置的电源供给仍可被稳定地提供至半导体封装件中。

5.根据本发明一些实施方式,半导体封装件可包括第一半导体晶圆、第一基板、第二半导体晶圆以及第二基板。第一基板设置于第一半导体晶圆上。第一基板包括多个第一金属线层彼此垂直地间隔开,且每一个第一金属线层电性连接至接地源以及不同类型的电源的其中一个。第二半导体晶圆设置于第一基板上。第二基板设置于第二半导体晶圆上。第二基板包括多个第二金属线层彼此垂直地间隔开,且每一个第二金属线层电性连接至接地源以及不同类型的电源的其中一个。

6.在本发明一些实施方式中,半导体封装件还包括多个导线,将第一半导体晶圆连接至第一金属线层。

7.在本发明一些实施方式中,半导体封装件还包括多个导线,将第二半导体晶圆连接至第二金属线层。

8.在本发明一些实施方式中,半导体封装件还包括多个导线,分别将多个第一金属线层连接至接地源及不同类型的电源的其中一个。

9.在本发明一些实施方式中,半导体封装件还包括多个导线,分别将多个第二金属线层连接至接地源及不同类型的电源的其中一个。

10.在本发明一些实施方式中,半导体封装件还包括多个第一重分布层,垂直地设置于第一半导体晶圆与第一基板之间。

11.在本发明一些实施方式中,半导体封装件还包括至少一个导线,将第一重分布层

的至少一个连接至信号源。

12.在本发明一些实施方式中,半导体封装件还包括多个导电垫,水平地相邻于第一重分布层,其中导电垫的至少一个接触第一重分布层的至少一个。

13.在本发明一些实施方式中,半导体封装件还包括多个第二重分布层,垂直地设置于第二半导体晶圆与第二基板之间。

14.在本发明一些实施方式中,半导体封装件还包括至少一个导线,将第二重分布层的至少一个连接至信号源。

15.在本发明一些实施方式中,半导体封装件还包括多个导电垫,水平地相邻于第二重分布层,其中导电垫的至少一个接触第二重分布层的至少一个。

16.在本发明一些实施方式中,半导体封装件还包括多个导通结构,嵌入至第一基板中,且垂直地连接第一金属线层的其中两个。

17.在本发明一些实施方式中,半导体封装件还包括多个导通结构,嵌入至第二基板中,且垂直地连接第二金属线层的其中两个。

18.在本发明一些实施方式中,半导体封装件还包括第一粘胶层,垂直地设置于第一半导体晶圆与第一基板之间。

19.在本发明一些实施方式中,半导体封装件还包括第二粘胶层,垂直地设置于第二半导体晶圆与第二基板之间。

20.在本发明一些实施方式中,半导体封装件还包括第三粘胶层,垂直地设置于第二半导体晶圆与第一基板之间。

21.在本发明一些实施方式中,半导体封装件还包括第三基板,设置于第一半导体晶圆背对第一基板的表面。

22.在本发明一些实施方式中,半导体封装件还包括多个焊球,安装于第三基板背对第一半导体晶圆的表面。

23.在本发明一些实施方式中,半导体封装件还包括成型模料,封装第一半导体晶圆、第一基板、第二半导体晶圆以及第二基板。

24.在本发明一些实施方式中,成型模料穿过第一基板及第二基板。

25.根据本发明上述实施方式,由于包括第一金属线层的第一基板设置在第一半导体晶圆上,因此第一半导体晶圆可通过第一基板电性连接至接地源及多个电源。类似而言,由于包括第二金属线层的第二基板设置在第二半导体晶圆上,因此第二半导体晶圆可通过第二基板电性连接至接地源及多个电源。如此一来,可以避免引起半导体封装件中的瞬间电压降的大电阻,且当即使需要瞬间大电流时,来自外部电子装置的电源供给仍可被稳定地提供至半导体封装件中。借此,即使在需要瞬间大电流的情形下,半导体封装件仍可良好地执行其功能。

附图说明

26.为让本发明的上述和其他目的、特征、优点与实施例能更明显易懂,现结合附图说明如下:

27.图1绘示根据本发明一些实施方式的半导体封装件的俯视示意图;

28.图2绘示根据本发明一些实施方式的半导体封装件沿线段2-2'的剖面示意图;

29.图3绘示根据本发明一些实施方式的半导体封装件沿线段3-3'的剖面示意图;

30.图4绘示根据本发明一些实施方式的半导体封装件沿线段4-4'的剖面示意图;

31.图5绘示根据本发明一些实施方式的半导体封装件沿线段5-5'的剖面示意图;以及

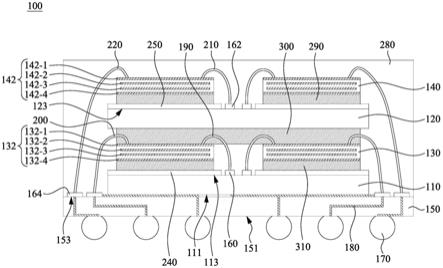

32.图6绘示根据本发明一些实施方式的半导体封装件沿线段6-6'的剖面示意图。

33.主要附图标记说明:

34.100-半导体封装件;110-第一半导体晶圆;111-表面;113-表面;120-第二半导体晶圆;123-表面;130-第一基板;132,132-1,132-2,132-3,132-4-第一金属线层;140-第二基板;142,142-1,142-2,142-3,142-4-第二金属线层;150-第三基板;151-表面;153-表面;160-第一导电垫;162-第二导电垫;164-第三导电垫;170-焊球;180-互连结构;190-第一导线;200-第二导线;210-第三导线;220-第四导线;230-导通结构;240-第一重分布层;250-第二重分布层;260-第五导线;270-第六导线;280-成型模料;290-第二粘胶层;300-第三粘胶层;310-第一粘胶层;2-2',3-3',4-4',5-5',6-6'-线段。

具体实施方式

35.以下将以附图公开本发明的多个实施方式,为明确说明起见,许多实务上的细节将在以下叙述中一并说明。然而,应了解到,这些实务上的细节不应用以限制本发明。也就是说,在本发明部分实施方式中,这些实务上的细节是非必要的,因此不应用以限制本发明。此外,为简化附图起见,一些公知惯用的结构与元件在附图中将以简单示意的方式绘示。另外,为了便于读者观看,附图中各元件的尺寸并非依实际比例绘示。

36.图1绘示根据本发明一些实施方式的半导体封装件100的俯视示意图。

37.图2绘示根据本发明一些实施方式的半导体封装件100沿线段2-2'的剖面示意图。请参阅图1及图2,半导体封装件100包括第一半导体晶圆110、第二半导体晶圆120、第一基板130及第二基板140。第一基板130设置于第一半导体晶圆110上方,第二半导体晶圆120设置于第一基板130上方,且第二基板140设置于第二半导体晶圆120上方。换句话说,第一基板130、第二半导体晶圆120以及第二基板140依序堆叠于第一半导体晶圆110上。

38.第一基板130包括多个第一金属线层132(例如具有横向延伸的金属线的层)垂直地堆叠并彼此间隔开(例如通过第一半导体基板中的介电材料间隔开),且每个第一金属线层132通过第一基板130中的一个或多个垂直延伸的导通结构电性连接至以下其中一个:接地源及多个不同类型的电源(如图3至图6所示)。举例而言,第一基板130包括第一金属线层132-1、132-2、132-3及132-4,第一金属线层132-1电性连接接地源,第一金属线层132-2电性连接vdd电源,第一金属线层132-3电性连接vdd2电源,且第一金属线层132-4电性连接vddq电源。然而,第一金属线层132-1、132-2、132-3及132-4与接地源/电源(亦即接地源以及vdd、vdd2与vddq电源)之间的连接关系不限于此,且可根据设计者的需求设置其他连接关系。

39.第二基板140包括多个第二金属线层142垂直地堆叠并彼此间隔开,且每个第二金属线层142通过第二基板140中的一个或多个垂直延伸的导通结构电性连接至以下其中一个:接地源以及多个不同类型的电源(如图3至图6所示)。举例而言,第二基板140包括第二金属线层142-1、142-2、142-3及142-4,第二金属线层142-1电性连接至接地源,第二金属线

层142-2电性连接至vdd电源,第二金属线层142-3电性连接至vdd2电源,第二金属线层142-4电性连接至vddq电源。然而,第二金属线层142-1、142-2、142-3及142-4与接地源/电源(亦即接地源以及vdd、vdd2与vddq电源)之间的连接关系不限于此,且可根据设计者的需求设置其他连接关系。

40.应了解到,为了清楚起见及方便说明,在以下叙述中,第一金属线层132-1及第二金属线层142-1被视为电性连接至接地源,第一金属线层132-2及第二金属线层142-2被视为电性连接至vdd电源,第一金属线层132-3及第二金属线层142-3被视为电性连接至vdd2电源,且第一金属线层132-4及第二金属线层142-4被视为电性连接至vddq电源。

41.在一些实施方式中,半导体封装件100还包括第三基板150,设置在第一半导体晶圆110背对第一基板130的表面111。在一些实施方式中,第一基板130及第二基板140各自于第三基板150的垂直投影面积小于第一半导体晶圆110及第二半导体晶圆120各自于第三基板150的垂直投影面积。在一些实施方式中,第一基板130于第三基板150的垂直投影面积等于第二基板140于第三基板150的垂直投影面积,且第一半导体晶圆110于第三基板150的垂直投影面积等于第二半导体晶圆120于第三基板150的垂直投影面积。

42.在一些实施方式中,半导体封装件100还包括多个第一导电垫160、多个第二导电垫162及多个第三导电垫164。第一导电垫160设置于第一半导体晶圆110面对第一基板130的表面113,第二导电垫162设置于第二半导体晶圆120面对第二基板140的表面,且第三导电垫164设置于第三基板150面对第一半导体晶圆110的表面153。第一导电垫160、第二导电垫162以及第三导电垫164配置以用于导线的接合。

43.在一些实施方式中,半导体封装件100还包括多个焊球170,安装在第三基板150背对第一半导体晶圆110的表面151。换句话说,第三导电垫164与焊球170设置在第三基板150的相对表面。在一些实施方式中,半导体封装件100还包括在第三基板150中的多个互连结构180(例如金属线及金属导通结构),使得第一半导体晶圆110及第二半导体晶圆120可进一步电性连接至外部接地源及电源,此将在下文中进行更详细的说明。

44.在一些实施方式中,半导体封装件100还包括多个第一导线190及多个第二导线200。第一导线190将第一半导体晶圆110连接至第一基板130,且第二导线200将第一基板130连接至第三基板150,使得第一半导体晶圆110可进一步通过互连结构180及焊球170而电性连接至接地源及电源。在一些实施方式中,半导体封装件100还包括多个第三导线210及多个第四导线220。第三导线210将第二半导体晶圆120连接至第二基板140,且第四导线220将第二基板140连接至第三基板150,使得第二半导体晶圆120可进一步通过互连结构180及焊球170而电性连接至接地源及电源。在以下叙述中,将通过图2至图5进一步说明上述电性连接关系。

45.如图1及图2所示,至少一个第一导线190将第一半导体晶圆110连接至第一基板130的第一金属线层132-1,且至少一个第二导线200将第一基板130的第一金属线层132-1连接至第三基板150,使得第一半导体晶圆110可进一步电性连接至接地源。类似地,至少一个第三导线210将第二半导体晶圆120连接至第二基板140的第二金属线层142-1,且至少一个第四导线220将第二金属线层142-1连接至第三基板150,使得第二半导体晶圆120可进一步电性连接至接地源。如此一来,通过第一金属线层132-1以及第二金属线层142-1的配置,第一半导体晶圆110及第二半导体晶圆120可电性连接至接地源。

46.在一些实施方式中,半导体封装件100还包括第一粘胶层310、第二粘胶层290及第三粘胶层300。第一粘胶层310垂直地(在垂直方向上)设置于第一半导体晶圆110与第一基板130之间,第二粘胶层290垂直地设置于第二半导体晶圆120与第二基板140之间,且第三粘胶层300垂直地设置于第一基板130与第二半导体晶圆120之间。在一些实施方式中,第一粘胶层310于第三基板150的垂直投影完全地重叠于第二粘胶层290于第三基板150的垂直投影。在一些实施方式中,第三粘胶层300于第三基板150的垂直投影面积大于第一粘胶层310于第三基板150的垂直投影面积。

47.图3绘示根据本发明一些实施方式的半导体封装件100沿线段3-3'的剖面示意图。如图1及图3所示,半导体封装件100还包括嵌入第一基板130及第二基板140中的多个导通结构230。至少一个第一导线190通过至少一个导通结构230将第一半导体晶圆110连接至第一基板130的第一金属线层132-2,且至少一个第二导线200通过至少一个导通结构230将第一基板130的第一金属线层132-2连接至第三基板150,使得第一半导体晶圆110可进一步电连接至vdd电源。类似而言,至少一个第三导线210通过至少一个导通结构230将第二半导体晶圆120连接至第二基板140的第二金属线层142-2,且至少一个第四导线220通过至少一个导通结构230将第二基板140的第二金属线层142-2连接至第三基板150,使得第二半导体晶圆120可进一步电连接至vdd电源。借此,通过第一金属线层132-2及第二金属线层142-2的配置,第一半导体晶圆110及第二半导体晶圆120可电性连接至vdd电源。

48.图4绘示根据本发明一些实施方式的半导体封装件100沿线段4-4'的剖面示意图。如图1及图4所示,至少一个第一导线190通过至少一个导通结构230将第一半导体晶圆110连接至第一基板130的第一金属线层132-3,且至少一个第二导线200通过至少一个导通结构230将第一基板130的第一金属线层132-3连接至第三基板150,使得第一半导体晶圆110可进一步电连接至vdd2电源。类似地,至少一个第三导线210至少一个导通结构230将第二半导体晶圆120连接至第二基板140的第二金属线层142-3,且至少一个第四导线220通过至少一个导通结构230将第二基板140的第二金属线层142-3连接至第三基板150,使得第二半导体晶圆120可进一步电连接至vdd2电源。借此,通过第一金属线层132-3及第二金属线层142-3的配置,第一半导体晶圆110及第二半导体晶圆120可电性连接至vdd2电源。

49.图5绘示根据本发明一些实施方式的半导体封装件100沿线段5-5'的剖面示意图。如图1及图5所示,至少一个第一导线190通过至少一个导通结构230将第一半导体晶圆110连接至第一基板130的第一金属线层132-4,且至少一个第二导线200通过至少一个导通结构230将第一基板130的第一金属线层132-4连接至第三基板150,使得第一半导体晶圆110可进一步电连接至vddq电源。类似地,至少一个第三导线210通过至少一个导通结构230将第二半导体晶圆120连接至第二基板140的第二金属线层142-4,且至少一个第四导线220通过至少一个导通结构230将第二基板140的第二金属线层142-4连接至第三基板150,使得第二半导体晶圆120可进一步电连接至vddq电源。借此,通过第一金属线层132-4及第二金属线层142-4的配置,第一半导体晶圆110及第二半导体晶圆120可电性连接至vddq电源。

50.应了解到,虽未绘示在各附图中,但第一半导体晶圆110以及第二半导体晶圆120可在单一剖面图中电连接至不同类型的接地源/电源。举例而言,在单一剖面图中,第一半导体晶圆110可电性连接至接地源,而第二半导体晶圆120可电性连接至vdd电源。又举例而言,在单一剖面图中,第一半导体晶圆110可电性连接至vdd电源,而第二半导体晶圆120可

电性连接至vddq电源。

51.由于第一半导体晶圆110通过第一基板130的第一金属线层132-1、132-2、132-3及132-4电性连接至接地源及电源,且第二半导体晶圆120通过第二基板140的第二金属线层142-1、142-2、142-3及142-4电性连接至接地源及电源,因此可避免引起半导体封装件100中的瞬间电压降的大电阻,使得来自外部电子装置的电源供给仍可被稳定地提供至半导体封装件100中。

52.图6绘示根据本发明一些实施方式的半导体封装件100沿线段6-6'的剖面示意图。如图1及图6所示,半导体封装件100还包括多个第一重分布层240及多个第二重分布层250。第一重分布层240在第一半导体晶圆110的表面113,并垂直地位于第一半导体晶圆110与第一基板130之间。第二重分布层250位于第二半导体晶圆120的表面123,并垂直地位于第二半导体晶圆120与第二基板140之间。在一些实施方式中,部分的第一重分布层240及部分的第二重分布层250分别由第一基板130及第二基板140裸露。

53.在一些实施方式中,半导体封装件100还包括至少一个第五导线260以及至少一个第六导线270。第五导线260可将至少一个第一重分布层240连接至第三基板150,使得第一半导体晶圆110得以电性连接至外部信号源。第六导线270将至少一个第二重分布层250连接至第三基板150,使得第二半导体晶圆120得以电性连接至信号源。如此一来,通过第一重分布层240、第二重分布层250、第五导线260及第六导线270的配置,第一半导体晶圆110及第二半导体晶圆120可电性连接至信号源。

54.如图1至图6所示,如前所述,半导体封装件100包括第一导电垫160、第二导电垫162、第一重分布层240及第二重分布层250。在一些实施方式中,第一导电垫160水平地相邻于第一重分布层240,且第二导电垫162水平地相邻于第二重分布层250。如图1至图5所示,连接至第一基板130及第二基板140的第一导电垫160及第二导电垫162分别与第一重分布层240及第二重分布层250间隔开。如图6所示,未连接至第一基板130及第二基板140的第一导电垫160及第二导电垫162分别与第一重分布层240及第二重分布层250接触。

55.在一些实施方式中,半导体封装件100还包括成型模料280,配置以封装第一半导体晶圆110、第一基板130、第二半导体晶圆120以及第二基板140。成型模料280用以使半导体封装件100中的元件不被过度暴露。在一些实施方式中,成型模料280进一步穿透第一基板130及第二基板140。

56.根据本发明上述实施方式,半导体封装件通过第一及第二基板电性连接至接地源及电源,并通过第一及第二重新分布层电性连接至信号源。如此一来,可以避免引起半导体封装件中的瞬间电压降的大电阻,且即使当需要瞬间大电流时,来自外部电子装置的电源供给仍可被稳定地提供至半导体封装件中。借此,即使在需要瞬间大电流的情形下,半导体封装件仍可良好地执行其功能。

57.虽然本发明已以实施方式公开如上,然其并非用以限定本发明,任何所属领域的技术人员,在不脱离本发明的精神和范围内,当可作各种的更动与润饰,因此本发明的保护范围当视权利要求所界定的为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。